# INTERNATIONAL STANDARD

ISO 22896

> First edition 2006-11-15

# Road vehicles — Deployment and sensor bus for occupant safety systems

Véhicules routiers — Bus de déploiement et de capteurs pour les systèmes de sécurité des occupants

Reference number ISO 22896:2006(E)

## PDF disclaimer

This PDF file may contain embedded typefaces. In accordance with Adobe's licensing policy, this file may be printed or viewed but shall not be edited unless the typefaces which are embedded are licensed to and installed on the computer performing the editing. In downloading this file, parties accept therein the responsibility of not infringing Adobe's licensing policy. The ISO Central Secretariat accepts no liability in this area.

Adobe is a trademark of Adobe Systems Incorporated.

Details of the software products used to create this PDF file can be found in the General Info relative to the file; the PDF-creation parameters were optimized for printing. Every care has been taken to ensure that the file is suitable for use by ISO member bodies. In the unlikely event that a problem relating to it is found, please inform the Central Secretariat at the address given below

#### © ISO 2006

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm, without permission in writing from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Case postale 56 • CH-1211 Geneva 20 Tel. + 41 22 749 01 11 Fax + 41 22 749 09 47 E-mail copyright@iso.org Web www.iso.org

Published in Switzerland

# **Contents** Page

| Forewo                                      | ord                                                                                                                                                          | İν                           |

|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| 1                                           | Scope                                                                                                                                                        | . 1                          |

| 2                                           | Terms and definitions                                                                                                                                        | . 1                          |

| 3                                           | Abbreviations                                                                                                                                                | . 3                          |

| 4                                           | General                                                                                                                                                      | . 4                          |

| 5<br>5.1<br>5.2<br>5.3<br>5.4               | System architecture                                                                                                                                          | . 5<br>. 5<br>. 5            |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Physical Layer  Bus medium  Bus topology  Bus load  Bus signals  Bit coding  Fault tolerance  Use of analogue safing on a deployment bus                     | . 6<br>. 8<br>10<br>12<br>15 |

| 6.8<br>7<br>7.1<br>7.2<br>7.3<br>7.4        | Bus signal parameters  Data Link Layer  Bus Idle  Addresses  Message frames  Bit fields within a frame                                                       | 22<br>22<br>22<br>24         |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5        | Application Layer  General  Common D-Frame commands  Memory layout of slaves  Application Layer for deployable devices  Application Layer for sensor devices | 35<br>35<br>36<br>37<br>42   |

| Annex                                       | A (informative) In-car address programming for daisy-chain systems                                                                                           | 50                           |

| Annex                                       | B (informative) Guideline for definition of deviations from standard parameters                                                                              | 51                           |

| Annex                                       | C (informative) Rationale of functionality                                                                                                                   | 52                           |

| Annex                                       | D (informative) Latency time analysis for interrupts from smart sensors                                                                                      | 53                           |

| Annex                                       | E (informative) CRC examples                                                                                                                                 | 56                           |

| Annex                                       | F (informative) Deployable devices                                                                                                                           | 57                           |

| Annex                                       | G (informative) Slave manufacturer identification codes                                                                                                      | 60                           |

## **Foreword**

ISO (the International Organization for Standardization) is a worldwide federation of national standards bodies (ISO member bodies). The work of preparing International Standards is normally carried out through ISO technical committees. Each member body interested in a subject for which a technical committee has been established has the right to be represented on that committee. International organizations, governmental and non-governmental, in liaison with ISO, also take part in the work. ISO collaborates closely with the International Electrotechnical Commission (IEC) on all matters of electrotechnical standardization.

International Standards are drafted in accordance with the rules given in the ISO/IEC Directives, Part 2.

The main task of technical committees is to prepare International Standards. Draft International Standards adopted by the technical committees are circulated to the member bodies for voting. Publication as an International Standard requires approval by at least 75 % of the member bodies casting a vote.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO shall not be held responsible for identifying any or all such patent rights.

ISO 22896 was prepared by Technical Committee ISO/TC 22, Road vehicles, Subcommittee SC 3, Electrical and electronic equipment.

# Road vehicles — Deployment and sensor bus for occupant safety systems

## 1 Scope

This International Standard is a specification of a serial communications bus protocol for automotive occupant restraint systems. It covers Physical Layer and Data Link Layer and those parts of the Application Layer that are not supplier-specific.

## 2 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

#### 2.1

#### analogue safing

using a special bus level (LSO-level) for confirmation of deploy messages

#### 2.2

## bitmap addressing

method of addressing one or several slaves at a time by assigning each bit of the address field to a different slave

#### 2.3

## bus level

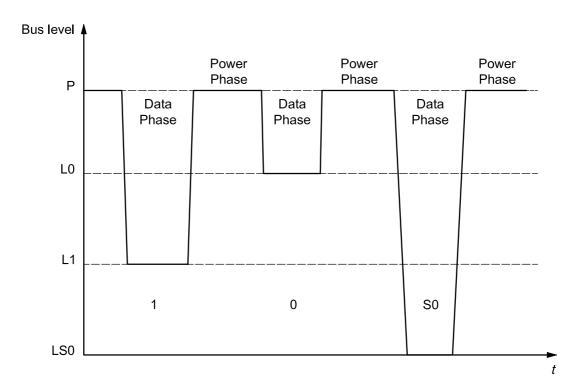

one out of four levels of the differential bus voltage, whereof one forms the *Power Phase* and the other three are used for representation of a data bit during the *Data Phase*

## 2.4

#### command

part of a *D-Frame*, transmitted by the master, defining the purpose of the frame

## 2.5

## **CRC field**

part of a D-Frame or S-Frame

#### 2.6

## data field

part of a *D-Frame*

## 2.7

## **Data Phase**

part of a data bit providing the bit value

## 2.8

## deploy command family

four commands for control of deployable devices

## 2.9

## deployable device

irreversible actuator

#### 2.10

#### **D-Frame**

type of frame primarily used for diagnostic communication and actuation of deployable devices

## 2.11

## differential bus voltage

differential voltage between the two bus wires

#### 2.12

## duty cycle

percentage of a bit time that is assigned to the Power Phase

#### 2.13

#### E-bit

bit in a *D-Frame* indicating an error or a "read" command

#### 2.14

#### half-rate

mode used for sensors that shall not reply in every S-Frame

#### 2.15

## hold-up capacitor

capacitor supplying power to a slave during the Data Phase

#### 2.16

## latency time

worst-case duration between the occurrence of an interrupt requesting event in the sensor and the actual start of an S-Frame polling message

## 2.17

#### LS0-level

bus level indicating an error, a bus interrupt or a "0" with analogue safing

#### 2.18

## L0-level

bus level indicating a "0"

## 2.19

### L1-level

bus level indicating a "1"

#### 2.20

device responsible for communication on the bus and for power distribution over the bus

#### 2.21

# Multi-Sharing

mode used in S-Frames for dynamic assignment of slave data to the first slot

## 2.22

## node

master or slave

## 2.23

## point-to-point addressing

addressing used for communication between the master and one slave

#### 2.24

#### power level

bus level forming the Power Phase

#### 2.25

## **Power Phase**

part of a data bit during which the master transmits the power level

#### 2.26

#### R-bit

reserved bit in *D-frames* for future definition

## 2.27

#### **SEL-bit**

bit used in S-Frames to control slaves configured for half-rate mode

#### 2.28

#### S-Frame

type of frame used by the master to collect dynamic data from slaves periodically

## 2.29

## signal address

address assigned to peculiar signals provided by slaves, used in S-Frames for Multi-Sharing

## 2.30

#### slave

device that is connected to the bus and is not the master

#### 2.31

## slave address bitmap

part of a *D-Frame* in which each bit corresponds to one slave

## 2.32

#### slot

part of an S-Frame assigned to a certain slave to be filled with its data

#### 2.33

## **Slot Length**

determines the number of data bits that a slot consists of

# 2.34

## **Sub-Slot**

sub-section of a slot

## 2.35

## T-bit

first bit of a frame, used to define the frame type (S- or D-Frame)

## 3 Abbreviations

ACU Airbag Control Unit

ASIC Application-Specific Integrated Circuit

CRC Cyclic Redundancy Check

ECU Electronic Control Unit

---..---.

HSD High Side Driver

INT Interrupt

LSB Least Significant Bit

LSD Low Side Driver

MSA Multi-Sharing Address

MSB Most Significant Bit

MTP Multi Time Programmable

NVM Non Volatile Memory

ORC Occupant Restraint Controller

OTP One Time Programmable

RAM Random Access Memory

RCM Restraint Control Module

ROM Read Only Memory

SDM Sensing and Diagnostic Module

SEL Select

SOF Start Of Frame

SSB Slot Start Bit

## 4 General

Automotive occupant restraint systems are controlled by a Sensing and Diagnostic Module (SDM), also called Airbag Control Unit (ACU), Restraint Control Module (RCM) or Occupant Restraint Controller (ORC), which is connected to peripheral devices:

- dynamic sensors with high update rates, e.g. for remote front and side impact sensing;

- static sensors with low update rates, e.g. buckle switches, seat position and occupancy sensors;

- actuators, especially deployable devices, e.g. squibs.

The SDM is also referred to as "master"; the peripheral devices are also referred to as "slaves".

The bus provides a two-wire connection between the SDM and the peripheral devices and supplies power to the slaves. It offers bi-directional communication. The master's bus interface sends energy into the bus, the slave's bus interface extracts power from the bus. The master determines the bus speed and initiates all communication by sending message frames on the bus. Slaves may transmit their data within these frames when requested by the master. Smart dynamic sensors (defined in 5.3) may send an interrupt to the master while the bus is idle or while there is diagnostic communication on the bus. The master's reaction to the interrupt is application specific and typically lets the master stop diagnostic communication and start polling of impact data instead.

The data is usually coded using differential bus voltage. On a bus, where several transmitters are sharing the same wiring, using voltage as the data signal has a significant advantage over current, because it enables the transmitter to verify the data that it sent on the bus. This is the most reliable way to detect bus collisions, e.g. when two sensors are transmitting their data at the same time. For less critical data like diagnostics, reply data from slaves can be coded using current, which allows connection of deployable slaves to the bus via isolation resistors (see 6.6.4.2).

# 5 System architecture

## 5.1 General

The specification covers sensor busses, deployment busses and combined sensor/deployment busses.

The bus shall support 64 slave addresses, of which three shall be reserved for special purposes. The actual number of slaves that can be connected to one bus is limited by the supply current for the slaves and by the pin capacitance of the slaves (see also Clause 6). Bandwidth limits shall also be considered.

NOTE A single slave can incorporate the functionality of several slave addresses.

## 5.2 Deployment bus

The deployment bus shall support deployable devices and static sensors. The bus shall provide point-to-point messages for diagnostic communications between master and slaves. Since the deployment bus shall support fast selective deployment of several deployable devices, the bus shall also provide a special deploy message, which allows individual deployment control of up to 12 devices at a time. There shall be four deploy messages available, each controlling 12 device addresses:

- address range 0b000000 0b001011;

- address range 0b010000 0b011011;

- address range 0b100000 0b101011;

- address range 0b110000 0b111011.

In this way, up to  $4 \times 12 = 48$  deployable devices can be controlled by one bus. The address 0b000000 should not be used as a slave address, because this address shall be the default address of all slaves that have not been programmed yet. See also 7.2.1, 7.3.2 and 7.4.8.

The deployment bus shall provide communication with and without a special "safing" signal, which may be used for additional differentiation between diagnostic communication and actual deploy commands.

#### 5.3 Sensor bus

The sensor bus shall support static and dynamic sensors. There may be two types of dynamic sensors.

- Raw-data sensors send time-critical data periodically to the SDM.

- Smart sensors send time-critical data event-driven only.

Smart sensors can easily coexist with static sensors on the same bus.

NOTE Raw-data sensors usually occupy the bus bandwidth all the time, while smart sensors usually need the full bandwidth only for a short time during an event.

11/11/2017/11/17/17/17/11/11

EXAMPLE In the absence of an event, the master can poll diagnostic data and/or static sensor data from all slaves. When an event occurs, a smart sensor can stop this communication by sending an interrupt to the master and to the other slaves. The master can then assign the full bus bandwidth for exclusive communication of time-critical data from smart sensors to the master.

The number of smart sensors that can be connected to the bus is usually limited by the ratio between the available bandwidth and the latency time requirements for this data transfer. Additional static sensors on the bus do not contribute to the latency time, but they contribute to the physical bus load, which also limits the number of slaves (see Clause 6) on the bus.

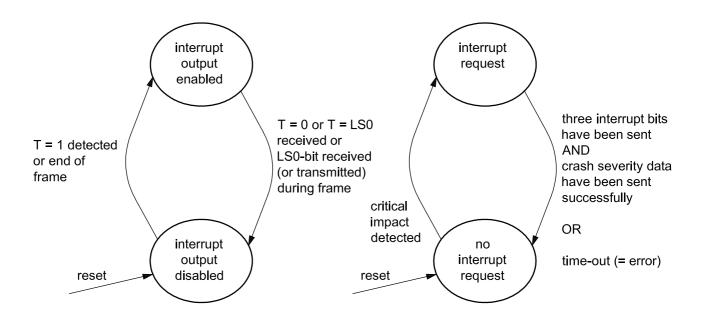

On a sensor bus, the "safing" signal, known from the deployment bus, shall be used for error indication and optionally for the interrupt capability of smart sensors.

Since raw-data sensors usually are not required to send bus interrupts, they may be implemented without this option. Devices (master and slaves) made for raw-data sensor busses should either not have bus interrupt capability or provide a means to disable the bus interrupt function in a reliable way.

## 5.4 Combined sensor and deployment bus

On a combined sensor and deployment bus, all types of slaves that are connected to the same bus would have to share the available bandwidth and the available bus power. This shall be taken into account when designing such a mixed system.

The "safing"-level LS0 shall be used on the one hand for confirmation of deploy messages (i.e. LS0 transmitted by the master), and on the other hand for signalling bus collisions (i.e. LS0 transmitted by a dynamic sensor during an S-Frame) or for interrupting communication (i.e. LS0 transmitted by a smart sensor during a D-Frame). The deployment and sensor bus protocol shall ensure that the relevant function of the LS0-level can be clearly identified by all nodes (see 8.5.4).

# 6 Physical Layer

## 6.1 Bus medium

The bus can use unshielded twisted pair or untwisted cable (see Table 3). The maximum bus length depends on the bus topology (see 6.2).

## 6.2 Bus topology

## 6.2.1 Parallel configuration

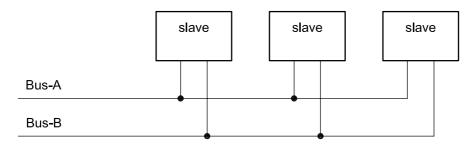

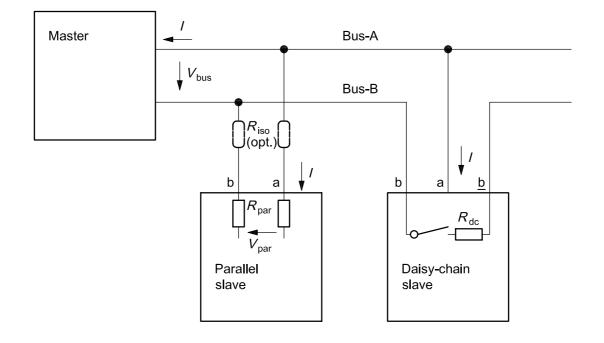

For a parallel bus configuration, each slave shall be directly connected to the two bus wires Bus-A and Bus-B (see Figure 1).

Figure 1 — Parallel connection of slaves to the bus

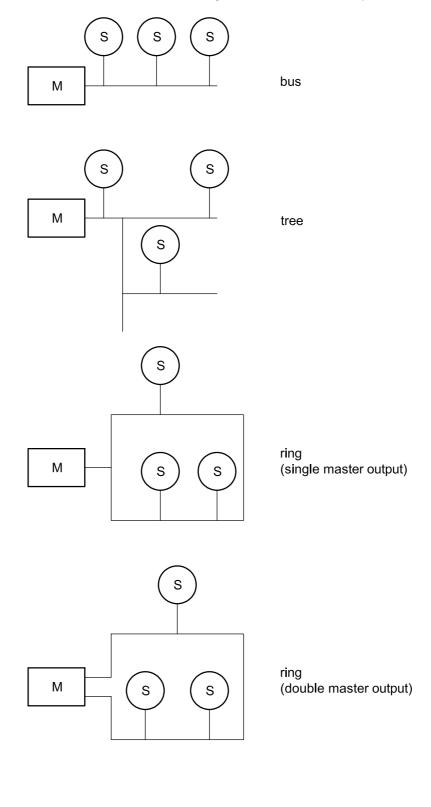

In parallel configuration, the wires may be routed in a bus, tree or ring structure (see Figure 2) or combinations of these. A ring may be implemented either by connecting both ends of the bus cable to a single bus output of the master, or by connecting each end of the cable to a separate output of the master (see also 6.6.3.2).

Parallel squibs can be implemented as polarized or non-polarized devices. For non-polarized devices, it does not matter which pin is connected to which bus wire. Dynamic sensors shall be polarized.

Figure 2 — Bus topologies for parallel configuration

Key

M = masterS = slave

## 6.2.2 Daisy-chain configuration

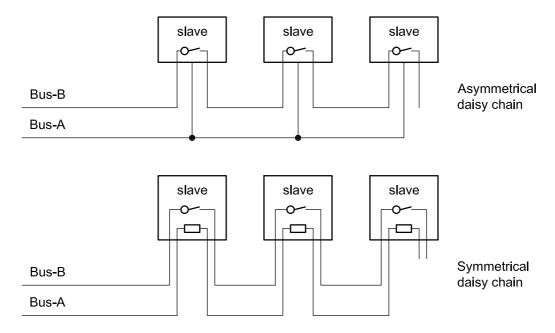

Figure 3 — Daisy-chain connection of slaves to the bus

For an asymmetrical daisy-chain configuration, each slave shall be directly connected to Bus-A. Bus-B shall be routed through a switch in each slave (see Figure 3). These daisy-chain switches shall split the bus into bus sections. Single switches can be opened in order to shut down individual bus sections, which can be used for the following:

- in-car address programming, where slaves are identified by their position in the daisy-chain (see Annex A):

- recovery from Bus-A to Bus-B shorts (see 6.6.4.3), where the faulty bus section is switched off.

For a symmetrical daisy-chain configuration, each slave shall switch Bus-B and insert an element into Bus-A. Ideally, the on-resistance of the switch and the resistance of the element should be identical, in order to keep the balance of the bus voltage behind the daisy-chain slave. Symmetrical daisy-chain configurations should be chosen when the bus is run permanently at high speed.

In a daisy-chain configuration, the wires may be routed in a bus or ring structure (see also 6.6.3.2). Between two daisy-chain slaves, parallel slaves may be connected in a bus or tree structure.

Daisy-chain slaves shall be polarized with respect to the exchange of Bus-A with Bus-B. For operation in a ring, they shall not be polarized with respect to the exchange of switch input with switch output.

### **Bus load**

## 6.3.1 General

The master shall provide enough current to supply the slaves and to drive the signal edges. A slave replying with voltage modulation shall sink enough current to drive the signal edges.

## 6.3.2 Bus capacitance

Each slave, the bus wires and the master itself contribute to the capacitance that is limiting the slope of the signal edges. Since parallel slaves have less capacitance than daisy-chain slaves, a higher number of parallel slaves and/or a longer bus may be admitted.

The total bus capacitance shall be less than the value that master and slaves can drive. The latter can depend on the bus speed (i.e. higher bus speed requires lower capacitance).

#### **EXAMPLE**

Calculations for a deployment bus:

$$C_{c} = 61 \text{ pF/m}$$

$$C_{\rm mstr} = 5 \text{ nF}$$

where

$C_{c}$  is the cable capacity per metre;

$C_{

m mstr}$  is the master pin output capacitance (effective capacitance between Bus-A and Bus-B, when one bus wire is shorted to ground), see Table 1.

NOTE This corresponds for instance to 2,2 nF capacitors (with a relative tolerance of  $\pm$  10 %) connected from Bus-A to GND and from Bus-B to GND at both master outputs driving a ring. If a single output is driving the bus, the capacitor values can be doubled.

Calculation for parallel slave configuration

$$C_{ab} = 250 \text{ pF}$$

$$l_{par} = 40 \text{ m}$$

$$n_{\text{par}} = 16$$

where

$C_{

m ab}$  is the maximal slave capacitance of each slave in parallel configuration;

$l_{\rm par}$  is the maximal permissible cable length in parallel configuration;

$n_{\rm par}$  is the maximal number of slaves that may be connected to the bus in parallel configuration.

The total bus capacitance in parallel configuration,  $C_{\mathrm{totpar'}}$  is calculated as follows:

$$C_{\text{totpar}} = (C_{\text{c}} \times l_{\text{par}}) + (n_{\text{par}} \times C_{\text{ab}}) + C_{\text{mstr}}$$

$$C_{\text{totpar}} = (61 \text{ pF/m} \times 40 \text{ m}) + (16 \times 250 \text{ pF}) + 5 \text{ nF}$$

$$C_{\text{totpar}} = 2,44 \text{ nF} + 4 \text{ nF} + 5 \text{ nF} = 11,44 \text{ nF}$$

Calculation for daisy-chain slave configuration

$$C_{dc} = 500 \text{ pF}$$

$$l_{dc} = 25 \text{ m}$$

$$n_{dc} = 12$$

9

where

is the maximal slave capacitance of each slave in daisy-chain configuration (2  $\times$   $C_{ab}$  because of two connections to the bus);

is the maximal permissible cable length in daisy-chain configuration;

is the maximal number of slaves that may be connected to the bus in daisy-chain configuration.

The total bus capacitance in daisy-chain configuration,  $C_{\mathrm{totdc}}$ , is calculated as follows:

$$C_{\text{totdc}} = (C_{\text{c}} \times l_{\text{dc}}) + (n_{\text{dc}} \times C_{\text{dc}}) + C_{\text{mstr}}$$

$$C_{\text{totdc}} = (61 \text{ pF/m} \times 25 \text{ m}) + (12 \times 500 \text{ pF}) + 5 \text{ nF}$$

$$C_{\text{totdc}} = 1,525 \text{ nF} + 6 \text{ nF} + 5 \text{ nF} = 12,525 \text{ nF}$$

In these examples, the total bus capacitance is 12,525 nF for a 25 m bus with 12 daisy-chain slaves, or 11,44 nF for a 40 m bus with 16 parallel slaves.

## 6.3.3 Slave supply current

A slave shall not get a d.c. supply current from the bus. The bus shall provide power pulses with a duty cycle of about 50 %. A hold-up capacitor internal to each slave can be used to supply power to the slave in between power pulses. A slave shall extract power from the power pulses only, even during power-on, when its hold-up capacitor has not yet been charged up. The average surge current needed by the slave for power extraction is about twice its average d.c. supply current, because of the 50 % duty cycle. A built-in current limit in the slave shall balance the surge current over the length of the power pulse.

#### **Bus signals** 6.4

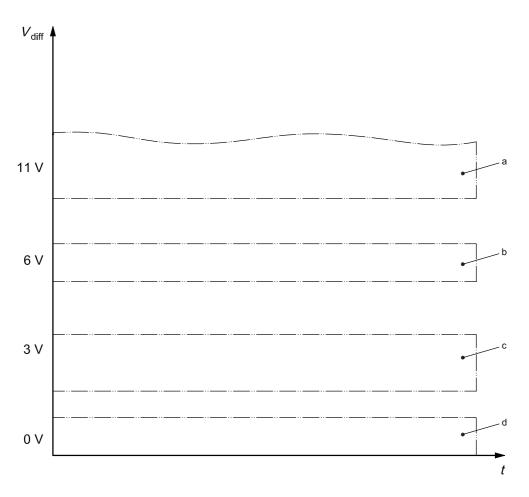

The bus shall use differential voltage signals for communications from master to slaves. Slave data shall be transmitted either by differential voltage as well, or by current modulation. All voltage signals shall have the same polarity  $V_{\text{Bus-A}} - V_{\text{Bus-B}} > 0$ . Differential bus voltages are shown in Figure 4.

- a Power distribution level "P".

- b L0 = normal data level "0".

- c L1 = normal data level "1".

- d LS0 = special data level "0" for safing, interrupt or error.

Figure 4 — Differential bus voltage levels

There shall be one bus level for power distribution and three levels for data exchange:

- P = power level;

- L0 = recessive data level for the bit value "0";

- L1 = dominant data level for the bit value "1";

- LS0 = dominant data level for either

- the interrupt signal,

- the bit value "0" with analogue safing (for deploy messages), or

- an error indication at certain bit positions (see 7.4.9 and 7.4.10).

A slave shall only transmit when the master does not output the power level. In order to allow a slave to transmit, the master shall transmit a default "0" (L0-level), which a slave may overwrite by pulling the bus down to the L1-level for transmission of a "1". Dynamic sensors shall modulate the bus voltage for

transmission of data. This way they can read back the bus signal while transmitting and detect faults like collisions with other transmitting nodes. On a deploy bus, static sensors or deployable devices may not be able to modulate the bus voltage at high bus speeds, because their transmit current may be too weak to discharge the bus capacitance in time. In this case the master shall recognize the slave data by evaluating the bus current.

A dynamic sensor slave shall have the additional option to pull an L0- or L1-level down to the LS0-level, which means either that the slave can submit an interrupt to the master or that it can indicate a detected error during transmission (see 7.4.9 and 8.5.4).

The master shall use either the L0-level or the LS0-level for the representation of a "0", depending whether the message is a normal message or a qualified one ("analogue safing"). See also 6.7.

The P-level shall be about 12 V for normal operation, or it may be raised up to 30 V for special purposes such as OTP programming in the slaves. Raising the P-level shall not be considered applicable in the system, but for off-line use only. Slaves not requiring an increased P-level for certain functions need not tolerate such a level. All slaves shall tolerate and shall not be damaged by a differential bus voltage up to 20 V. This takes into account failure modes in the airbag ECU that may lead to a temporarily increased bus level.

L0 can be overwritten by L1 or by LS0; L1 can be overwritten by LS0. The P-level cannot be overwritten by any other level. The exact bus levels are specified in 6.8.

NOTE Higher voltage at same slew rate level implies lower speed.

#### Bit coding 6.5

## 6.5.1 General

The time during which the master transmits the power level is called the Power Phase. The time during which the master transmits a data level is called the Data Phase. The master shall transmit a steady sequence of Power and Data Phases. During one Data Phase, one bit shall be transmitted (see Figure 5). The slaves shall extract power from the bus during the Power Phase only. The average duty cycle for the Power Phase should be about 50%.

Speed changes for high-speed deployment messages can be initiated by the master. For high-speed sensor polling messages, speed changes can be initiated by a sensor with interrupt capability.

Speed changes shall go into effect with the beginning of a new Power Phase (for details and restrictions, see 6.5.2).

When the master does not transmit a message (= Bus Idle) or when the master transmits a frame in which it expects a slave to transmit data, the master shall transmit the L0-level during Data Phases. The L0-level can be overwritten by another data level from a slave, when the slave is transmitting data. In order to transmit the bit value "0", the slave shall leave the Data Phase as is. In order to transmit the bit value "1", the slave shall pull the bus voltage down to L1-level. On a deploy bus during D-Frames, the master shall read the slave's transmit current, instead of checking the bus voltage. Therefore, it is not necessary that the slave actually pull the bus voltage completely down to L1-level. In order to send an interrupt or to indicate an error during S-Frames, the slave shall pull the bus voltage down to LS0-level (applicable to dynamic sensors only).

Data bits are surrounded by power distribution level phases. The level "LS0" is used either for analogue safing of deploy messages, or for signalling an interrupt or error condition from a dynamic sensor to the master.

Figure 5 — Illustration of the bit coding

## 6.5.2 Start of frame (SOF)

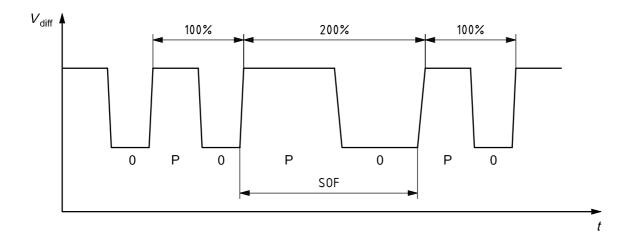

The Physical Layer shall provide a special SOF symbol, which is characterized by a temporary doubling of the duration of the Power Phase (P) and of the following Data Phase (0) of one bit (see Figure 6).

The bit level within the SOF shall indicate the type ("T", see 7.4.2) of the subsequent frame.

The master shall start a new frame by sending the SOF symbol. Usually, this is done after completion of a previous frame or during Bus Idle. The master can also send a new SOF during a frame. This shall terminate the running frame and shall start a new one. For this case, the following rules apply.

- The master shall not send an SOF immediately after an SOF, there shall be at least one data bit in between.

- When the current frame is a D-Frame requesting data and the new frame is also a D-Frame (7.3.2), the master shall send the SOF twice, with at least one idle bit in between (see also Annex C). When the new frame is a deploy command with safing, the idle bit(s) between the dual SOF shall be transmitted with safing level as well (LS0).

Figure 6 — Characterization of the SOF by a temporary doubling of the bit time

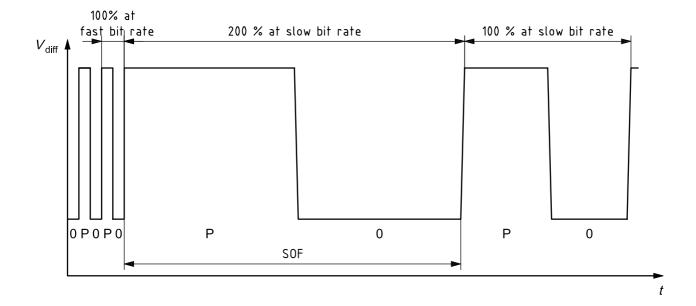

The start of a new message may also be used as the time to decrease the bus speed permanently (see Figure 7). Any lengthening of the bit time by a factor of two or more shall be recognized as the start of a new frame.

Figure 7 — Example for changing the bus speed from fast to slow with the start of a new frame

The bus speed may be increased at any time during a frame, except immediately before an SOF. If the request to increase speed and an SOF occur coincidentally, the master shall switch to high speed one bit before it sends the SOF (Figure 8).

Figure 8 — Example for changing the bus speed from slow to fast one bit before the start of a new frame

NOTE For simplicity, the data values in Figure 6, Figure 7 and Figure 8 are all "0".

## 6.6 Fault tolerance

#### 6.6.1 General

This concept provides several options to implement fault tolerance. It shall cover

- shorts of one bus wire,

- open circuits,

- shorts between the bus wires (A-to-B shorts).

## 6.6.2 Shorts of one bus wire

The main approach for tolerance of single-wire shorts is to make the bus float. Due to the definition of a steady 50 % duty cycle even during Bus Idle, capacitor-based circuitry can be used to make the bus float, without having to use a transformer. This way, shorts of one wire to any voltage within the range of at least -2 V to +16 V are tolerated, no matter whether this is a transient, intermittent or continuous short and no matter the resistance of the short.

## 6.6.3 Wire interruptions

## 6.6.3.1 General

Without a ring structure, the bus shall tolerate open bus wires by maintaining communication to all slaves between the master and the fault.

#### 6.6.3.2 Ring structure

On a pure parallel bus, the ring can be driven by a single master output (see Figure 2). In this case, an open wire within the ring shall be completely tolerated. The master cannot check whether the ring is open or closed.

The ring can be driven from two master outputs as well. In this configuration the master can check whether the ring is open or closed. However, the electrical bus parameters on a closed ring differ from those on an open ring. Therefore some restrictions apply, which are explained below.

All voltage-specific bus signals shall be independent of the status of the ring. This includes all urgent messages like commands from master to slaves on a deploy bus and sensor data on a sensor bus. For these messages, the frames shall be transmitted by the master on both outputs. Slave data shall be decoded on both outputs, the actual slave data being the result of a bit-wise OR function of the individual signals. The bus transfer of such messages shall fully tolerate any opening or closure of the ring. No such message shall be lost.

All current-specific bus signals, such as reply data from slaves within D-Frames, are dependent on the status of the ring. When the master data bias current ( $I_{\rm Dsrc}$ ) (see Table 1) is driven from both sides at the same time, the ECU may not be able to receive such slave data. Therefore the following rules apply to a ring driven by two bus outputs.

- For D-Frames,  $I_{Dsrc}$  shall be switched off on **one** bus output during bits that carry slave data.

- The slave current shall be checked at the one output at which  $I_{Dsrc}$  is active.

- When there is no slave reply detectable, the message frame shall be repeated with  $I_{\rm Dsrc}$  being active at the other output and checking the slave current from there. This could happen when the ring is open. The master shall locate the open wire by checking which slave is replying to which output.

## 6.6.4 Bus A-to-B shorts

## 6.6.4.1 General

The bus shall fully tolerate Bus A-to-B short circuit currents of up to 5 mA. On a parallel bus, the ability to send and receive messages with safing level shall be maintained even with short circuit currents of up to 20 mA. On a daisy-chain bus, short circuits of more than 5 mA can be isolated by reconfiguration of the daisy-chain.

## 6.6.4.2 Recovery from A-to-B shorts on a deployment bus in parallel configuration

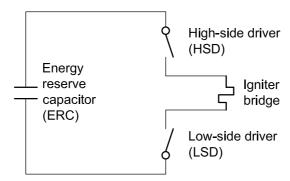

Parallel deployable devices or static sensors on a deployment bus shall be connected to the bus through discrete resistors. These resistors prevent the slave from shorting the bus wires A-to-B. The resistors may be part of the slaves, or they are inserted in the wiring harness between master and slave. Both solutions may also be combined (see Figure 10). However, such resistors shall only maintain the capability of transmitting messages with analogue safing from master to slaves, in spite of an A-to-B short. This means that deploy messages can still be sent, but diagnostic communication or polling of sensor data can no longer proceed, because of the short.

## 6.6.4.3 Recovery from A-to-B shorts in daisy-chain configuration

There shall be two ways of recovering from an A-to-B short:

- real-time recovery by hardware;

- recovery by software.

Recovery by software may be chosen for all kind of problems where the origin of the problem is located by testing the individual bus sections. Once it has been identified that the occurrence of the problem is correlated

to the closure of one of the daisy-chain switches, the master can decide to leave this particular switch off in order to maintain communication in the remaining bus sections.

Hardware recovery shall be available for recovery from "true" shorts. A "true" short is defined as a low-ohmic short that prevents the master from generating a sufficient power level,  $V_{\rm LP}$ , with the consequence that the bus signal does not exceed the  $V_{\rm P0}$  threshold at one or several nodes (which can include the master itself).

A slave shall detect a "true" short by checking the time having elapsed since the last Power Phase. When this time is significantly longer than the duration of one bit at lowest bus speed, the slave shall assume the presence of a "true" short and open its daisy-chain switch.

A master shall detect a "true" short by checking the bus level during Power Phase. When the bus level is lower than the  $V_{\rm P0}$  threshold, the master shall assume the presence of a "true" short and shut down the bus output.

When a slave has detected a "true" short and has opened its daisy-chain switch accordingly, it shall wait for a bus voltage higher than the  $V_{\rm P0}$  threshold on one of the two sides of the daisy-chain switch. When this is available, it shall forward a test current to the other side during Power Phase. If the bus voltage on this side exceeds the  $V_{\rm 01}$  threshold again, it is assumed that the short is gone and the slave shall switch on the daisy-chain switch again.

When a master has detected a "true" short and has switched off the bus accordingly, it shall wait for one bit time and afterwards turn on a test current to check if the short is still present. When the bus voltage reaches the  $V_{01}$  threshold again, it is assumed that the short is gone and the master shall switch on the bus output again.

The power-up behaviour of a master or a slave shall be basically the same as described above for recovery from an A-to-B short. The bus shall be tested with a test current: if positive, the bus shall be switched on; if negative, the master can double-check by commanding the closure of a daisy-chain switch and simply testing whether it can still communicate afterwards.

During initial power-on of a slave, its daisy-chain switch shall be open. Immediately after power-on, the slave shall behave as after an A-to-B short detection: when  $V_{\rm P0}$  is reached on one side, the test current shall be switched on and the daisy-chain switch shall be closed as soon as  $V_{\rm 01}$  has been crossed on the other bus side.

NOTE Even when the slave fails to close the switch automatically, the master can still command the closure of the daisy-chain switch to double-check whether there is really an A-to-B short behind that slave.

## 6.7 Use of analogue safing on a deployment bus

## 6.7.1 General

The master shall send out a message with analogue safing almost in the same way as without safing. It shall simply replace the L0-level by the LS0-level for representation of a "0", and keep the L1-level for representation of a "1".

A slave shall recognize both levels, L0 and LS0, as a data bit value "0". The LS0-level shall additionally qualify a deploy message as a "serious" one.

A slave shall accept a message in two cases:

- when all bits of content "0" are represented with L0-level;

- when all bits of content "0" are represented with LS0-level.

When some bits of a frame are represented with L0-level and others with LS0-level (= inconsistent safing), the message shall be ignored and regarded as a bus error (see 8.4.7). This gives additional protection against corrupted messages. Slaves, for which this extra level of protection is not needed, may not be able to receive

messages transmitted with safing. These slaves need not check for consistent safing and may not even be able to recognize an LS0-level at all.

A message of the deploy command family (see 8.4.2) that is sent without safing level, shall be accepted by the deploy slaves (i.e. not regarded as bus error), but a command to turn on a deploy switch shall be refused in this case.

A slave shall not reply in a D-Frame that has been started with safing level.

Master and slave on a deploy bus should process the safing information as far as possible away from the circuitry for handling the binary bit patterns of bus messages. Then the probability is low that a fault in a device corrupts both the bit pattern and the safing information at the same time.

## 6.7.2 Immunity to "babbling idiots"

When a parallel slave ASIC is shorted or a slave is transmitting without having been asked to do so ("babbling idiot"), a message sent by the master can get corrupted, since the defective slave can pull the L0-level down to L1-level, though the slave cannot modify the L1-level significantly. The master can recognize such a fault by reading back the bits while transmitting. The master shall then make the message artificially invalid to avoid the slaves receiving wrong data. An appropriate way to make a message invalid can be to send L1-level during the E-bit slot. Alternatively, the master can interrupt the faulty message by sending an SOF and starting a new frame. In any case, the master can send out a message with analogue safing level, e.g., a "serious" deploy message. Since a slave on the deployment bus cannot influence the L1-level or the LS0-level, the message is transmitted and received without bit error.

#### **Bus signal parameters** 6.8

Table 1 summarizes the bus signal parameters that are common for all implementations of the automotive safety restraints bus. Other parameters depend on the application. These are listed in Table 2, for a standard deployment bus and for a standard sensor bus. For non-standard applications, these parameters may be varied. A guideline for such variations is given in Annex B.

Table 3 lists the recommended cable parameters. Deviations are possible, depending on the actual bus speed and bus topology specifics.

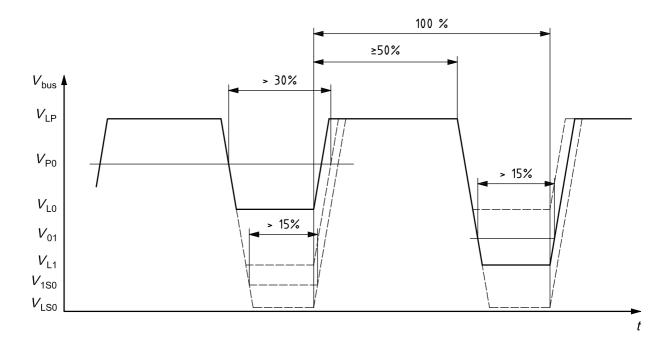

Data bits shall consist of a sequence of Power and Data Phases with a Power Phase duty cycle of at least 50 % (see Figure 9). This ensures that the average surge current during the Power Phase is not much higher than twice the average supply current of the slaves. The nominal duration of one bit (= 100 %) shall be

- between 5,5 µs (181,8 kbit/s) and 14 µs (71,4 kbit/s) at high speed,

- between 22 µs (45,5 kbit/s) and 28 µs (35,7 kbit/s) at mid-speed,

- between 44 µs (22,7 kbit/s) and 56 µs (17,9 kbit/s) at low speed.

The devices may support other bit rates as well. A master implementation may support only a few discrete bus speeds. A slave implementation shall support all bus speeds within the above-specified speed ranges. A slave shall automatically adjust to the bus speed set by the master. Modules not requiring all three speed ranges may support less than these three speed ranges.

**EXAMPLE** A side-impact acceleration sensor may be optimized for high-speed operation and not support lower speeds.

The slew rate shall be high enough to guarantee a minimum data-signal dwell time below the respective receiver threshold of 15 % of one bit time or 1 μs, whichever is longer. The Data Phase itself (i.e. the time for which the bus voltage is lower than the  $V_{P0}$  threshold) shall be at least 30 % of one bit time. See also Figure 9.

Figure 9 — Duty cycle of the Power and Data Phases

Figure 10 — Definition of parameters

Table 1 — Common bus parameters

| Symbol             | Parameter                                                                                                                            | Condition/remarks                                                                                                                                        | Min.         | Max.            | Unit   |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------|--------|

| $V_{LP}$           | differential bus voltage at power level                                                                                              | normal operation<br>OTP programming mode, max. 33 kbit/s                                                                                                 | 10,1<br>10,1 | 12,5<br>30      | V<br>V |

| $V_{P0}$           | receiver threshold P/0                                                                                                               |                                                                                                                                                          | 6,6          | 8,0             | V      |

| $V_{L0}$           | differential bus voltage at data level 0                                                                                             |                                                                                                                                                          | 4,9          | 6,1             | V      |

| V <sub>01</sub>    | receiver threshold 0/1                                                                                                               |                                                                                                                                                          | 3,6          | 4,4             | V      |

| $V_{L1}$           | differential bus voltage at data level 1, master is transmitting                                                                     |                                                                                                                                                          | 2,5          | 3,1             | ٧      |

| V <sub>L1slv</sub> | differential bus voltage at data level 1, slave is transmitting (slaves with voltage transmitter, e.g. sensors replying to S-Frames) | measured at slave,<br>0 < I < 12  mA,<br>$(I_{\text{Dsaf}} = 0, R_{\text{par}} = 0, R_{\text{iso}} = 0)$                                                 | 2            | 2,9             | >      |

| V <sub>1S0</sub>   | receiver threshold 1/S0                                                                                                              |                                                                                                                                                          | 1,2          | 1,5             | V      |

| V <sub>LS0</sub>   | differential bus voltage at data level LS0                                                                                           | measured at transmitter (master or slave)                                                                                                                | 0            | 0,5             | ٧      |

| $I_{Dsrc}$         | master data bias current                                                                                                             | master sends L0-level, $V_{\rm bus} < V_{\rm L0}$                                                                                                        | - 5          | - 10            | mA     |

| I <sub>01</sub>    | D-Frame slave data current threshold                                                                                                 |                                                                                                                                                          | - 5          | - 10            | mA     |

| $I_{lkg}$          | tolerated leakage current during Data<br>Phase                                                                                       | Bus-A to Bus-B and Bus to ground (bus isolation at master)                                                                                               |              | 5               | mA     |

| I <sub>Dsaf</sub>  | master data safing current<br>(only active when parallel deployable<br>devices are on the bus)                                       | master sends L0- or L1-level, $V_{\rm bus}$ < $V_{\rm L1}$                                                                                               | - 20         | - 40            | mA     |

| $V_{\sf par}$      | bus voltage at parallel slave ASIC while transmitting during D-Frames                                                                | I = 12 mA                                                                                                                                                |              | 0,9             | V      |

| $I_{Dtxd}$         | slave data transmit current                                                                                                          | 3,9 V < V <sub>bus</sub>                                                                                                                                 | 12           | 24 <sup>a</sup> | mA     |

|                    | (daisy-chain deployable devices or sensors with current transmitter, i.e.                                                            | 2,5 V < V <sub>bus</sub> < 3,9 V                                                                                                                         | 0            | 24 <sup>a</sup> | mA     |

|                    | sensors not replying to S-Frames)                                                                                                    | V <sub>bus</sub> < 2,5 V                                                                                                                                 | 0            | 1               | mA     |

|                    |                                                                                                                                      | measured at slave                                                                                                                                        |              |                 |        |

| $C_{mstr}$         | effective capacitance between Bus-A and Bus-B at master because of external components                                               | one bus wire shorted to ground                                                                                                                           |              | 5               | nF     |

| $I_{tst}$          | test current during Power Phase for                                                                                                  | <i>V</i> <sub>bus</sub> < 5 V                                                                                                                            | 2,2          | 4,4             | mA     |

|                    | daisy-chain recovery from A-to-B shorts                                                                                              | 5 V < V <sub>bus</sub> < 7,5 V                                                                                                                           | 0            | 4,4             | mA     |

|                    | (used by master before switching on                                                                                                  | 7,5 V < V <sub>bus</sub>                                                                                                                                 | 0            | 0,1             | mA     |

|                    | the bus, or used by slave before closing daisy-chain switch)                                                                         | measured at tested bus section                                                                                                                           |              |                 |        |

| t <sub>ko</sub>    | time-out for detection of an A-to-B short by a daisy-chain slave                                                                     | time between end of previous Power Phase $(V_{\rm bus} < V_{\rm P0})$ and beginning of next Power Phase $(V_{\rm bus} > V_{\rm P0})$ , measured at slave | 60 b         | 240             | μs     |

NOTE Unless specified differently, all bus voltages are measured at the master.

The slave transmit current during the falling edge may be higher.

Allows bus speeds down to 20 kbit/s with a tolerance of - 10 %. For non-standard, lower bus speeds, this number shall be increased accordingly.

Table 2 — Application-specific parameters

| Symbol             | Parameter                                                                                           | Condition/remarks                                                                                  | Min.    | Max.                                               | Unit     |

|--------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------|----------------------------------------------------|----------|

| Standar            | d deployment bus                                                                                    |                                                                                                    | •       |                                                    |          |

| $I_{\mathrm{srg}}$ | Surge current of a slave                                                                            | $\begin{array}{c} V_{\rm bus} > 8 \ {\rm V} \\ V_{\rm bus} < 8 \ {\rm V} \end{array}$              |         | 4 <sup>a</sup><br>0,1 <sup>b</sup>                 | mA<br>mA |

| R <sub>par</sub>   | value of bus protection resistor at parallel slave                                                  | pure parallel bus or mixed<br>parallel/daisy-chain bus,<br>two resistors of this value are<br>used | 75 – 5% | 75 + 5%                                            | Ω        |

| R <sub>iso</sub>   | value of bus protection resistor in harness<br>between master and one parallel slave                | pure parallel bus,<br>two resistors of this value are<br>used                                      | 75 – 5% | 75 + 5%                                            | Ω        |

| $R_{dc}$           | on-resistance of daisy-chain switch in slave                                                        |                                                                                                    |         | 5                                                  | Ω        |

| $C_{ab}$           | capacitance of external components applied between pins a and b or a and <u>b</u> of a slave        |                                                                                                    |         | 250                                                | pF       |

| n <sub>par</sub>   | number of slaves in a pure parallel bus                                                             |                                                                                                    |         | 16                                                 | 1        |

| n <sub>dc</sub>    | number of slaves in a in a pure daisy-chain or mixed parallel/daisy-chain bus                       |                                                                                                    |         | 12                                                 | 1        |

| n <sub>dcmx</sub>  | number of daisy-chain slaves between master and parallel slaves in a mixed parallel/daisy-chain bus | reference configuration: MDPPDPPDPPDPP  M = master                                                 |         | 4                                                  | 1        |

| n <sub>pardc</sub> | number of parallel slaves between two daisy-<br>chain slaves                                        | D = daisy-chain slave<br>P = parallel slave                                                        |         | 2                                                  | 1        |

| Standar            | d sensor bus                                                                                        |                                                                                                    |         |                                                    |          |

| $I_{ m srg}$       | surge current of a slave                                                                            | $V_{\rm bus}$ > 8 V $V_{\rm bus}$ < 8 V                                                            |         | 45 <sup>a</sup><br>0,1 <sup>b</sup>                | mA<br>mA |

| $R_{dc}$           | on-resistance of daisy-chain switch in slave                                                        |                                                                                                    |         | 5                                                  | Ω        |

| $C_{ab}$           | capacitance of external components applied between pins a and b or a and <u>b</u> of a slave        |                                                                                                    |         | 500                                                | pF       |

| n <sub>par</sub>   | number of slaves in a pure parallel bus                                                             |                                                                                                    |         | all be able $_{ m par} 	imes I_{ m srg}$ $^{ m c}$ | to drive |

| $n_{\sf dc}$       | number of slaves in a pure daisy-chain bus                                                          |                                                                                                    |         | 4                                                  | 1        |

| Extende            | ed sensor bus                                                                                       |                                                                                                    |         |                                                    |          |

| $I_{ m srg}$       | surge current of a slave                                                                            | $V_{\rm bus}$ > 8 V $V_{\rm bus}$ < 8 V                                                            |         | 30 <sup>a</sup><br>0,1 <sup>b</sup>                | mA<br>mA |

| $R_{\sf dc}$       | on-resistance of daisy-chain switch in slave                                                        |                                                                                                    |         | 3                                                  | Ω        |

| $C_{ab}$           | capacitance of external components applied between pins a and b or a and <u>b</u> of a slave        |                                                                                                    |         | 500                                                | pF       |

| n <sub>par</sub>   | number of slaves in a pure parallel bus                                                             |                                                                                                    |         | all be able $_{ m par} 	imes I_{ m srg}$ c         | to drive |

| n <sub>dc</sub>    | number of slaves in a pure daisy-chain bus                                                          |                                                                                                    |         | 6                                                  | 1        |

| NOTE               | "Non-standard" systems with different values are po                                                 | ossible.                                                                                           |         |                                                    |          |

| a For (            | daisy-chain operation, this limit shall be implemented in                                           | the slave's nower extractor. See also                                                              | Anney A |                                                    |          |

<sup>&</sup>lt;sup>a</sup> For daisy-chain operation, this limit shall be implemented in the slave's power extractor. See also Annex A.

<sup>&</sup>lt;sup>b</sup> A slave shall not extract power during Data Phase.

<sup>&</sup>lt;sup>c</sup> At high speed, further restrictions apply (depending on actual speed and on implementation of devices).

Table 3 — Recommended cable parameters

| Symbol               | Parameter                                                                                               | Condition/remarks              | Min. | Max.            | Unit |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------|--------------------------------|------|-----------------|------|--|--|--|--|--|--|

| $l_{\sf par}$        | total bus cable length for pure parallel configuration                                                  | sum of lengths of all branches |      | 40 <sup>a</sup> | m    |  |  |  |  |  |  |

| $l_{ee}$             | cable distance between any two cable ends                                                               |                                |      | 25 <sup>a</sup> | m    |  |  |  |  |  |  |

| l <sub>dc</sub>      | total bus cable length for pure daisy-chain or mixed parallel/daisy-chain configuration                 | sum of lengths of all branches |      | 25 <sup>a</sup> | m    |  |  |  |  |  |  |

| Z                    | specific cable impedance                                                                                |                                | 95   | 140             | Ω    |  |  |  |  |  |  |

| $C_{c}$              | cable capacitance                                                                                       | one bus wire shorted to ground |      | 61              | pF/m |  |  |  |  |  |  |

| <sup>a</sup> At high | At high speed, further restrictions apply (depending on actual speed and on implementation of devices). |                                |      |                 |      |  |  |  |  |  |  |

## 7 Data Link Layer

## 7.1 Bus Idle

Bus Idle shall be represented by a continuously repeated sequence of levels P-L0-P-L0-.... This ensures that a maximum latency time for a sensor interrupt can be specified.

During power-on, also a long Power Phase may be applied to the bus in order to accelerate power-on of the slaves.

#### 7.2 Addresses

## 7.2.1 Slave address

The bus shall support 64 slave addresses, 0 through 63. However, the actual number of slaves that may be connected to one bus is limited by the supply current for the slaves, the pin capacitance of the slaves (see also Clauses 5 and 6) and the bandwidth. A single slave may incorporate the functionality of several slave addresses.

The slave address 0b000000 (0x00) should be reserved for slaves that have not yet been programmed with an address. Slave addresses shall be programmed into non-volatile memory in slaves with parallel configuration.

NOTE When slaves are used in daisy-chain configuration, their slave address can be stored in their volatile or non-volatile memory.

With the address a parity bit shall be stored (even parity). When a slave detects a parity error for its programmed address, it shall ignore the programmed address, set the "internal error" status (see Table 27) and adopt the reserved address 62 = 0x3e for communication with the master.

The slave address 63 = 0x3f shall be reserved for optional broadcast commands from the master. All slaves, independent of their actual programmed slave address, shall execute a command sent to slave address 63. All slaves shall ignore a message requesting data from slave address 63.

Usage of slave addresses is given in Table 4.

Table 4 — Usage of slave addresses

|         | Slave addre | ess               | Usage                                                                                                     |  |  |  |  |  |  |

|---------|-------------|-------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| decimal | hex         | binary            | Usage                                                                                                     |  |  |  |  |  |  |

| 63      | 0x3f        | 11 1111           | broadcast commands: all slaves shall accept commands sent to this address (optional feature)              |  |  |  |  |  |  |

| 62      | 0x3e        | 11 1110           | address error: slaves that detect a parity error in their programmed address shall switch to this address |  |  |  |  |  |  |

| 60 – 61 | 0x3c - 0x3d | 11 1100 – 11 1101 | for sensors                                                                                               |  |  |  |  |  |  |

| 48 – 59 | 0x30 – 0x3b | 11 0000 – 11 1011 | for sensors or deployable devices                                                                         |  |  |  |  |  |  |

| 44 – 47 | 0x2c - 0x2f | 10 1100 – 10 1111 | for sensors                                                                                               |  |  |  |  |  |  |

| 32 – 43 | 0x20 – 0x2b | 10 0000 – 10 1011 | for sensors or deployable devices                                                                         |  |  |  |  |  |  |

| 28 – 31 | 0x1c - 0x1f | 01 1100 – 01 1111 | for sensors                                                                                               |  |  |  |  |  |  |

| 16 – 27 | 0x10 - 0x1b | 01 0000 – 01 1011 | for sensors or deployable devices                                                                         |  |  |  |  |  |  |

| 12 – 15 | 0x0c - 0x0f | 00 1100 – 00 1111 | for sensors                                                                                               |  |  |  |  |  |  |

| 1 – 11  | 0x01 – 0x0b | 00 0001 – 00 1011 | for sensors or deployable devices                                                                         |  |  |  |  |  |  |

| 0       | 0x00        | 00 0000           | default address of an unprogrammed slave                                                                  |  |  |  |  |  |  |

## 7.2.2 Memory address

Each slave has internal memory, which may consist of volatile and/or non-volatile (register, RAM, OTP, MTP or ROM) memory cells of 8-bit size. Each cell shall have a slave-specific **memory address**.

## 7.2.3 Signal address

A slave with Multi-Sharing capability (see 7.3.3.4) shall use an individual 6-bit **signal address** for each signal that it can transmit during S-Frames. Like the slave address, each signal address shall be unique for a given bus. When the slave serves only one signal, this signal address may be identical to the slave address of that slave.

The signal address shall have an attribute "sample" or "no sample", depending on its numerical value (Table 5). The sampling shall be performed by successful acceptation of any Multi-Sharing address with the sampling attribute set to "sample". This shall be used for synchronization of signal samples (see 7.3.3.6).

Table 5 — Signal address attributes

| Signal address             | Attribute |

|----------------------------|-----------|

| 0x00 - 0x1f (i.e. MSB = 0) | sample    |

| 0x20 - 0x3f (i.e. MSB = 1) | no sample |

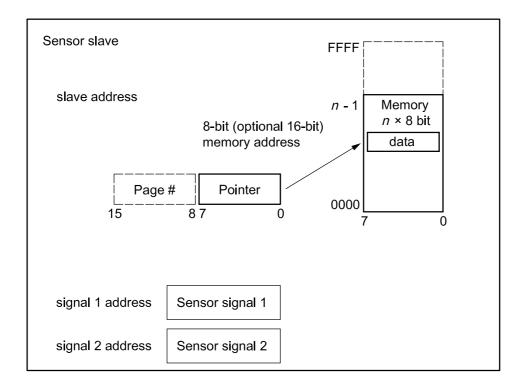

Slave address, memory address and signal address of a sensor slave are illustrated in Figure 11.

Figure 11 — Illustration of slave address, memory address and signal address of a sensor slave

#### 7.3 Message frames

#### 7.3.1 General

A message frame shall be transmitted exclusively by the master. Frames shall be used either to transfer data from the master to one or several slaves, or to transfer data from one or several slaves to the master. In the latter case, the master shall send the frame with L0-level at all bit positions that will contain slave data. The slave(s) shall overwrite these bits according to the data to be sent to the master.

A message frame shall start with an SOF symbol (see 6.5.2), which shall be transmitted by the master. A message shall end when the specified number of data bits of the frame has been transmitted. After the end of a frame, the master may either start a new frame or continue with the Bus Idle signal. An already started message frame can be cancelled by sending a new SOF symbol before completion of the frame.

There are two different message frame types available.

- The **D-Frame** shall be mainly used for diagnostic data and deploy commands.

- The S-Frame shall be mainly used for fast polling of sensor data (crash severity data or raw impact sensing data).

The data level within the SOF shall indicate the frame type ("T", see 7.4.2).

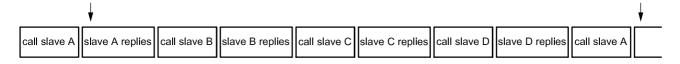

#### 7.3.2 D-Frames

## Table 6 — Layout of the D-Frame

| 1    |     | 2    | 3                | 4    | 5    | 6    | 7         | 8     | 9     | 10                 | 11   | 12   | 13   | 14   | 15   | 16   | 17   | 18   | 19 | 20   | 21   | 22   | 23   | 24   | 25 | 26   | 27 | 28 | 29 |

|------|-----|------|------------------|------|------|------|-----------|-------|-------|--------------------|------|------|------|------|------|------|------|------|----|------|------|------|------|------|----|------|----|----|----|

|      |     |      |                  |      |      |      |           |       |       |                    |      |      |      |      |      |      |      |      |    |      |      |      |      |      |    |      |    |    |    |

| D-F  | ram | e w  | ith <sub> </sub> | poin | t-to | -poi | nt a      | ddre  | essir | ing:               |      |      |      |      |      |      |      |      |    |      |      |      |      |      |    |      |    |    |    |

| trai | nsm | itte | d by             | ma   | ster | •    |           |       |       |                    |      |      | trai | nsm  | itte | d by | ma   | ster | or | by s | lave | )    |      |      |    |      |    |    |    |

| Т    |     | R    | Со               | mm   | and  |      | 6-b       | it sl | ave   | add                | ress | 3    | 8-b  | it D | ata  |      |      |      |    |      | 8-b  | it C | RC   |      |    |      |    |    | Е  |

|      |     |      |                  |      |      |      |           |       |       |                    |      |      |      |      |      |      |      |      |    |      |      |      |      |      |    |      |    |    |    |

|      | •   |      |                  |      |      |      |           |       |       |                    |      |      |      |      |      |      |      |      |    |      |      |      |      |      |    |      |    |    |    |

| D-F  | ram | e w  | ith I            | oitm | ара  | addr | ess       | ing:  |       |                    |      |      |      |      |      |      |      |      |    |      |      |      |      |      |    |      |    |    |    |

| trai | nsm | itte | d by             | ma   | ster | ,    |           |       | trai  | nsm                | itte | d by | ma   | ster | or l | by s | lave | )    |    |      | tra  | nsm  | itte | d by | ma | ster |    |    |    |

| Т    |     | R    | Co               | mm   | and  |      | Add<br>MS |       | Sla   | Slave address bitr |      |      |      |      |      |      |      |      |    |      | 8-b  | it C | RC   |      |    |      |    |    | E  |

|      |     |      |                  |      |      |      |           |       | В     | Α                  | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1  | 0    |      |      |      |      |    |      |    |    |    |

|      |     |      |                  |      |      |      | 1         |       |       |                    |      |      |      |      |      |      |      |      | •  | •    |      | •    |      |      |    |      |    |    |    |

The layout of the D-Frame is shown in Table 6. It shall include several bit fields, which are explained later in this International Standard. A D-Frame can use point-to-point addressing or bitmap addressing. Point-to-point addressing shall be used for diagnostic communications on a deploy or sensor bus. Bitmap addressing shall be used for immediate control of deploy states of several deployable devices at a time. Both addressing types may be used for sending data to slaves and for getting data from slaves.

NOTE Point-to-point addressing may also be used for broadcasting of commands, see 7.2.1.

When a D-Frame is used to carry data from the master to one or several slaves, the master shall send the according bus level for each bit and verify with its receiver circuitry that the right bus levels actually appear on the bus. Depending on the result of this check, the master shall send a "0" (= ok) or a "1" (= error) in the E-bit slot.

When a D-Frame is used to carry data from a slave to the master, the master shall send L0-level in the data and CRC field and send a "1" (= error) in the E-bit slot (see 7.4.10). The slave shall modulate the current and/or the bus voltage in the data and CRC field according to the data to be sent. Current modulation can turn the master's L0-level into L1-level or the level may be left as is. The slave shall ignore the bus voltage level while transmitting. The master shall receive slave data by evaluating the bus current and/or the bus voltage. Evaluation of the bus current is only necessary on a deploy bus.

When a D-Frame is used to collect one-bit data from several slaves (by using bitmap addressing), the master shall send L0-level in the address bitmap and CRC field and send a "1" (= error) in the E-bit slot. Each slave that belongs to the selected address bank shall modulate the current and/or the bus voltage in its respective address bitmap slot according to the bit information it wants to send. Current modulation can turn the master's L0-level into L1-level or the level may be left as is. The slave shall ignore the bus voltage level while transmitting. The master shall receive slave data by evaluating the bus current and/or the bus voltage. The CRC field shall not be filled with slave data and shall be ignored by master and by slaves.

#### 7.3.3 S-Frames

#### 7.3.3.1 General

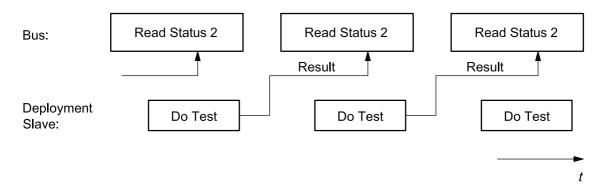

S-Frames have been defined for high throughput of sensor data to the master. The master shall start a frame with SOF and the appropriate T-bit (see 7.4.2). Then the slaves shall fill in their data in the respective slots of the frame, according to their set-up. Each slave shall append a CRC (see 7.4.9) to its data. Slaves shall modulate the bus voltage for data transmission.

In general, the S-Frame can support any number of slots, any length of data and individual data length for each sensor. However, the master shall know which sensor is using which data length and how many sensors are sending data within one frame. The data length should be eight or ten bits for raw-data sensors, or four bits for smart sensors sending crash severity levels (see Tables 7 and 8). For other sensors with short data length, see also 7.3.3.5. Accordingly, the bit number where the sensor's data slot starts shall be programmed into each slave. A master implementation should have a programmable number of slots, at least up to three slots.

The CRC-length used in S-Frames shall be either 3-bit or 8-bit. It shall be selectable as a global parameter for one bus.

- **EXAMPLE 1** A master implementation may be programmable to use the 3-bit CRC or the 8-bit CRC for all S-Frames.

- **EXAMPLE 2** A raw-data sensor slave implementation may support 3-bit CRC only.

Slaves sending data that does not need CRC protection may not send a CRC at all, which means that **EXAMPLE 3** the CRC field may be left empty (all 0).

Table 7 — Example layout of an S-Frame with 4-bit crash severity data from three sensors

| 1           | 2            | 3           | 4           | 5    | 6      | 7     | 8     | 9     | 10   | 11 | 12   | 13     | 14    | 15    | 16    | 17   | 18 | 19   | 20     | 21    | 22    | 23    | 24   | 25 |

|-------------|--------------|-------------|-------------|------|--------|-------|-------|-------|------|----|------|--------|-------|-------|-------|------|----|------|--------|-------|-------|-------|------|----|

|             | 1            | 2           | 3           | 4    | 5      | 6     | 7     | 8     | 9    | 10 | 11   | 12     | 13    | 14    | 15    | 16   | 17 | 18   | 19     | 20    | 21    | 22    | 23   | 24 |

|             |              |             |             |      |        |       |       |       |      |    |      |        |       |       |       |      |    |      |        |       |       |       |      |    |

| Hea         | der          |             |             | Slo  | t 0    |       |       |       |      |    | Slot | : 1    |       |       |       |      |    | Slot | 2      |       |       |       |      |    |

| tran<br>mas | smit<br>ster | ted         | by          | tran | smit   | ted k | y sla | ave n | ю. 0 |    | tran | smit   | ted b | y sla | ave n | o. 1 |    | tran | smit   | ted k | y sla | ave n | ю. 2 |    |

| Т           |              | M<br>S<br>A | S<br>E<br>L | slav | /e-0 ( | data  |       | CRO   | 3    |    | slav | re-1 c | lata  |       | CRO   | ;    |    | slav | re-2 ( | data  |       | CRO   | 3    |    |

| Slot        | bit n        | o. (he      | ex)         | 1    | 2      | 3     | 4     | 5     | 6    | 7  | 8    | 9      | а     | b     | С     | d    | е  | f    | 10     | 11    | 12    | 13    | 14   | 15 |

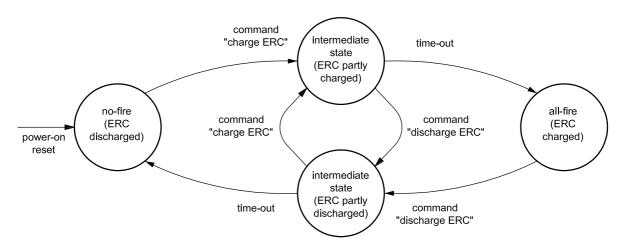

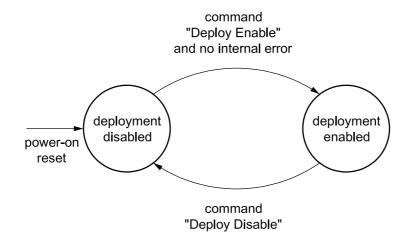

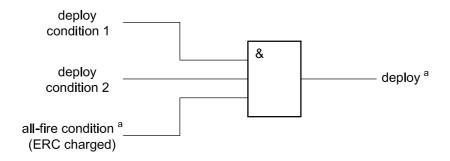

|             |              |             |             |      |        |       |       |       |      |    |      |        |       |       |       |      |    |      |        |       |       |       |      |    |