# INTERNATIONAL STANDARD

ISO 17987-7

First edition 2016-12-01

# Road vehicles — Local Interconnect Network (LIN) —

Part 7:

**Electrical Physical Layer (EPL)** conformance test specification

Véhicules routiers — Réseau Internet local (LIN) —

Partie 7: Spécification d'essai de conformité de la couche électrique physique (EPL)

# **COPYRIGHT PROTECTED DOCUMENT**

### © ISO 2016, Published in Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Ch. de Blandonnet 8 • CP 401 CH-1214 Vernier, Geneva, Switzerland Tel. +41 22 749 01 11 Fax +41 22 749 09 47 copyright@iso.org www.iso.org

| Co   | Contents |                                                                                                         |          |  |

|------|----------|---------------------------------------------------------------------------------------------------------|----------|--|

| Fore | eword    |                                                                                                         | v        |  |

| Intr | oductio  | n                                                                                                       | vi       |  |

| 1    | Scop     | e                                                                                                       | 1        |  |

| 2    | _        | native references                                                                                       |          |  |

| _    |          |                                                                                                         |          |  |

| 3    | 3.1      | ns, definitions, symbols and abbreviated terms<br>Terms and definitions                                 |          |  |

|      | 3.2      | Symbols                                                                                                 |          |  |

|      | 3.3      | Abbreviated terms                                                                                       |          |  |

| 4    | Conv     | rentions                                                                                                |          |  |

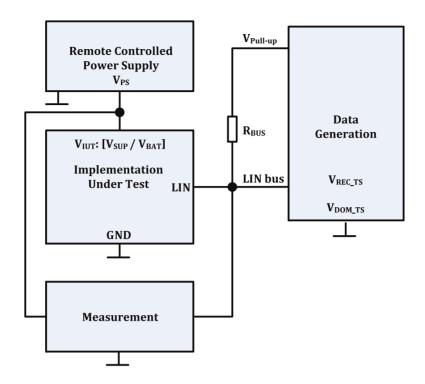

| 5    | EPI.     | 12 V LIN devices with RX and TX access                                                                  | 5        |  |

| 0    | 5.1      | Test specification overview                                                                             |          |  |

|      |          | 5.1.1 Test case organization                                                                            |          |  |

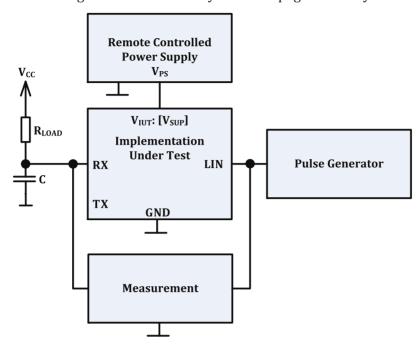

|      |          | 5.1.2 Measurement and signal generation requirements                                                    | 6        |  |

|      | 5.2      | Operational conditions — Calibration                                                                    |          |  |

|      |          | 5.2.1 Electrical input/output, LIN protocol                                                             |          |  |

|      |          | 5.2.2 [EPL-CT 1] Operating voltage range                                                                |          |  |

|      |          | 5.2.3 Threshold voltages                                                                                |          |  |

|      |          | 5.2.4 [EPL–CT 5] Variation of V <sub>SUP_NON_OP</sub>                                                   |          |  |

|      |          | 5.2.6 Slope control                                                                                     |          |  |

|      |          | 5.2.7 Propagation delay                                                                                 |          |  |

|      |          | 5.2.8 Supply voltage offset                                                                             |          |  |

|      |          | 5.2.9 Failure                                                                                           | 28       |  |

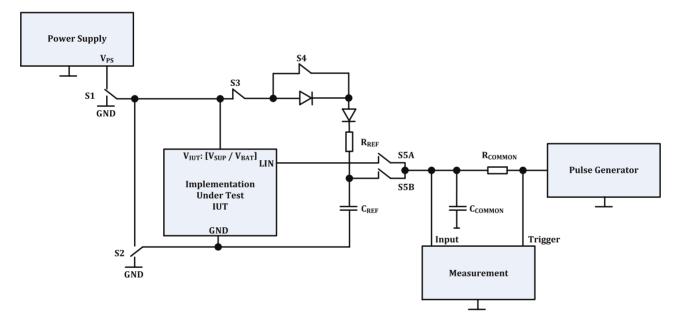

|      |          | 5.2.10 [EPL-CT 22] Verifying internal capacitance and dynamic interference — IUT as slave               |          |  |

|      | 5.3      | Operation mode termination                                                                              |          |  |

|      |          | 5.3.1 General                                                                                           |          |  |

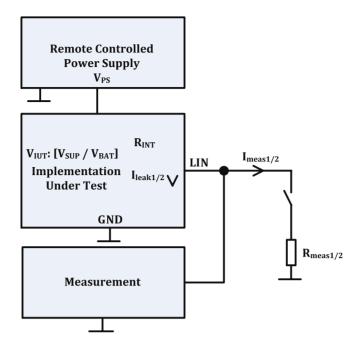

|      |          | 5.3.2 [EPL-CT 23] Measuring internal resistor — IUT as slave                                            |          |  |

|      | F 4      | 5.3.3 [EPL-CT 24] Measuring internal resistor — IUT as master                                           |          |  |

|      | 5.4      | Static test cases                                                                                       |          |  |

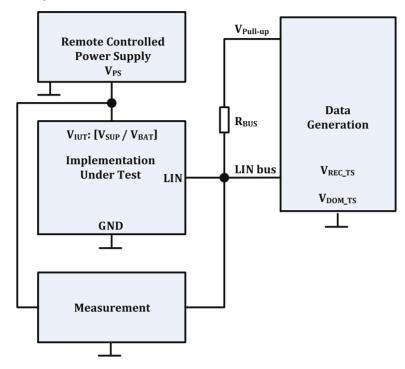

| 6    |          | 12 V LIN devices without RX and TX access                                                               |          |  |

|      | 6.1      | Test specification overview                                                                             |          |  |

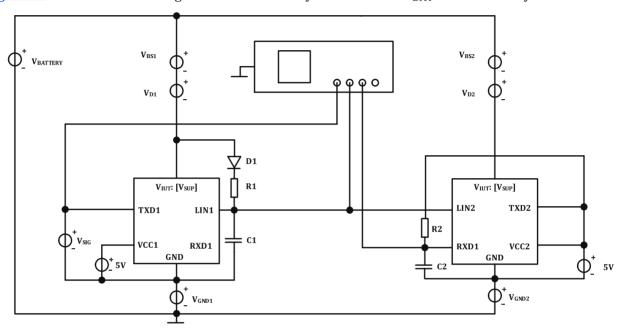

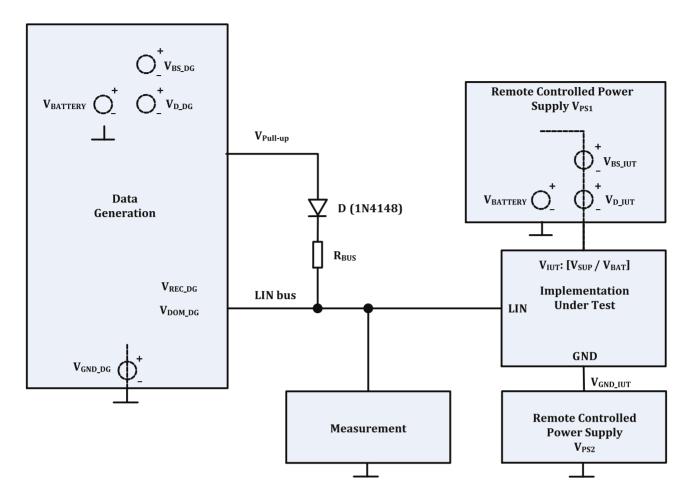

|      | 6.2      | Communication scheme                                                                                    |          |  |

|      |          | 6.2.2 IUT as slave                                                                                      |          |  |

|      |          | 6.2.3 IUT as master                                                                                     |          |  |

|      |          | 6.2.4 IUT class C device                                                                                |          |  |

|      | 6.3      | Test case organization                                                                                  | 42       |  |

|      | 6.4      | Measurement and signal generation — Requirements                                                        |          |  |

|      |          | 6.4.1 Data generation                                                                                   |          |  |

|      | € □      | 6.4.2 Various requirements                                                                              |          |  |

|      | 6.5      | Operational conditions — Calibration                                                                    |          |  |

|      |          | 6.5.2 [EPL-CT 25] Operating voltage range                                                               |          |  |

|      |          | 6.5.3 Threshold voltages                                                                                |          |  |

|      |          | 6.5.4 [EPL-CT 29] Variation of $V_{SUP NON OP} \in [-0.3 \text{ V to } 7.0 \text{ V}]$ , [18 V to 40 V] |          |  |

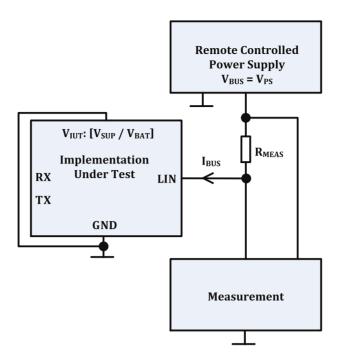

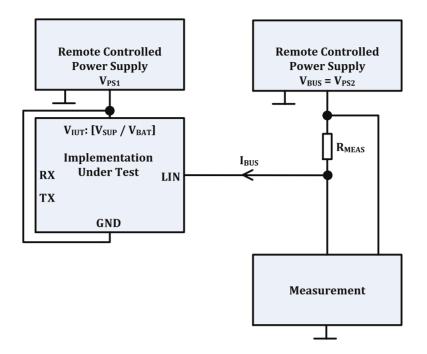

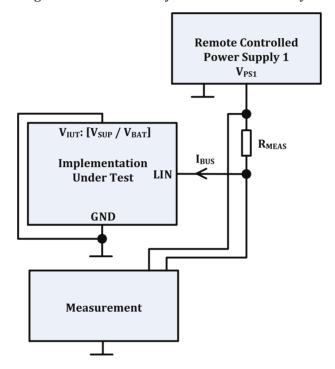

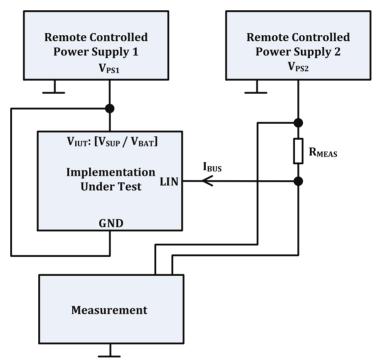

|      |          | 6.5.5 I <sub>BUS</sub> under several conditions                                                         |          |  |

|      |          | 6.5.6 Slope control                                                                                     | 55       |  |

|      |          | 6.5.7 [EPL-CT 35] Propagation delay                                                                     |          |  |

|      |          | 6.5.8 Supply voltage offset                                                                             | 65<br>74 |  |

|      |          | n n M Halling                                                                                           | 7 /1     |  |

# ISO 17987-7:2016(E)

|      |                                                      | 6.5.10     | [EPL-CT 48] Verifying internal capacitance and dynamic interference —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <b>5</b> .0 |

|------|------------------------------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

|      |                                                      | 0          | IUT as slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

|      | 6.6                                                  | -          | on mode termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|      |                                                      | 6.6.1      | General HITT I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |             |

|      |                                                      | 6.6.2      | [EPL-CT 49] Measuring internal resistor — IUT as slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

|      | 6.7                                                  | 6.6.3      | [EPL–CT 50] Measuring internal resistor — IUT as masterest cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

|      |                                                      |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| 7    |                                                      |            | devices with RX and TX access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

|      | 7.1                                                  |            | ecification overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

|      |                                                      | 7.1.1      | Test case organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

|      |                                                      | 7.1.2      | Measurement and signal generation — Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

|      | 7.2                                                  |            | onal conditions — Calibration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

|      |                                                      | 7.2.1      | Electrical input/output, LIN protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

|      |                                                      | 7.2.2      | [EPL-CT 51] Operating voltage range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|      |                                                      | 7.2.3      | Threshold voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |             |

|      |                                                      | 7.2.4      | [EPL-CT 55] Variation of V <sub>SUP_NON_OP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90          |

|      |                                                      | 7.2.5      | I <sub>BUS</sub> under several conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |

|      |                                                      | 7.2.6      | Slope control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |

|      |                                                      | 7.2.7      | Propagation delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

|      |                                                      | 7.2.8      | Supply voltage offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

|      |                                                      | 7.2.9      | Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 112         |

|      |                                                      | 7.2.10     | [EPL-CT 80] Verifying internal capacitance and dynamic interference —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

|      |                                                      |            | IUT as slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |             |

|      | 7.3                                                  |            | on mode termination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |

|      |                                                      | 7.3.1      | General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|      |                                                      | 7.3.2      | [EPL-CT 81] Measuring internal resistor — IUT as slave                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             |

|      |                                                      | 7.3.3      | [EPL-CT 82] Measuring internal resistor — IUT as master                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             |

|      | 7.4                                                  | Static to  | est cases                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 118         |

| 8    | EPL :                                                | 24 V LIN ( | devices without RX and TX access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 121         |

|      | 8.1                                                  |            | ecification overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |

|      | 8.2                                                  |            | ınication scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             |

|      |                                                      | 8.2.1      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |             |