# INTERNATIONAL STANDARD

ISO 11898-2

Second edition 2016-12-15

# Road vehicles — Controller area network (CAN) —

Part 2: **High-speed medium access unit**

Véhicules routiers — Gestionnaire de réseau de communication (CAN) —

Partie 2: Unité d'accès au support à haute vitesse

Reference number ISO 11898-2:2016(E)

# **COPYRIGHT PROTECTED DOCUMENT**

# © ISO 2016, Published in Switzerland

All rights reserved. Unless otherwise specified, no part of this publication may be reproduced or utilized otherwise in any form or by any means, electronic or mechanical, including photocopying, or posting on the internet or an intranet, without prior written permission. Permission can be requested from either ISO at the address below or ISO's member body in the country of the requester.

ISO copyright office Ch. de Blandonnet 8 • CP 401 CH-1214 Vernier, Geneva, Switzerland Tel. +41 22 749 01 11 Fax +41 22 749 09 47 copyright@iso.org www.iso.org

| Coı   | ntent     | S                                                                                | Page |

|-------|-----------|----------------------------------------------------------------------------------|------|

| Fore  | word      |                                                                                  | iv   |

| Intro | oductio   | n                                                                                | v    |

| 1     | Scope     | e                                                                                | 1    |

| 2     | •         | native references                                                                |      |

| _     |           |                                                                                  |      |

| 3     | Term      | s and definitions                                                                | 1    |

| 4     | Symb      | ools and abbreviated terms                                                       | 2    |

| 5     | Func      | tional description of the HS-PMA                                                 | 3    |

|       | 5.1       | General                                                                          |      |

|       | 5.2       | HS-PMA test circuit                                                              | 3    |

|       | 5.3       | Transmitter characteristics                                                      | 4    |

|       | 5.4       | Receiver characteristics                                                         | 8    |

|       | 5.5       | Receiver input resistance                                                        |      |

|       | 5.6       | Transmitter and receiver timing behaviour                                        | 9    |

|       | 5.7       | Maximum ratings of V <sub>CAN_H</sub> , V <sub>CAN_L</sub> and V <sub>Diff</sub> | 11   |

|       | 5.8       | Maximum leakage currents of CAN_H and CAN_L                                      |      |

|       | 5.9       | Wake-up from low-power mode                                                      |      |

|       |           | 5.9.1 Overview                                                                   |      |

|       |           | 5.9.2 Basic wake-up                                                              |      |

|       |           | 5.9.3 Wake-up pattern wake-up                                                    |      |

|       | = 40      | 5.9.4 Selective wake-up                                                          |      |

|       | 5.10      | Bus biasing                                                                      |      |

|       |           | 5.10.1 Overview                                                                  |      |

|       |           | 5.10.2 Normal biasing                                                            |      |

|       |           |                                                                                  |      |

| 6     |           | ormance                                                                          |      |

| Ann   | ex A (inf | formative) ECU and network design                                                | 21   |

| Ann   | ex B (inf | formative) PN physical layer modes                                               | 29   |

| Bibli | iograph   | V                                                                                | 30   |

# **Foreword**

ISO (the International Organization for Standardization) is a worldwide federation of national standards bodies (ISO member bodies). The work of preparing International Standards is normally carried out through ISO technical committees. Each member body interested in a subject for which a technical committee has been established has the right to be represented on that committee. International organizations, governmental and non-governmental, in liaison with ISO, also take part in the work. ISO collaborates closely with the International Electrotechnical Commission (IEC) on all matters of electrotechnical standardization.

The procedures used to develop this document and those intended for its further maintenance are described in the ISO/IEC Directives, Part 1. In particular the different approval criteria needed for the different types of ISO documents should be noted. This document was drafted in accordance with the editorial rules of the ISO/IEC Directives, Part 2 (see <a href="www.iso.org/directives">www.iso.org/directives</a>).

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. ISO shall not be held responsible for identifying any or all such patent rights. Details of any patent rights identified during the development of the document will be in the Introduction and/or on the ISO list of patent declarations received (see <a href="https://www.iso.org/patents">www.iso.org/patents</a>).

Any trade name used in this document is information given for the convenience of users and does not constitute an endorsement.

For an explanation on the meaning of ISO specific terms and expressions related to conformity assessment, as well as information about ISO's adherence to the World Trade Organization (WTO) principles in the Technical Barriers to Trade (TBT) see the following URL: <a href="www.iso.org/iso/foreword.html">www.iso.org/iso/foreword.html</a>.

The committee responsible for this document is ISO/TC 22, *Road vehicles*, Subcommittee SC 31, *Data communication*.

This second edition cancels and replaces the first edition (ISO 11898-2:2003), which has been technically revised, with the following changes:

- max output current on CANH/CANL has been defined (<u>Table 4</u>);

- optional TXD timeout has been defined (<u>Table 7</u>);

- receiver input resistance range has been changed (<u>Table 10</u>);

- Bit timing parameters for CAN FD for up to 2 Mbps have been defined (Table 13);

- Bit timing parameters for CAN FD for up to 5 Mbps have been defined (Table 14);

- content of ISO 11898-5 and ISO 11898-6 has been integrated to ensure there is one single ISO Standard for all HS-PMA implementations;

- selective wake-up (formerly ISO 11898-6) CAN FD tolerance has been defined;

- wake-filter timings (formerly in ISO 11898-5) have been changed (Table 20)

- requirements and assumptions about the PMD sublayer have been shifted to <u>Annex A</u>, to clearly focus on the HS-PMA implementation.

A list of all parts in the ISO 11898 series can be found on the ISO website.

# Introduction

ISO 11898 was first published as one document in 1993. It covered the CAN data link layer as well as the high-speed physical layer. In the reviewed and restructured ISO 11898 series, ISO 11898-1 and ISO 11898-4 defined the CAN protocol and time-triggered CAN (TTCAN) while ISO 11898-2 defines the high-speed physical layer, and ISO 11898-3 defined the low-speed fault tolerant physical layer.

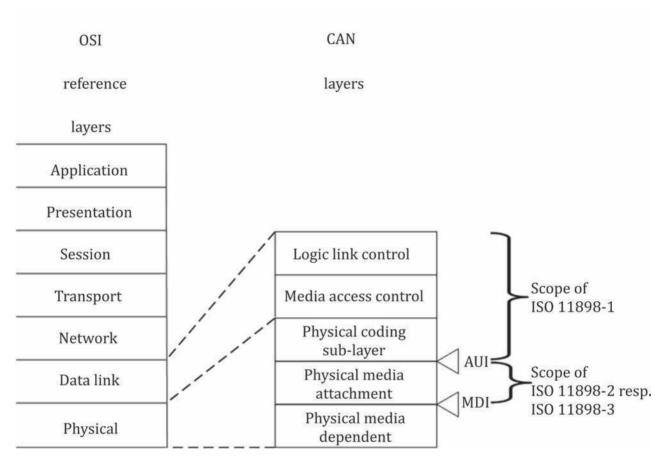

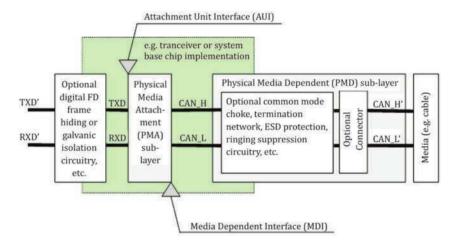

<u>Figure 1</u> shows the relation of the Open System Interconnection (OSI) layers and its sublayers to ISO 11898-1, this document as well as ISO 11898-3.

# Key

AUI attachment unit interface

MDI media dependant interface

OSI open system interconnection

Figure 1 — Overview of ISO 11898 specification series

The International Organization for Standardization (ISO) draws attention to the fact that it is claimed that compliance with this document may involve the use of a patent concerning the selective wake-up function given in 5.9.4.

ISO takes no position concerning the evidence, validity and scope of this patent right.

The holder of this patent right has assured ISO that he/she is willing to negotiate licenses under reasonable and non-discriminatory terms and conditions with applicants throughout the world. In this respect, the statement of the holder of this patent right is registered with ISO. Information may be obtained from the following:

# ISO 11898-2:2016(E)

Audi AG Elmos Semiconductor AG Renesas Electronics Europe GmbH August-Horch-Str. Heinrich-Hertz-Str. 1 Arcadiastr. 10 85045 Ingolstadt 44227 Dortmund 40472 Düsseldorf Germany Germany Germany Freescale Semiconductor Inc. Robert Bosch GmbH **BMW** Group Knorrstr. 147 6501 W. William Canon Drive PO Box 30 02 20 80788 München Austin. Texas 70442 Stuttgart **United States** Germany Germany Continental Teves AG & Co. oHG General Motors Corp. STMicroelectronics Application Guerickestr, 7 30001 VanDyke, Bldg 2-10 GmbH 60488 Frankfurt am Main Bahnhofstrasse 18 Warren, MI 48090-9020 Germany United States of America 85609 Aschheim Dornach Germany

DENSO CORP. NXP BV Volkswagen AG

1-1, Showa-cho, Kariya-shi High Tech Campus 60 PO Box 011/1770

Aichi-ken 448-8661 5656 AG Eindhoven 38436 Wolfsburg

Japan The Netherlands Germany

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights other than those identified above. ISO shall not be held responsible for identifying any or all such patent rights. ISO (www.iso.org/patents) maintains on-line databases of patents relevant to their standards. Users are encouraged to consult the databases for the most up to date information concerning patents.

# Road vehicles — Controller area network (CAN) —

# Part 2:

# High-speed medium access unit

# 1 Scope

This document specifies the high-speed physical media attachment (HS-PMA) of the controller area network (CAN), a serial communication protocol that supports distributed real-time control and multiplexing for use within road vehicles. This includes HS-PMAs without and with low-power mode capability as well as with selective wake-up functionality. The physical media dependant sublayer is not in the scope of this document.

# 2 Normative references

The following documents are referred to in the text in such a way that some or all of their content constitutes requirements of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

ISO 11898-1:2015, Road vehicles — Controller area network (CAN) — Part 1: Data link layer and physical signalling

ISO 16845-2, Road vehicles — Controller area network (CAN) conformance test plan — Part 2: High-speed medium access unit with selective wake-up functionality

#### 3 Terms and definitions

For the purposes of this document, the terms and definitions given in ISO 11898-1 and the following apply.

ISO and IEC maintain terminological databases for use in standardization at the following addresses:

- IEC Electropedia: available at <a href="http://www.electropedia.org/">http://www.electropedia.org/</a>

- ISO Online browsing platform: available at <a href="http://www.iso.org/obp">http://www.iso.org/obp</a>

NOTE See Figure A.1 for a visualization of the definitions.

#### 3.1

#### attachment unit interface

**AUI**

interface between the PCS that is specified in ISO 11898-1 and the PMA that is specified in this document

#### 3.2

## ground

GND

electrical signal ground

#### 3.3

# legacy implementation

HS-PMA implementation that has been released prior to the publication of this document

# ISO 11898-2:2016(E)

#### 3.4

## low-power mode

mode in which the transceiver is not capable of transmitting or receiving messages, except for the purposes of determining if a WUP or WUF is being received

#### 3.5

#### medium attachment unit

#### MAU

unit that comprises the physical media attachment and the media dependent interface

#### 3.6

#### media dependent interface

#### MDI

interface that ensures proper signal transfer between the media and the physical media attachment

#### 3.7

# normal-power mode

mode in which the transceiver is fully capable of transmitting and receiving messages

#### 3.8

# physical coding sublayer

#### **PCS**

sublayer that performs bit encoding/decoding and synchronization

#### 3.9

#### physical media attachment

#### **PMA**

sublayer that converts physical signals into logical signals and vice versa

#### 3.10

#### transceiver

implementation that comprises one or more physical media attachments

# 4 Symbols and abbreviated terms

For the purposes of this document, the symbols and abbreviated terms given in ISO 11898-1 and the following apply. Some of these abbreviations are also defined in ISO 11898-1. If the definition of the term in this document is different from the definition in ISO 11898-1, this definition applies.

AUI attachment unit interface

DLC data length code

EMC electromagnetic compatibility

ESD electro static discharge

GND ground

HS-PMA high-speed PMA

MAU medium attachment unit

MDI media dependent interface

PCS physical coding sublayer

PMA physical media attachment

PMD physical media dependent

WUF wake-up frame

WUP wake-up pattern

# 5 Functional description of the HS-PMA

#### 5.1 General

The HS-PMA comprises one transmitter and one receiving entity. It shall be able to bias the connected physical media, an electric two-wire cable, relative to a common ground. The transmitter entity shall drive a differential voltage between the CAN\_H and CAN\_L signals to signal a logical 0 (dominant) or shall not drive a differential voltage to signal a logical 1 (recessive) to be received by other nodes connected to the very same media. These two signals are the interface to the physical media dependent sublayer.

The HS-PMA shall provide an AUI to the physical coding sublayer as specified in ISO 11898-1. It comprises the TXD and RXD signals as well as the GND signal. The TXD signal receives from the physical coding sublayer the bit-stream to be transmitted on the MDI. The RXD signal transmits to the physical coding sublayer the bit-stream received from the MDI.

Implementations that comprise one or more HS-PMAs shall at least support the normal-power mode of operation. Optionally, a low-power mode may be implemented.

Some of the items specified in the following depend on the operation mode of the (part of the) implementation, in which the HS-PMA is included.

<u>Table 1</u> shows the possible combinations of HS-PMA operating modes and expected behaviour.

Operating mode

Bus biasing behaviour

Transmitter behaviour

Normal

Bus biasing active

Dominant or recessive<sup>a</sup>

Low-power

Bus biasing active or inactive

Recessive

a

Depends on input conditions as described in this document.

Table 1 — HS-PMA operating modes and expected behaviour

All parameters given in this subclause shall be fulfilled throughout the operating temperature range and supply voltage range (if not explicitly specified for unpowered) as specified individually for every HS-PMA implementation.

#### 5.2 HS-PMA test circuit

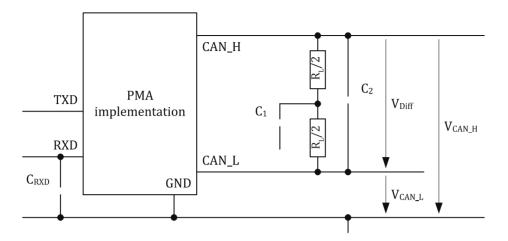

The outputs of the HS-PMA implementation to the CAN signals are called CAN\_H and CAN\_L, TXD is the transmit data input and RXD is the receive data output. Figure 2 shows the external circuit that defines the measurement conditions for all required voltage and current parameters.  $R_L$  represents the effective resistive load (bus load) for an HS-PMA implementation, when used in a network, and  $C_1$  represents an optional split-termination capacitor. The values of  $R_L$  and  $C_1$  vary for different parameters that the HS-PMA implementation needs to meet and are given as condition in Tables 2 to 20.

#### Key

V<sub>Diff</sub> differential voltage between CAN\_H and CAN\_L wires

V<sub>CAN\_H</sub> single ended voltage on CAN\_H wire

$V_{CAN\_L}$  single ended voltage on CAN\_L wire

C<sub>RXD</sub> capacitive load on RXD

Figure 2 — HS-PMA test circuit

#### 5.3 Transmitter characteristics

This subclause specifies the transmitter characteristics of a single HS-PMA implementation under the conditions as depicted in Figure 2; so no other HS-PMA implementations are connected to the media. The behaviour of an HS-PMA implementation connected to other HS-PMAs is outside the scope of this subclause. Refer to A.2 for consideration when multiple HS-PMAs are connected to the same media. The voltages and currents that are required on the CAN\_L and CAN\_H signals are specified in Tables 2 to 6. Table 2 specifies the output characteristics during dominant state.

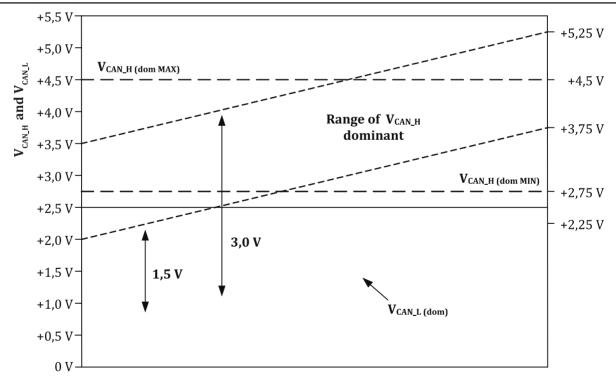

Figure 3 illustrates the voltage range for the dominant state.

Table 2 — HS-PMA dominant output characteristics

|                                                                 |                     |          | Value          |          |                            |  |

|-----------------------------------------------------------------|---------------------|----------|----------------|----------|----------------------------|--|

| Parameter                                                       | Notation            | Min<br>V | Nom<br>V       | Max<br>V | Condition                  |  |

| Single ended voltage on CAN_H                                   | V <sub>CAN_H</sub>  | +2,75    | +3,5           | +4,5     | $R_L = 50 \Omega65 \Omega$ |  |

| Single ended voltage on CAN_L                                   | V <sub>CAN_L</sub>  | +0,5     | +1,5           | +2,25    | $R_L = 50 \Omega65 \Omega$ |  |

| Differential voltage on normal bus load                         | $V_{\mathrm{Diff}}$ | +1,5     | +2,0           | +3,0     | $R_L = 50 \Omega65 \Omega$ |  |

| Differential voltage on effective resistance during arbitration | V <sub>Diff</sub>   | +1,5     | Not<br>defined | +5,0     | $R_L$ = 2 240 $\Omega^a$   |  |

| Optional: Differential voltage on extended bus load range       | $V_{\mathrm{Diff}}$ | +1,4     | +2,0           | +3,3     | $R_L = 45 \Omega70 \Omega$ |  |

$<sup>^</sup>a$   $-2.240~\Omega$  is emulating a situation with up to 32 nodes sending dominant simultaneously. In such case, the effective load resistance for a single node decreases (a node does drive only a part of the nominal bus load). Assuming a MAX  $R_L$  of 70  $\Omega$ , this scenario covers a 32 nodes network. (2.240  $\Omega/70~\Omega$  per node = 32 nodes.)

All requirements in this table apply concurrently. Therefore, not all combinations of  $V_{CAN\_H}$  and  $V_{CAN\_L}$  are compliant with the defined differential voltage (see Figure 3).

Measurement setup according to Figure 2 (only one HS-PMA present):

R<sub>L</sub>, see "Condition" column above

$C_1 = 0 pF (not present)$

$C_2 = 0$  pF (not present)

$C_{RXD} = 0 pF (not present)$

#### Key

V<sub>Diff</sub> differential voltage between CAN\_H and CAN\_L wires

V<sub>CAN\_H</sub> single ended voltage on CAN\_H wire

$V_{\text{CAN\_L}}$  single ended voltage on CAN\_L wire

Figure 3 — Voltage range of  $V_{CAN\_H}$  during dominant state of CAN node, when  $V_{CAN\_L}$  varies from minimum to maximum voltage level (50  $\Omega$  ... 65  $\Omega$  bus load condition)

In order to achieve a level of RF emission that is acceptably low, the transmitter shall meet the driver signal symmetry as required in <u>Table 3</u>.

Table 3 — HS-PMA driver symmetry

| Parameter                    | Notation         | Value |      |      |

|------------------------------|------------------|-------|------|------|

| rai ametei                   | Notation         | Min   | Nom  | Max  |

| Driver symmetry <sup>a</sup> | v <sub>sym</sub> | +0,9  | +1,0 | +1,1 |

$v_{\text{sym}} = (V_{\text{CAN\_H}} + V_{\text{CAN\_L}})/V_{\text{CC}}$ , with  $V_{\text{CC}}$  being the supply voltage of the transmitter.

$v_{sym}$  shall be observed during dominant and recessive state and also during the transition from dominant to recessive and vice versa, while TXD is stimulated by a square wave signal with a frequency that corresponds to the highest bit rate for which the HS-PMA implementation is intended, however, at most 1 MHz (2 Mbit/s) (HS-PMA in normal mode).

Measurement setup according to Figure 2:

$R_L = 60 \Omega \text{ (tolerance } \leq \pm 1 \%)$

$C_1 = 4.7 \text{ nF (tolerance} \le \pm 5 \%)$

$C_2 = 0$  pF (not present)

C<sub>RXD</sub> = 0 pF (not present)

The maximum output current of the transmitter shall be limited according to <u>Table 4</u>.

Table 4 — Maximum HS-PMA driver output current

|                           |                    | Va               | lue              |                                                                         |

|---------------------------|--------------------|------------------|------------------|-------------------------------------------------------------------------|

| Parameter                 | Notation           | <b>Min</b><br>mA | <b>Max</b><br>mA | Condition                                                               |

| Absolute current on CAN_H | I <sub>CAN_H</sub> | not defined      | 115              | $-3 \text{ V} \leq \text{V}_{\text{CAN}_{\text{H}}} \leq +18 \text{ V}$ |

| Absolute current on CAN_L | I <sub>CAN_L</sub> | not defined      | 115              | $-3 \text{ V} \leq \text{V}_{\text{CAN\_L}} \leq +18 \text{ V}$         |

Measurement setup according to Figure 2 with either  $V_{CAN\_H}$  or  $V_{CAN\_L}$  enforced to voltage levels as mentioned in the conditions by connection to an external voltage source, while the HS-PMA is driving the output dominant. The absolute maximum value does not care about the direction in which the current flows.

$R_L > 10^{10} \Omega$  (not present)

$C_1 = 0 pF (not present)$

$C_2 = 0$  pF (not present)

$C_{RXD} = 0 pF (not present)$

NOTE It is expected that the implementation does not stop driving its output dominant when the differential voltage between CAN\_H and CAN\_L is outside the limits given in the Condition column. The minimum output current is implicitly defined in Table 2 and thus can be expected to be above 30 mA.

<u>Table 5</u> specifies the recessive output characteristics when bus biasing is active.

Table 5 — HS-PMA recessive output characteristics, bus biasing active

|                                      |                     | Value    |                 |                 |  |

|--------------------------------------|---------------------|----------|-----------------|-----------------|--|

| Parameter                            | Notation            | Min<br>V | <b>Nom</b><br>V | <b>Max</b><br>V |  |

| Single ended output voltage on CAN_H | V <sub>CAN_H</sub>  | +2,0     | +2,5            | +3,0            |  |

| Single ended output voltage on CAN_L | V <sub>CAN_L</sub>  | +2,0     | +2,5            | +3,0            |  |

| Differential output voltage          | $V_{\mathrm{Diff}}$ | -0,5     | 0               | +0,05           |  |

All requirements in this table apply concurrently. Therefore, not all combinations of  $V_{CAN\_H}$  and  $V_{CAN\_L}$  are compliant with the defined differential output voltage.

Measurement setup according to Figure 2:

$R_L > 10^{10} \Omega$  (not present)

$C_1 = 0 pF (not present)$

$C_2 = 0 pF (not present)$

C<sub>RXD</sub> = 0 pF (not present)

<u>Table 6</u> specifies the recessive output characteristics when bus biasing is inactive.

Table 6 — HS-PMA recessive output characteristics, bus biasing inactive

|                                      |                     | Value    |          |                 |  |

|--------------------------------------|---------------------|----------|----------|-----------------|--|

| Parameter                            | Notation            | Min<br>V | Nom<br>V | <b>Max</b><br>V |  |

| Single ended output voltage on CAN_H | V <sub>CAN_H</sub>  | -0,1     | 0        | +0,1            |  |

| Single ended output voltage on CAN_L | V <sub>CAN_L</sub>  | -0,1     | 0        | +0,1            |  |

| Differential output voltage          | $V_{\mathrm{Diff}}$ | -0,2     | 0        | +0,2            |  |

See <u>5.10</u> to determine when bias shall be inactive.

Measurement setup according to Figure 2:

$R_L > 10^{10} \Omega$  (not present)

$C_1 = 0 pF (not present)$

$C_2 = 0 pF$ (not present)

$C_{RXD} = 0 pF (not present)$

The implementation of an HS-PMA may limit the duration of dominant transmission in order not to prevent other CAN nodes from communication when the TXD input is permanently asserted. The HS-PMA implementation should implement a timeout within the limits specified in <u>Table 7</u>.

Table 7 — Optional HS-PMA transmit dominant timeout

|                                                                                |                  | Value            |                  |  |  |

|--------------------------------------------------------------------------------|------------------|------------------|------------------|--|--|

| Parameter                                                                      | Notation         | <b>Min</b><br>ms | <b>Max</b><br>ms |  |  |

| Transmit dominant timeout <sup>a</sup>                                         | t <sub>dom</sub> | 0,8              | 10,0             |  |  |

| <sup>a</sup> A minimum value of 0,3 ms is accepted for legacy implementations. |                  |                  |                  |  |  |

NOTE There is a relation between the  $t_{dom}$  minimum value and the minimum bit rate. A  $t_{dom}$  minimum value of 0,8 ms accommodates 17 consecutive dominant bits at bit rates greater than or equal to 21,6 kbit/s and 36 consecutive dominant bits at bit rates greater than or equal to 45,8 kbit/s. The value 17 reflects PMA implementation attempts to send a dominant bit and every time sees a recessive level at the receive data input. The value 36 reflects six consecutive error frames when there is a bit error in the last bit of the first five attempts.

## 5.4 Receiver characteristics

The receiver uses the transmitter output signals CAN\_H and CAN\_L as differential input. Figure 2 shows the definition of the voltages at the connections of the HS-PMA's implementation.

When the HS-PMA implementation is in its low-power mode and bus biasing is active, then the recessive and dominant state differential input voltage ranges according to <a href="Table 8">Table 8</a> apply.

Table 8 — HS-PMA static receiver input characteristics, bus biasing active

|                                                  |                     | Value    |          |                                                                                                                                                                                          |

|--------------------------------------------------|---------------------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                        | Notation            | Min<br>V | Max<br>V | Condition                                                                                                                                                                                |

| Recessive state differential input voltage range | $V_{\mathrm{Diff}}$ | -3,0     | +0,5     | $-12.0 \text{ V} \le \text{V}_{\text{CAN}_L} \le +12.0 \text{ V}$<br>$-12.0 \text{ V} \le \text{V}_{\text{CAN}_H} \le +12.0 \text{ V}$                                                   |

| Dominant state differential input voltage range  | $V_{\mathrm{Diff}}$ | +0,9     | +8,0     | $-12,0 \text{ V} \le \text{V}_{CAN\_L} \le +12,0 \text{ V}$<br>$-12,0 \text{ V} \le \text{V}_{CAN\_L} \le +12,0 \text{ V}$<br>$12,0 \text{ V} \le \text{V}_{CAN\_H} \le +12,0 \text{ V}$ |

Measurement setup according <a>Figure 2</a>:

$R_L > 10^{10} \Omega$  (not present)

$C_1 = 0$  pF (not present)

$C_2 = 0 pF (not present)$

$C_{RXD} = 0 pF$ (not present)

NOTE A negative differential voltage may temporarily occur when the HS-PMA is connected to a media in which common mode chokes and/or unterminated stubs are present. The maximum positive differential voltage may temporarily occur when the HS-PMA is connected to a media while more than one HS-PMA is sending dominant and concurrently a ground shift between the sending HS-PMAs is present.

When the HS-PMA implementation is in its low-power mode and bus biasing is inactive, then the recessive and dominant state differential input voltage ranges according to <u>Table 9</u> apply.

Table 9 — HS-PMA static receiver input characteristics, bus biasing inactive

|                                                  |                     | Value    |          |                                                                             |  |

|--------------------------------------------------|---------------------|----------|----------|-----------------------------------------------------------------------------|--|

| Parameter                                        | Notation            | Min<br>V | Max<br>V | Condition                                                                   |  |

| Recessive state differential input voltage range | $V_{\mathrm{Diff}}$ | -3,0     | +0,4     | $-12.0 \text{ V} \le \text{V}_{\text{CAN\_L}} \le +12.0 \text{ V}$          |  |

| Voicage range                                    | <b></b>             |          |          | $-12,0 \text{ V} \le \text{V}_{\text{CAN}_{-}\text{H}} \le +12,0 \text{ V}$ |  |

| Dominant state differential input                | Vn:cc               | +1.15    | +8.0     | $-12.0 \text{ V} \le V_{\text{CAN}_{\perp}\text{L}} \le +12.0 \text{ V}$    |  |

| voltage range                                    | V <sub>Diff</sub>   | +1,15 +  | 10,0     | $-12.0 \text{ V} \le \text{V}_{\text{CAN}_{-}\text{H}} \le +12.0 \text{ V}$ |  |

Measurement setup according Figure 2:

$R_L > 10^{10} \Omega$  (not present)

$C_1 = 0 pF (not present)$

$C_2 = 0 pF (not present)$

$C_{RXD} = 0 pF$ (not present)

NOTE A negative differential voltage may temporarily occur when the HS-PMA is connected to a media in which common mode chokes and/or unterminated stubs are present. The maximum positive differential voltage may temporarily occur when the HS-PMA is connected to a media while more than one HS-PMA is sending dominant and concurrently a ground shift between the sending HS-PMAs is present.

# 5.5 Receiver input resistance

The implementation of an HS-PMA shall have an input resistance according to <u>Table 10</u>. Furthermore, the internal resistance shall meet the requirement given in <u>Table 11</u>. <u>Figure 4</u> shows an equivalent circuit diagram.

Figure~4 - Illustration~of~HS-PMA~internal~differential~input~resistance

Table 10 — HS-PMA receiver input resistance

|                                      |                                            | Va        | lue              |                                                     |  |

|--------------------------------------|--------------------------------------------|-----------|------------------|-----------------------------------------------------|--|

| Parameter                            | Notation                                   | Min<br>kΩ | <b>Max</b><br>kΩ | Condition                                           |  |

| Differential internal resistance     | R <sub>Diff</sub>                          | 12        | 100              | $-2 \text{ V} \leq \text{V}_{\text{CAN}_{\perp}}$ , |  |

| Single ended internal resistance     | R <sub>CAN_H</sub> ,<br>R <sub>CAN_L</sub> | 6         | 50               | $V_{\text{CAN}_{-H}} \le +7 \text{ V}$              |  |

| $R_{Diff} = R_{CAN\_H} + R_{CAN\_L}$ |                                            |           |                  |                                                     |  |

Table 11 — HS-PMA receiver input resistance matching

| Parameter                                                                                                  | Notation | Val   | lue   | Condition                                         |  |

|------------------------------------------------------------------------------------------------------------|----------|-------|-------|---------------------------------------------------|--|

| Parameter                                                                                                  | Notation | Min   | Max   | Condition                                         |  |

| Matching <sup>a</sup> of internal resistance                                                               | $m_R$    | -0,03 | +0,03 | V <sub>CAN_L</sub> , V <sub>CAN_H</sub> :<br>+5 V |  |

| The matching shall be calculated as $m_R = 2 \times (R_{CAN\_H} - R_{CAN\_L})/(R_{CAN\_H} + R_{CAN\_L})$ . |          |       |       |                                                   |  |

# 5.6 Transmitter and receiver timing behaviour

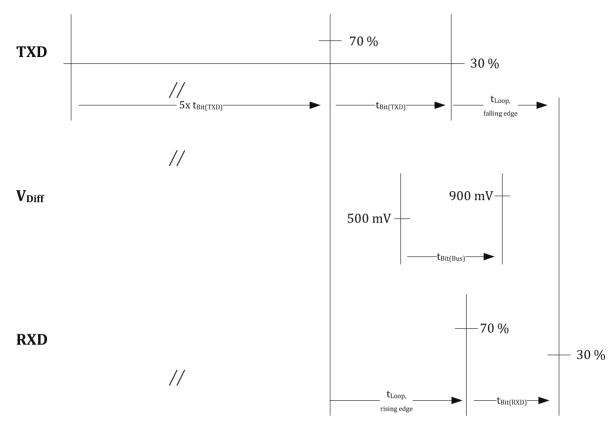

The timing is defined under consideration of the test circuit that is shown in <u>Figure 2</u>. The parameters are given in <u>Tables 12</u>, <u>13</u> and <u>14</u> and shall be measured at the RXD output and TXD input of the HS-PMA implementation as well as on the differential voltage between CAN\_H and CAN\_L.

Figure 5 shows how to measure the timing in the signal traces.

#### Key

$t_{Bit(TXD)} = 1\,000$  ns if the implementation of the HS-PMA supports bit rates of up to 1 Mbit/s

$t_{Bit(TXD)}$  = 500 ns if the implementation of the HS-PMA supports bit rates of up to 2 Mbit/s

$t_{Bit(TXD)}$  = 200 ns if the implementation of the HS-PMA supports bit rates of up to 5 Mbit/s

Figure 5 — HS-PMA implementation timing diagram

Table 12 — HS-PMA implementation loop delay requirement

|                         |            | Value       |     |  |

|-------------------------|------------|-------------|-----|--|

| Parameter               | Notation   | Min         | Max |  |

|                         |            | ns          | ns  |  |

| Loop delay <sup>a</sup> | $t_{Loop}$ | not defined | 255 |  |

<sup>&</sup>lt;sup>a</sup> Time span from signal edge on TXD input to the next signal edge with the same polarity on RXD output, the maximum of delay of both signal edges is to be considered.

Measurement setup according to Figure 2:

$R_L = 60 \Omega \text{ (tolerance } \leq \pm 1 \text{ \%)}$

$C_1 = 0 pF (not present)$

$C_2 = 100 \text{ pF (tolerance } \leq \pm 1 \%)$

C<sub>RXD</sub> = 15 pF (tolerance ≤ ±1 %)

Measurement according to Figure 5:

The input signal on TXD shall have rise and fall times (10 %/90 %) of less than 10 ns.

NOTE Limits for  $t_{Bit(Bus)}$  and  $t_{Bit(RXD)}$  are not defined for intended use with bit rates up to 1 Mbit/s.

Table 13 — Optional HS-PMA implementation data signal timing requirements for use with bit rates above 1 Mbit/s and up to 2 Mbit/s

|                                             |                       | Value |     |  |

|---------------------------------------------|-----------------------|-------|-----|--|

| Parameter                                   | Notation              | Min   | Max |  |

|                                             |                       | ns    | ns  |  |

| Transmitted recessive bit width at 2 Mbit/s | t <sub>Bit(Bus)</sub> | 435   | 530 |  |

| Received recessive bit width at 2 Mbit/s    | t <sub>Bit(RXD)</sub> | 400   | 550 |  |

| Receiver timing symmetry at 2 Mbit/s        | ∆t <sub>Rec</sub> a   | -65   | +40 |  |

a  $\Delta t_{Rec} = t_{Bit(RXD)} - t_{Bit(Bus)}$

All requirements in this table apply concurrently. Therefore, not all combinations of  $t_{Bit(Bus)}$  and  $\Delta t_{Rec}$  are compliant with  $t_{Bit(RXD)}$ .

Measurement setup according to Figure 2:

$R_L = 60 \Omega \text{ (tolerance } \leq \pm 1 \%)$

$C_1 = 0$  pF (not present)

$C_2 = 100 \text{ pF (tolerance } \leq \pm 1 \%)$

$C_{RXD} = 15 \text{ pF (tolerance } \leq \pm 1 \%)$

Measurement according to Figure 5:

The input signal on TXD shall have rise and fall times (10 %/90 %) of less than 10 ns.

NOTE Limits for  $t_{Bit(Bus)}$  and  $t_{Bit(RXD)}$  are not defined for intended use with bit rates up to 1 Mbit/s.

Table 14 — Optional HS-PMA implementation data signal timing requirements for use with bit rates above 2 Mbit/s and up to 5 Mbit/s

|                                                       |                         | Value |     |  |

|-------------------------------------------------------|-------------------------|-------|-----|--|

| Parameter                                             | Notation                | Min   | Max |  |

|                                                       |                         | ns    | ns  |  |

| Transmitted recessive bit width at 5 Mbit/s, intended | t <sub>Bit(Bus)</sub>   | 155   | 210 |  |

| Received recessive bit width at 5 Mbit/s              | $t_{Bit(RXD)}$          | 120   | 220 |  |

| Receiver timing symmetry at 5 Mbit/s                  | $\Delta t_{ m Rec}{}^a$ | -45   | +15 |  |

a  $\Delta t_{Rec} = t_{Bit(RXD)} - t_{Bit(Bus)}$

All requirements in this table apply concurrently. Therefore, not all combinations of  $t_{Bit(Bus)}$  and  $\Delta t_{Rec}$  are compliant with  $t_{Bit(RXD)}$ .

Measurement setup according to Figure 2:

$R_L = 60 \Omega \text{ (tolerance } \leq \pm 1 \text{ \%)}$

$C_1 = 0 pF (not present)$

$C_2 = 100 \text{ pF (tolerance } \leq \pm 1 \%)$

$C_{RXD} = 15 \text{ pF (tolerance } \leq \pm 1 \%)$

Measurement according to Figure 5:

The input signal on TXD shall have rise and fall times (10 %/90 %) of less than 10 ns.

$NOTE \quad Limits \ for \ t_{Bit(Bus)} \ and \ t_{Bit(RXD)} \ are \ not \ defined \ for \ intended \ use \ with \ bit \ rates \ up \ to \ 1 \ Mbit/s.$

# 5.7 Maximum ratings of $V_{CAN\_H}$ , $V_{CAN\_L}$ and $V_{Diff}$

Table 15 reflects upper and lower limit static voltages, which may be connected to CAN\_H and CAN\_L without causing damage, while V<sub>Diff</sub> stays within in its own maximum rating range.

Table 15 — HS-PMA maximum ratings of  $V_{CAN\_H}$ ,  $V_{CAN\_L}$  and  $V_{Diff}$

|                                                                           |                                            | Value    |                 |  |

|---------------------------------------------------------------------------|--------------------------------------------|----------|-----------------|--|

| Parameter                                                                 | Notation                                   | Min<br>V | <b>Max</b><br>V |  |

| Maximum rating V <sub>Diff</sub> <sup>a</sup>                             | V <sub>Diff</sub>                          | -5,0     | +10,0           |  |

| General maximum rating $V_{CAN\_H}$ and $V_{CAN\_L}$                      | V <sub>CAN_H</sub> ,<br>V <sub>CAN_L</sub> | -27,0    | +40,0           |  |

| Optional: $ Extended \ maximum \ rating \ V_{CAN\_H} \ and \ V_{CAN\_L} $ | V <sub>CAN_H</sub> ,<br>V <sub>CAN_L</sub> | -58,0    | +58,0           |  |

$<sup>^{\</sup>text{a}}$   $\,$  This is required regardless whether general or extended maximum rating for  $V_{CAN\_H}$  and  $V_{CAN\_L}$  is fulfilled.

Applies to HS-PMA implementation powered and unpowered conditions. Applies to transmit data input de-asserted and transmit data becomes asserted while CAN\_H or/and CAN\_L connected to a fixed voltage.

The maximum rating for  $V_{Diff}$  excludes that all combinations of  $V_{CAN\_H}$  and  $V_{CAN\_L}$  are compliant to this document.  $V_{Diff}$  =  $V_{CAN\_H}$  –  $V_{CAN\_L}$ , see Figure 2.

# 5.8 Maximum leakage currents of CAN\_H and CAN\_L

An unpowered HS-PMA implementation shall not disturb the communication of other HS-PMAs that are connected to the same media. The required maximum leakage currents are given in <u>Table 16</u>.

Table 16 — HS-PMA maximum leakage currents on CAN\_H and CAN\_L, unpowered

|                                                                                                                 |                                            | Value            |                  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------|------------------|--|--|--|

| Parameter                                                                                                       | Notation                                   | <b>Min</b><br>μΑ | <b>Max</b><br>μA |  |  |  |

| Leakage current on CAN_H, CAN_L                                                                                 | I <sub>CAN_H</sub> ,<br>I <sub>CAN_L</sub> | -10              | +10              |  |  |  |

| $V_{\text{CAN\_H}} = 5 \text{ V}$ , $V_{\text{CAN\_L}} = 5 \text{ V}$ , all supply inputs are connected to GND. |                                            |                  |                  |  |  |  |

| Positive currents are flowing into the implementation.                                                          |                                            |                  |                  |  |  |  |

# 5.9 Wake-up from low-power mode

#### 5.9.1 Overview

When an implementation comprising one or more HS-PMAs implements a low-power mode, the HS-PMA shall be able to signal a wake-up event to its implementation. <u>Table 17</u> lists the required wake-up mechanism for defined types of HS-PMA implementations.

Table 17 — HS-PMA wake-up implementations

| Type of HS-PMA implementation                                                  | Required wake-up mechanism                                      |

|--------------------------------------------------------------------------------|-----------------------------------------------------------------|

| CAN wake-up, implementations without low-power mode                            | No wake-up                                                      |

| CAN wake-up, implementations with low-power mode but without selective wake-up | Either basic wake-up or wake-up pattern (WUP) wake-up           |

| CAN wake-up, implementations with selective wake-up                            | Selective wake-up frame (WUF) and wake-up pattern (WUP) wake-up |

When more than one wake-up mechanism is implemented in an HS-PMA, the wake-up mechanism to be used shall be configurable.

#### 5.9.2 Basic wake-up

Upon receiving once a dominant state for duration of at least t<sub>Filter</sub>, a wake-up event shall happen.

# 5.9.3 Wake-up pattern wake-up

Upon receiving two consecutive dominant states each for duration of at least  $t_{Filter}$ , separated by a recessive state with a duration of at least  $t_{Filter}$ , a wake-up event shall happen. This method follows the description of activating the bus biasing as described in 5.10.3.

## 5.9.4 Selective wake-up

#### **5.9.4.1** General

Upon detection of a wake-up frame (WUF), a wake-up event shall happen. Decoding of CAN frames in either CBFF or CEFF and acceptance as a WUF is done by the HS-PMA. If enabled, decoding of CAN frames shall be possible in normal- and low-power modes. The acceptance procedure is described in detail in the following subclauses.

After the bias reaction time,  $t_{Bias}$ , has elapsed, the implementation may ignore up to four (or up to eight when bit rate higher than 500 kbit/s) frames in CBFF and CEFF and shall not ignore any following frame in CBFF and CEFF.

In case of erroneous communication, the HS-PMA shall signal a wake-up upon or after an overflow of the internal error counter.

# 5.9.4.2 Behaviour during transitions between normal- to low-power modes

If selective wake-up is enabled prior to the mode change and the HS-PMA is not anymore ignoring frames, decoding of CAN data and remote frames shall also be supported during mode transitions, which have frame detection IP enabled. If the received frame is a valid WUF, the transceiver shall indicate a wake-up. If enabled, decoding of CAN data shall be possible in normal- and low-power mode.

# 5.9.4.3 Bit decoding

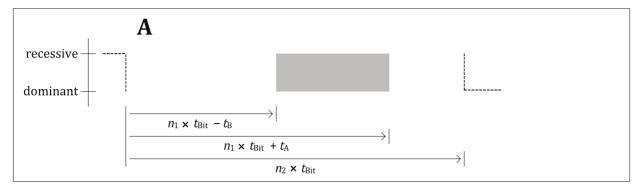

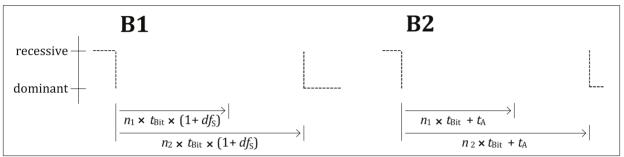

A received Classical CAN frame shall be decoded correctly when the timing of the differential voltage between CAN\_H and CAN\_L complies with one of the two following types of signals:

- the bit stream consists of multiple instances of the signal shape A (to handle ringing);

- the bit stream can be assembled out of multiple instances of the signal shape B1 and one instance of signal shape B2 (to handle sender clock tolerance and loss of arbitration).

These two types of signals are specified in Figure 6.

#### Kev

- $n_1$  number of consecutive dominant bits  $\{1, 2, 3, 4, 5\}$

- $n_2$  number of bits between two falling edges {2, 3, ..., 10};  $n_2 > n_1$

- $t_A$  0  $\leq t_A \leq$  55 % of  $t_{Bit}$  (product specific higher maximum values for  $t_A$  are allowed)

- $t_{\rm B}$  0  $\leq$   $t_{\rm B}$   $\leq$  5 % of  $t_{\rm Bit}$  (product specific higher maximum values for  $t_{\rm B}$  are allowed)

- $t_{\rm Bit}$  nominal bit time

- $df_{

m S}$  transceivers according to this document shall tolerate sender clock frequency deviations up to at least 0,5 %

NOTE Often used values for  $t_{Bit}$  are 2 µs, 4 µs and 8 µs.

Figure 6 — Signal shape A and B of V<sub>Diff</sub> for bit reception

Edges in the time span from " $n_1 \times t_{Bit} - t_B$ " to " $n_1 \times t_{Bit} + t_A$ " of signal shape A shall be ignored and shall not cause decoding errors.

#### 5.9.4.4 Wake-up frame evaluation

If all of the following conditions are met, a valid Classical CAN frame shall be accepted as a valid WUF.

- a) The received frame is a Classical CAN data frame when DLC matching [see c)] is not disabled. The frame may also be a remote frame when DLC matching is disabled.

- b) The ID (as defined in ISO 11898-1:2015, 8.4.2.2) of the received Classical CAN frame is exactly matching a configured ID (in the HS-PMA implementation) in the relevant bit positions. The relevant bit positions are given by an ID-mask (in the HS-PMA implementation). See the mechanism illustrated in 5.9.4.7.

- c) The DLC (as defined in ISO 11898-1:2015, 8.4.2.4) of the received Classical CAN data frame is exactly matching a configured DLC. See the mechanism illustrated in <u>5.9.4.8</u>. Optionally, this DLC matching condition may be disabled by configuration in the HS-PMA implementation.

- d) When the DLC is greater than 0 and DLC matching is enabled, the data field (as defined in ISO 11898-1:2015, 8.4.2.5) of the received frame has at least one bit set in a bit position which corresponds to a set bit in the configured data mask. See the mechanism illustrated in 5.9.4.9.

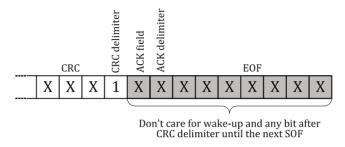

e) A correct cyclic redundancy check (CRC) has been received, including a recessive CRC delimiter, and no error (according to ISO 11898-1:2015, 10.11) is detected prior to the acknowledgement (ACK) Slot. Figure 7 depicts the bits, which are considered as "don't care".

NOTE There is no requirement for the SRR bit to be received as dominant in CEFF to recognize the frame as a valid WUF.

Figure 7 — Don't care bits for frame decoding

#### 5.9.4.5 Frame error counter mechanism

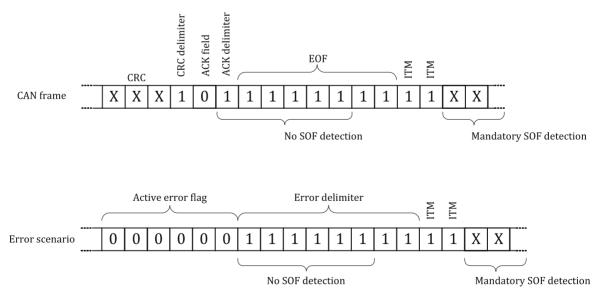

Upon activating the selective wake-up function (e.g. by a connected host controller) and also on expiration of  $t_{\rm Silence}$ , the counter for erroneous CAN frames shall be set to zero. The initial value of the counter is zero. This counter shall be incremented by one when a bit stuffing, CRC or CRC delimiter form error (according to ISO 11898-1) is detected. If a Classical CAN frame has been received, which is valid according to the definition in 5.9.4.4, and the counter is not zero, then the counter shall be decremented by one. Dominant bits between the CRC delimiter and the end of the intermission field shall not increase the frame error counter.

On each increment or decrement of this counter, the decoder unit in the HS-PMA shall wait for  $n_{Bits\_idle}$  recessive bits before considering a dominant bit as a start of frame. Figure 8 depicts the position of the mandatory start of frame (SOF) detection when a Classical CAN frame was received and in case of an error scenario.

Figure 8 — Mandatory SOF detection after Classical CAN frames and error scenarios

A wake-up shall happen immediately or upon the next received WUP when the counter has reached a threshold value. The default threshold value is 32, other values might be configurable.

## ISO 11898-2:2016(E)

Up to four (or up to eight when bit rate >500 kbit/s) consecutive Classical CAN data and remote frames that start after the bias reaction time,  $t_{Bias}$ , has elapsed might be either ignored (no error counter increase of failure) or judged as erroneous (error counter increase even in case of no error).

Receiving a frame in CEFF with non-nominal reserved bits (SRR, r0) shall not lead to an increase of the error counter.

## 5.9.4.6 Tolerance to CAN FD frames (optional)

After receiving a recessive FDF bit followed by a dominant res bit, the decoder unit in the HS-PMA shall wait for  $n_{Bits\_idle}$  recessive bits before considering a further dominant bit as a start of frame. Figure 8 depicts the position of the mandatory SOF detection when a CAN FD data frame was received and in case of an error scenario. Table 18 specifies the valid range for  $n_{Bits\_idle}$ .

The behaviour, when the FDF bit is received recessively and the following bit position is also received recessively, is outside the scope of this document.

One of the following bitfilter options shall be implemented to support different combinations of arbitration and data phase bit rates.

- Bitfilter option 1: A data phase bit rate less or equal to four times the arbitration bit rate or 2 Mbit/s, whichever is lower, shall be supported.

- Bitfilter option 2: A data bit rate less or equal to ten times the arbitration bit rate or 5 Mbit/s, whichever is lower, shall be supported.

Dominant signals less than or equal to the minimum of pBitfilter of the arbitration bit time in duration shall not be considered to be a valid bit and shall not restart the recessive bit counter. Dominant signals longer than or equal to maximum of pBitfilter of the arbitration bit time in duration shall restart the recessive bit counter. Table 19 specifies pBitfilter depending on the chosen bitfilter option as percentage of the arbitration bit time.

Table 18 — Number of recessive bit before next SOF

| Parameter                                                   | Notation               | Va  | lue |

|-------------------------------------------------------------|------------------------|-----|-----|

| Farameter                                                   | Notation               | Min | Max |

| Number of recessive bits before a new SOF shall be accepted | n <sub>Bits_idle</sub> | 6   | 10  |

Table 19 — Bitfilter in CAN FD data phase

| Parameter                              | Notation                      | Value |        |  |

|----------------------------------------|-------------------------------|-------|--------|--|

| rai ametei                             | Notation                      | Min   | Max    |  |

| CAN FD data phase bitfilter (option 1) | pBitfilter <sub>option1</sub> | 5 %   | 17,5 % |  |

| CAN FD data phase bitfilter (option 2) | pBitfilter <sub>option2</sub> | 2,5 % | 8,75 % |  |

#### 5.9.4.7 Wake-up frame ID evaluation

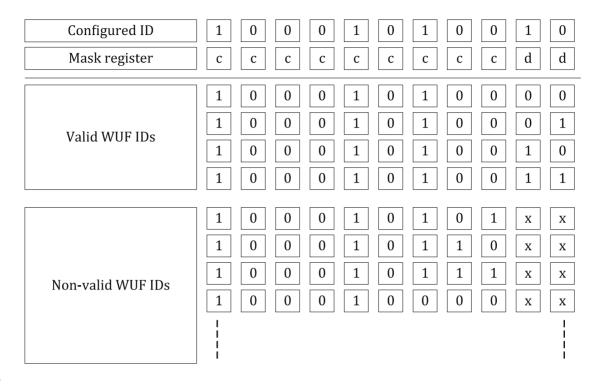

A CAN-ID mask mechanism shall be supported to exclude ID-bits from comparison. 11-bit and 29-bit CAN-IDs and ID-masks shall be supported. The user selects whether a WUF has to appear in CBFF or CEFF. The IDE bit is not part of the ID-mask. It has to be evaluated in any case.

All masked ID-bits except "don't care" shall match exactly the configured ID-bits. If the masked ID-bits are configured as "don't care", then both "1" and "0" shall be accepted.

The masking mechanism is implementation dependent.

Figure 9 shows an example for valid WUF IDs corresponding to the ID-mask register.

#### Key

- d don't care

- c care

Figure 9 — Example for ID masking mechanism

# 5.9.4.8 Wake-up frame DLC evaluation

If the DLC matching condition is enabled, then a Classical CAN frame can only be a valid WUF when the DLC of the received frame matches exactly the configured DLC.

If the DLC matching condition is disabled, then the DLC and data field are not evaluated and a Classical CAN frame is already a valid WUF when the identifier matches (see <u>5.9.4.7</u>) and the CRC is correct.

#### 5.9.4.9 Wake-up frame data field evaluation

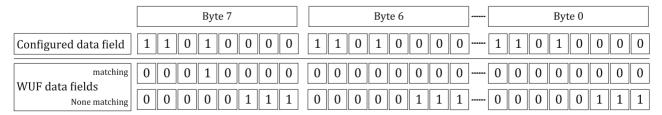

If the DLC matching condition is enabled, then a Classical CAN frame can only be a valid WUF if at least one logic 1 bit within the data field of the received WUF matches to a logic 1 bit of the data field within the configured WUF.

If the DLC matching condition is disabled, then the DLC and data field are not evaluated and a Classical CAN frame is already a valid WUF when the identifier matches (see <u>5.9.4.7</u>) and the CRC is correct.

Figure 10 shows an example with a non-matching and a matching ID field.

Figure 10 — Example of the data field within a received Classical CAN data frame

# ISO 11898-2:2016(E)

With this mechanism, it is possible to wake-up up to 64 independent groups of ECUs with only one wake-up frame.

# 5.10 Bus biasing

#### 5.10.1 Overview

The HS-PMA implementation shall bias CAN H and CAN L according to Tables 5 and 6.

When the HS-PMA implementation features a low-power mode and selective wake-up, automatic voltage biasing is required. For all other implementation, either normal biasing or automatic voltage biasing shall be implemented.

# 5.10.2 Normal biasing

Normal biasing means bus biasing is active in normal mode and inactive in low-power mode.

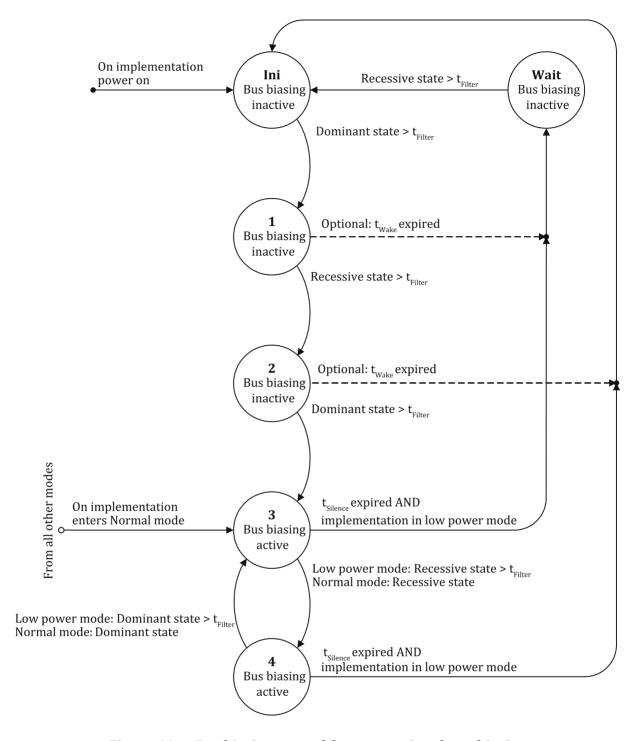

# 5.10.3 Automatic voltage biasing

Automatic voltage biasing means bus biasing is active in normal mode and is controlled by the differential voltage between CAN\_H and CAN\_L in low-power mode. The following state machine illustrates the mechanism.

Figure 11 — Bus biasing control for automatic voltage biasing

The state machine in Figure 11 defines the bus biasing behaviour for all operation modes. When entering state 1, the optional timer,  $t_{Wake}$ , shall be reset and restarted; when entering state 3 or 4, the timer,  $t_{Silence}$ , shall be reset and restarted.

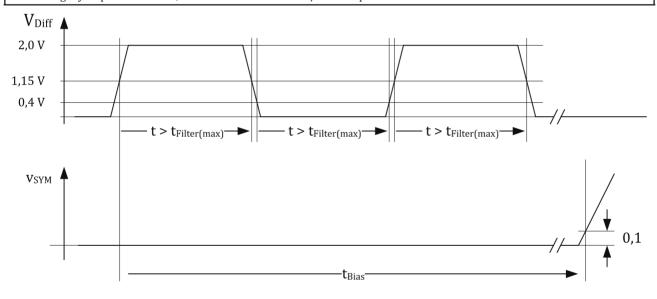

<u>Table 20</u> specifies the bus biasing control timings and <u>Figure 12</u> the bias reaction time.

|                                             | Value                |                       |                       |                                                                                                                                                                             |  |

|---------------------------------------------|----------------------|-----------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                   | Notation             | Min                   | Max                   | Condition                                                                                                                                                                   |  |

|                                             |                      | μs                    | μs                    |                                                                                                                                                                             |  |

| CAN activity filter time, long <sup>a</sup> | t <sub>Filter</sub>  | 0,5                   | 5,0                   | Bus voltages according to <u>Table A.2</u>                                                                                                                                  |  |

| CAN activity filter time, shortb            | t <sub>Filter</sub>  | 0,15                  | 1,8                   | Bus voltages according to <u>Table A.2</u>                                                                                                                                  |  |

| Wake-up timeout <sup>c</sup>                | t <sub>Wake</sub>    | 800,0                 | 10 000,0              | Optional timeout parameter                                                                                                                                                  |  |

| Timeout for bus inactivity                  | t <sub>Silence</sub> | 0,6 × 10 <sup>6</sup> | 1,2 × 10 <sup>6</sup> | Timer is reset and restarted, when bus changes from dominant to recessive or vice versa.                                                                                    |  |

| Bus bias reaction time                      | t <sub>Bias</sub>    | Not<br>defined        | 250,0                 | Measured from the start of a dominant-<br>recessive-dominant sequence (each<br>phase 6 $\mu$ s) until $v_{sym} \ge 0,1$ . See Figure 12<br>$v_{sym}$ as defined in Table 3. |  |

Table 20 — HS-PMA bus biasing control timings

For legacy implementations, a minimum value of 350 us is acceptable.

Figure 12 — Test signal definition for bias reaction time measurement

# 6 Conformance

The conformance test case definition and measurement setups to derive the parameters are outside the scope of this document. A conformance test plan is given in ISO 16845-2.

For an implementation to be compliant with this document, the HS-PMA implementation shall comply with all mandatory specifications and values given in this document. If optional specifications and values are implemented, they shall comply too. More information is given in <u>A.4</u>.

The implementation does not need to meet this timing, in case the "CAN activity filter time, short" is met. It should be noted that the maximum filter time has an impact to the suitable wake-up messages, especially at high bit rates. For example, a 500 kbit/s system, a message shall carry at least three similar bit levels in a row in order to safely pass the wake-up filter. Shorter filter time implementations might increase the risk for unwanted bus wake-ups due to noise. The specified range is a compromise between robustness against unwanted wake-ups and freedom in message selection.

b The implementation does not need to meet this timing, in case the "CAN activity filter time, long" is met.

# Annex A

(informative)

# ECU and network design

# A.1 Implementation options

This clause specifies the physical media attachment sublayer. It can be implemented in a standalone CAN transceiver chip or in a system basis chip comprising additional functionality, e.g voltage regulators, wake-up logic and watchdog. These implementations can also provide additional functions, which are outside the scope of this document.

<u>Figure A.1</u> shows an optional digital processing unit, which hides CAN FD data frames to the CAN data link layer implementation. Another optional feature is a galvanic isolation. Note that these optional functions cause some timing delays.

Figure A.1 — Optional functions in this document, compliant transceiver and their relation to the OSI sublayers

<u>Figure A.1</u> shows also some optional functionality belonging to the physical media dependent sublayer. This includes, for example, a ringing suppression circuitry. These optional functionalities can improve the signal integrity of the analogue signals on the bus wires (CAN\_L' and CAN\_H').

NOTE These functions can have impacts on the EMC performance.

When implementing a ringing suppression circuitry, the differential internal resistance is typically  $120 \Omega$  in a bit-width interval [ $t_{Bit(Bus)}$ ] after the dominant-to-recessive edge.

# A.2 Expectations on a CAN network

This clause outlines which input voltages on  $V_{CAN\_L}$  and  $V_{CAN\_H}$  are recommended for proper operation of HS-PMA implementations connected to a media.

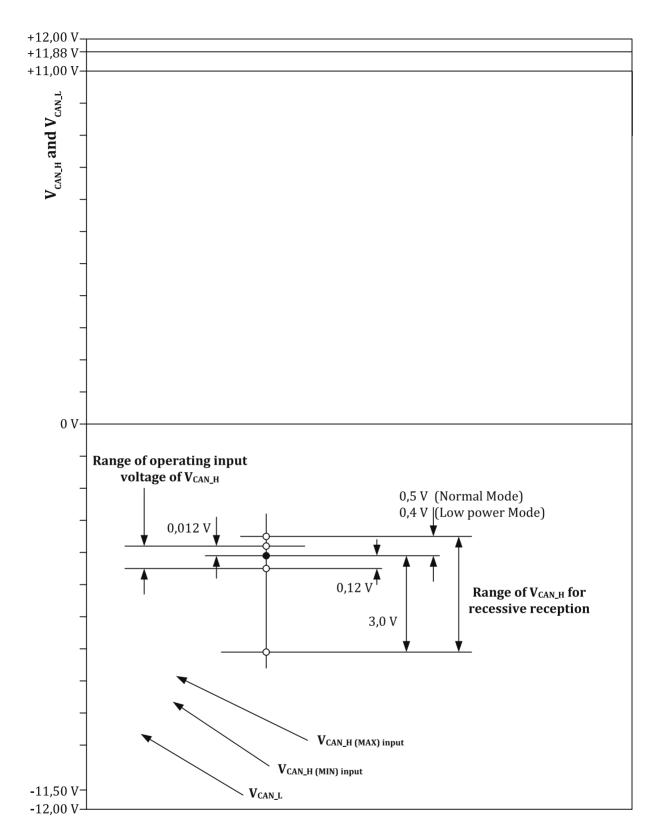

<u>Table A.1</u> shows the CAN interface voltage parameters for the reception of recessive state.

Table A.1 — Input voltage parameters for reception of recessive state

|                            |                     |          | Value    |          |                                                                 |  |

|----------------------------|---------------------|----------|----------|----------|-----------------------------------------------------------------|--|

| Parameter                  | Notation            | Min<br>V | Nom<br>V | Max<br>V | Condition                                                       |  |

| Operating input voltage    | V <sub>CAN_H</sub>  | -12,0    | +2,5     | +12,0    | Measured with respect to the individual ground of each CAN node |  |

|                            | V <sub>CAN_L</sub>  | -12,0    | +2,5     | +12,0    |                                                                 |  |

| Differential input voltage | $V_{\mathrm{Diff}}$ | -3,0     | 0        | +0,012   | Measured at each CAN node connected to the media                |  |

The differential input voltage is determined by a combination of the recessive state output voltages of the individual CAN nodes present. Therefore,  $V_{\rm Diff}$  is approximately zero.

Figure A.3 shows the voltages  $V_{CAN\_H}$  and  $V_{CAN\_L}$  in their interdependency during recessive state.

Figure A.2 — Valid voltage range of  $V_{CAN\_H}$  for recessive state, when  $V_{CAN\_L}$  varies from minimum to maximum common mode range

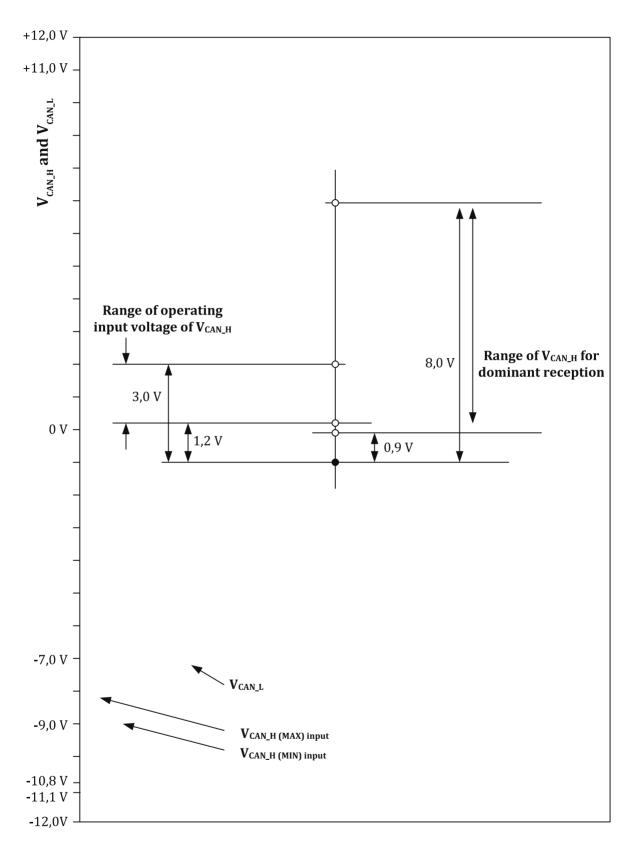

<u>Table A.2</u> shows the CAN interface voltage parameters for reception of dominant state.

Table A.2 — Input voltage parameters for reception of dominant state

|                                   |                    | Value    |          |          |                                                  |

|-----------------------------------|--------------------|----------|----------|----------|--------------------------------------------------|

| Parameter                         | Notation           | Min<br>V | Nom<br>V | Max<br>V | Condition                                        |

| Common mode voltage               | V <sub>CAN_H</sub> | -10,8    | +3,5     | +12,0    | Measured with respect to the                     |

| Common mode voltage               | V <sub>CAN_L</sub> | -12,0    | +1,5     | +10,8    | individual ground of each CAN node               |

| Differential voltage <sup>a</sup> | V <sub>Diff</sub>  | +1,2     | +2,0     | +3,0     | Measured at each CAN node connected to the media |

a Normal bus load range, no arbitration.

The minimum value of  $V_{CAN\_H}$  is determined by the minimum value of  $V_{CAN\_L}$  plus the minimum value of  $V_{Diff}$ . The maximum value of  $V_{CAN\_L}$  is determined by the maximum value of  $V_{CAN\_H}$  minus the minimum value of  $V_{Diff}$ .

The bus load increases as CAN nodes are added to the media by  $R_{Diff}$ . Consequently,  $V_{Diff}$  decreases. The minimum value of  $V_{Diff}$  determines the number of CAN nodes allowed to be connected to the media. Also, the cable material, length and cross-section between the HS-PMA implementations, as well as connectors, impact the  $V_{Diff}$  that can be measured at the receiving HS-PMA's input.

Figure A.4 shows the voltages  $V_{CAN\_H}$  and  $V_{CAN\_L}$  in their interdependency during dominant state according to Table A.2.

Table A.3 — Input voltage parameters for reception of dominant state during arbitration

|                      |                    | Value    |                 |                                                                 |  |

|----------------------|--------------------|----------|-----------------|-----------------------------------------------------------------|--|

| Parameter            | Notation           | Min<br>V | <b>Max</b><br>V | Condition                                                       |  |

| Common mode voltage  | V <sub>CAN_H</sub> | -10,8    | +12,0           | Measured with respect to the individual ground of each CAN node |  |

|                      | V <sub>CAN_L</sub> | -12,0    | +10,8           | _                                                               |  |

| Differential voltage | V <sub>Diff</sub>  | +1,2     | +8,0            | Measured at each CA node connected to the media                 |  |

The minimum value of  $V_{CAN\_H}$  is determined by the minimum value of  $V_{CAN\_L}$  plus the minimum value of  $V_{Diff}$ . The maximum value of  $V_{CAN\_L}$  is determined by the maximum value of  $V_{CAN\_H}$  minus the minimum value of  $V_{Diff}$ .

The maximum value of V<sub>Diff</sub> is specified by the upper limit during arbitration plus a ground shift of up to 3 V.

Figure A.3 — Valid voltage range of  $V_{CAN\_H}$  for monitoring dominant state, when  $V_{CAN\_L}$  varies from minimum to maximum common mode range during normal mode, arbitration free scenario

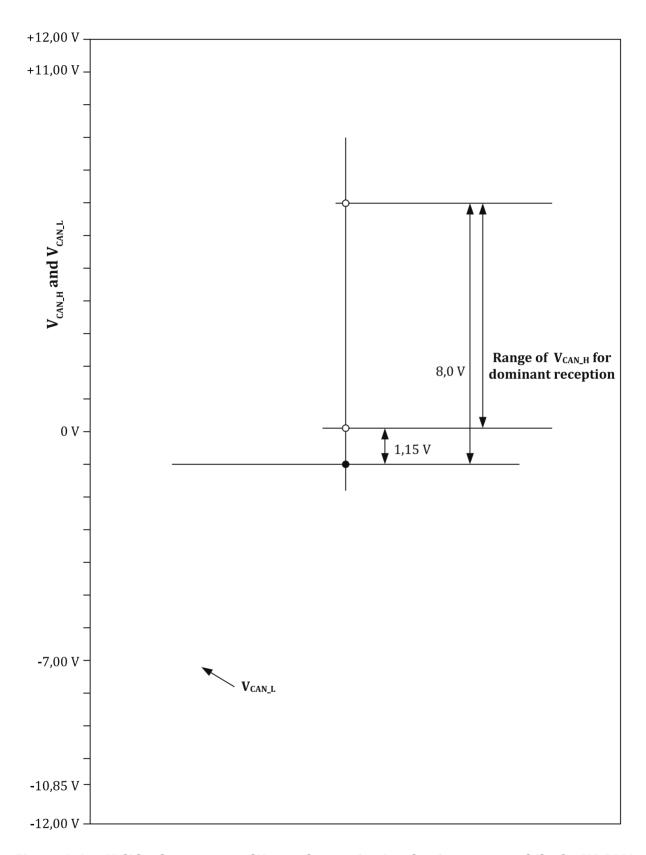

Figure A.4 — Valid voltage range of  $V_{CAN\_H}$  for monitoring dominant state while the HS-PMA is not connected to the media, when  $V_{CAN\_L}$  varies from minimum to maximum common mode range during low-power mode

# A.3 Expectations on a datasheet of an HS-PMA implementation

The datasheet needs to state the maximum supported bit rate according to the bit time requirements given in  $\frac{14}{12}$  and  $\frac{14}{12}$ .

The datasheet needs to state the supported arbitration bit rates for partial networking in case selective wake-up functionality is implemented.

In case the implemented selective wake-up functionality is tolerant to frames in FBFF and FEFF, the maximum supported ratio of data bit rate and arbitration bit rate needs to be stated, as well as the absolute maximum data bit rate.

The datasheet needs to state which of the functionalities classified as optional in this document are implemented in the particular HS-PMA implementation (e.g. extended bus load range, transmit dominant timeout, CAN activity filter time, etc.)

# A.4 Overview of optional features and implementation choices

This document offers the following options for an HS-PMA. <u>Table A.4</u> lists functional options that are specified in this document.

No. Option Reference 1 Support of extended bus load range 5.3, Table 2 2 Transmit dominant timeout function 5.3, Table 7 3 Support of bit rates above 1 Mbit/s and up to 2 Mbit/s 5.6, Table 13 Support of bit rates above 2 Mbit/s and up to 5 Mbit/s 5.6, Table 14 5 Support of extended maximum ratings for CAN\_H and CAN\_L 5.7, Table 15 Support of wake-up 5.9, Table 17

Table A.4 — Optional features and functions

In case the HS-PMA implementation implements low-power mode(s), then a wake-up mechanism according to <u>Table 18</u> needs to be implemented. Each Wake-up mechanism has options and alternatives, which are summarized in <u>Tables A.5</u>, <u>A.6</u>, <u>A.7</u> and <u>A.8</u>.

| Table A.5 —  | Alternative  | timings | within             | the wake-un | features |

|--------------|--------------|---------|--------------------|-------------|----------|

| I abic A.J — | AILLIIIALIVL | ummes   | VV I L I I I I I I | the want-up | icatuics |

| No.  | Alternative 1                         | Alternative 2         | Alternative 3                                                            | Reference                    |  |

|------|---------------------------------------|-----------------------|--------------------------------------------------------------------------|------------------------------|--|

| 1    | CAN activity filter time, long        | -                     | CAN activity filter time,<br>long and CAN activity<br>filter time, short | <u>5.9</u> , <u>Table 17</u> |  |

| 2    | Wake-up timeout, shorta               | Wake-up timeout, long | No wake-up timeout                                                       | <u>5.9, Table 17</u>         |  |

| a Or | a Only applicable for legacy devices. |                       |                                                                          |                              |  |

Table A.6 — Options of the selective wake-up functions

| No. | Option                            | Reference        |

|-----|-----------------------------------|------------------|

| 1   | Support of disabling DLC matching | <u>5.9.4.4</u> . |

$Table \ A.7 - Alternative \ for \ handling \ of \ CAN \ FD \ frames \ by \ the \ selective \ wake-up \ function$

| No. | Alternative 1            | Alternative 2              | Alternative 3                | Reference      |

|-----|--------------------------|----------------------------|------------------------------|----------------|

|     | No tolerance             | Tolerance to CAN FD frames | Tolerance to CAN FD frames   | <u>5.9.4.6</u> |

|     | (not recommended for new |                            | with bit rate ratio of up to |                |

|     | designs)                 | 1:4 or maximum 2 Mbit/s in | 1:10 or maximum 5 Mbit/s in  |                |

|     |                          | data phase                 | data phase                   |                |

# ISO 11898-2:2016(E)

# Table A.8 — Alternatives for TXD dominant timeout function

| No.                                   | Alternative 1 | Alternative 2               | Alternative 3 | Reference  |  |

|---------------------------------------|---------------|-----------------------------|---------------|------------|--|

| 1                                     | No timeout    | Timeout, short <sup>a</sup> | Timeout, long | <u>5.3</u> |  |

| a Only applicable for legacy devices. |               |                             |               |            |  |

# Annex B

(informative)

# PN physical layer modes

<u>Table B.1</u> provides a summary of features of PN physical layer implementations.

Table B.1 — PN physical layer features

| PN-capable<br>FD-tolerant<br>transceiver<br>mode                                                      | End of frame detection for<br>CAN FD messages (glitch<br>filtering), from FDF = reces-<br>sive to EOF, when selective<br>wake-up is enabled | Bus wake-<br>up detec-<br>tion | Frame<br>error<br>counting | Frame error<br>counter value                | t <sub>Silence</sub><br>functionality |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------|---------------------------------------------|---------------------------------------|

| Normal                                                                                                | Required when frame error counting active/Not required when frame error counting inactive                                                   | WUF<br>detection<br>required   | Optional                   | Counting up/<br>down active<br>or no change | Active or inactive                    |

| Transition<br>normal to<br>low-power                                                                  | Required when frame error counting active/Not required when frame error counting inactive                                                   | WUF<br>detection<br>required   | Optional                   | Counting up/<br>down active<br>or no change | Active or inactive                    |

| Low-power<br>and t <sub>Silence</sub> not<br>expired and bus<br>biasing active                        | Required                                                                                                                                    | WUF<br>detection<br>required   | Required                   | Counting up/<br>down active                 | Active                                |

| Low-power and t <sub>Silence</sub> expired                                                            | Inactive                                                                                                                                    | WUP<br>detection<br>required   | Inactive                   | Set value to zero                           | Inactive                              |

| Low-power and t <sub>Silence</sub> not expired and bus biasing inactive (from WUP to bus bias active) | Inactive                                                                                                                                    | WUP<br>detection<br>required   | Inactive                   | No change                                   | Active                                |

| Transition<br>low-power to<br>normal                                                                  | Required when frame error counting active/Not required when frame error counting inactive                                                   | WUF detection optional         | Optional                   | Counting up/<br>down active<br>or no change | Active or inactive                    |

# **Bibliography**

- [1] ISO/IEC 7498-1, Information technology Open Systems Interconnection Basic Reference Model: The Basic Model

- [2] ISO 11898-3, Road vehicles Controller area network (CAN) Part 3: Low-speed, fault-tolerant, medium-dependent interface

- [3] ISO 11898-4, Road vehicles Controller area network (CAN) Part 4: Time-triggered communication

- [4] ISO 11898-5, Road vehicles Controller area network (CAN) Part 5: High-speed medium access unit with low-power mode

- [5] ISO 11898-6, Road vehicles Controller area network (CAN) Part 6: High-speed medium access unit with selective wake-up functionality