# PD IEC/TS 62578:2015

# **BSI Standards Publication**

Power electronics systems and equipment — Operation conditions and characteristics of active infeed converter (AIC) applications including design recommendations for their emission values below 150 kHz

# **National foreword**

This Published Document is the UK implementation of IEC/TS 62578:2015. It supersedes DD IEC/TS 62578:2009 which is withdrawn.

The UK participation in its preparation was entrusted to Technical Committee PEL/22, Power electronics.

A list of organizations represented on this committee can be obtained on request to its secretary.

This publication does not purport to include all the necessary provisions of a contract. Users are responsible for its correct application.

© The British Standards Institution 2015. Published by BSI Standards Limited 2015

ISBN 978 0 580 75477 7 ICS 29.200

Compliance with a British Standard cannot confer immunity from legal obligations.

This Published Document was published under the authority of the Standards Policy and Strategy Committee on 30 April 2015.

Amendments/corrigenda issued since publication

Date Text affected

# **IEC TS 62578**

Edition 2.0 2015-04

# TECHNICAL SPECIFICATION

# SPECIFICATION TECHNIQUE

Power electronics systems and equipment – Operation conditions and characteristics of active infeed converter (AIC) applications including design recommendations for their emission values below 150 kHz

Systèmes et équipements électroniques de puissance – Conditions de fonctionnement et caractéristiques des convertisseurs à alimentation active (AIC), y compris les recommandations de conception pour leurs valeurs d'émission inférieures à 150 kHz

INTERNATIONAL

ELECTROTECHNICAL

COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

ICS 29.200 ISBN 978-2-8322-2585-1

Warning! Make sure that you obtained this publication from an authorized distributor. Attention! Veuillez vous assurer que vous avez obtenu cette publication via un distributeur agréé.

# CONTENTS

| Ε( | DREWC          | PRD                                                                                        | 9  |

|----|----------------|--------------------------------------------------------------------------------------------|----|

| IN | TRODU          | JCTION                                                                                     | 11 |

| 1  | Scop           | e                                                                                          | 12 |

| 2  | Norm           | native references                                                                          | 12 |

| 3  | Term           | is and definitions                                                                         | 13 |

| 4  | Gene           | eral system characteristics of PWM active infeed converters connected to the               |    |

|    |                | er supply network                                                                          | 18 |

|    | 4.1            | General                                                                                    | 18 |

|    | 4.2            | Basic topologies and operating principles                                                  | 18 |

|    | 4.2.1          | General                                                                                    | 18 |

|    | 4.2.2          | Operating principles                                                                       | 18 |

|    | 4.2.3          | Equivalent circuit of an AIC                                                               | 20 |

|    | 4.2.4          | Filters                                                                                    | 21 |

|    | 4.2.5          | Pulse patterns                                                                             | 21 |

|    | 4.2.6          | Control methods                                                                            | 22 |

|    | 4.2.7          |                                                                                            |    |

|    | 4.2.8          | <b>-</b>                                                                                   |    |

|    | 4.3            | AIC rating                                                                                 |    |

|    | 4.3.1          | General                                                                                    | 23 |

|    | 4.3.2          | 3                                                                                          |    |

|    | 4.3.3          | 9                                                                                          |    |

|    | 4.3.4          | 3                                                                                          |    |

| 5  | Elect          | romagnetic compatibility (EMC) considerations for the use of AICs                          | 24 |

|    | 5.1            | General                                                                                    | 24 |

|    | 5.2            | Low-frequency phenomena (<150 kHz)                                                         | 25 |

|    | 5.2.1          | General                                                                                    | 25 |

|    | 5.2.2          |                                                                                            | 25 |

|    | 5.2.3          | supply network                                                                             |    |

|    | 5.2.4          |                                                                                            | 21 |

|    | 3.2.4          | 2 kHz to 20 kHz                                                                            | 32 |

|    | 5.2.5          | Proposal of an appropriate line impedance stabilisation network (LISN) from 2 kHz to 9 kHz | 37 |

|    | 5.2.6          | Effects on industrial equipment in the frequency band 2 kHz to 9 kHz                       | 41 |

|    | 5.3            | High-frequency phenomena (> 150 kHz)                                                       | 44 |

|    | 5.3.1          | General                                                                                    | 44 |

|    | 5.3.2          | Mitigation of distortion                                                                   | 44 |

|    | 5.3.3          | Immunity                                                                                   | 44 |

|    | 5.3.4          | EMI filters                                                                                | 44 |

|    | 5.4            | Audible noise effects                                                                      | 45 |

|    | 5.5            | Leakage currents                                                                           | 45 |

|    | 5.6            | Aspects of system integration and dedicated tests                                          | 45 |

| 6  |                | acteristics of a PWM active infeed converter of voltage source type and two                |    |

|    | level topology |                                                                                            |    |

|    | 6.1            | General                                                                                    |    |

|    | 6.2            | General function, basic circuit topologies                                                 | 46 |

| 6.3  | B Power control                                                                        | 49 |

|------|----------------------------------------------------------------------------------------|----|

| 6.4  | Dynamic performance                                                                    | 50 |

| 6.5  | Desired non-sinusoidal line currents                                                   | 50 |

| 6.6  | Undesired non-sinusoidal line currents                                                 | 50 |

| 6.7  | Availability and system aspects                                                        | 51 |

| 6.8  | Operation in active filter mode                                                        | 52 |

|      | Characteristics of a PWM active infeed converter of voltage source type and three      |    |

| le   | evel topology                                                                          | 52 |

| 7.1  | General function, basic circuit topologies                                             | 52 |

| 7.2  | Power control                                                                          | 53 |

| 7.3  | B Dynamic performance                                                                  | 53 |

| 7.4  | Undesired non-sinusoidal line currents                                                 | 54 |

| 7.5  | 5 Availability and system aspects                                                      | 54 |

|      | Characteristics of a PWM Active Infeed Converter of Voltage Source Type and            |    |

| N    | Multi Level Topology                                                                   |    |

| 8.1  | General function, basic circuit topologies                                             | 55 |

| 8.2  | Power control                                                                          | 56 |

| 8.3  | B Dynamic performance                                                                  | 57 |

| 8.4  | Power supply network distortion                                                        | 57 |

| 8.5  | Availability and system aspects                                                        | 57 |

| 9 (  | Characteristics of a F3E AIC of the Voltage Source Type                                | 58 |

| 9.1  | General function, basic circuit topologies                                             | 58 |

| 9.2  | Power control and line side filter                                                     | 59 |

| 9.3  | B Dynamic performance                                                                  | 61 |

| 9.4  | Harmonic current                                                                       | 61 |

| 10 ( | Characteristics of an AIC of Voltage Source Type in Pulse Chopper Topology             | 62 |

| 10   | .1 General                                                                             | 62 |

| 10   |                                                                                        |    |

| 10   | ·                                                                                      |    |

| 10   |                                                                                        |    |

| 10   |                                                                                        |    |

| 10   | •                                                                                      |    |

| 10   |                                                                                        |    |

| _    | Characteristics of a two level PWM AIC of current source type (CSC)                    |    |

| 11   |                                                                                        |    |

| 11   |                                                                                        |    |

| 11   |                                                                                        |    |

| 11   |                                                                                        |    |

| 11   |                                                                                        |    |

| 11   |                                                                                        |    |

| 11   | ·                                                                                      |    |

|      | x A (informative)                                                                      |    |

|      | ·                                                                                      |    |

| A.   |                                                                                        |    |

|      | A.1.1 General                                                                          |    |

|      | A.1.2 Considerations of control methods                                                | 69 |

| F    | A.1.3 Short-circuit ride through functionality for decentralized power infeed with AIC | 70 |

| /    | 1.1.4 Fault ride through mode                                                          | 70 |

| A.2        | Examples of practical realized AIC applications                                                                                                               | 72  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A.2.       | 1 AIC of current source type (CSC)                                                                                                                            | 72  |

| A.2.2      | Active infeed converter with commutation on the d.c. side (reactive power converter)                                                                          | 74  |

| A.3        | Details concerning two level and multi-level AICs in VSC Topology                                                                                             |     |

| A.3.       |                                                                                                                                                               |     |

| A.3.2      |                                                                                                                                                               |     |

| A.3.3      | •                                                                                                                                                             |     |

| A.4        | Basic transfer rules between voltage and current distortion of an AIC                                                                                         |     |

| A.5        | Examples of the influence of AICs to the voltage quality                                                                                                      |     |

| A.6        | Withstand capability of power capacitors towards distortion in the range of 2 kHz to 9 kHz                                                                    |     |

| A.6.       |                                                                                                                                                               |     |

| A.6.2      | 2 Catalogue information about permissible harmonic load                                                                                                       | 82  |

| A.6.3      | Frequency boundaries for permissible distortion levels                                                                                                        | 82  |

| A.6.4      | Frequency spectrum of active infeed converters                                                                                                                | 83  |

| A.6.5      | 5 Conclusion                                                                                                                                                  | 84  |

| A.7        | Impact of additional AIC filter measures in the range of 2 kHz to 9 kHz                                                                                       | 85  |

| A.7.       | 1 General                                                                                                                                                     | 85  |

| A.7.2      | 2 Example of a PDS constellation (AIC and CSI)                                                                                                                | 86  |

| A.7.3      | 3 Conclusion                                                                                                                                                  | 88  |

| A.8        | Example of the power supply network impedance measurement                                                                                                     | 89  |

| A.8.       | 1 General                                                                                                                                                     | 89  |

| A.8.2      | 2 Basic principle of measurement                                                                                                                              | 89  |

| A.8.3      | 3 Harmonic component injection methods for measurement                                                                                                        | 90  |

| A.8.4      | 4 Harmonic current generation by disturbing device                                                                                                            | 90  |

| A.8.5      | References based on current injection by disturbance (Method A)                                                                                               | 90  |

| A.8.6      | References based on sinusoidal single frequency injection (Method B)                                                                                          | 92  |

| Annex B    | (informative)                                                                                                                                                 | 94  |

| B.1        | Basic considerations for design recommendations of AICs in the range of 2 kHz to 9 kHz                                                                        | 94  |

| B.1.1      | 1 Overview                                                                                                                                                    | 94  |

| B.1.2      | 2 General                                                                                                                                                     | 94  |

| B.1.3      | Withstand capability of power capacitors connected to the power supply network and recommendation for the compatibility in the frequency range 2 kHz to 9 kHz | 95  |

| B.1.4      |                                                                                                                                                               |     |

| B.1.5      |                                                                                                                                                               |     |

| B.1.6      |                                                                                                                                                               |     |

| B.1.7      |                                                                                                                                                               |     |

| B.1.8      | 8 AIC appropriate technical and economical amount                                                                                                             | 100 |

| B.1.9      | 9 Frequency range from 2 kHz to 9 kHz                                                                                                                         | 101 |

| B.2        | Design recommendations for conducted emission of low voltage AICs in the reasonable context of higher frequencies between 9 kHz and 150 kHz                   | 102 |

| B.2.       | 1 General                                                                                                                                                     | 102 |

| B.2.2      | 2 Data collection results                                                                                                                                     | 103 |

| B.2.3      | 3 Conclusions                                                                                                                                                 | 105 |

| Bibliograp | phy                                                                                                                                                           | 107 |

| Figure 1 – AIC in VSC topology, basic structure                                                                                                                                                                                                     | 19 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 – AIC in CSC topology, basic structure                                                                                                                                                                                                     | 19 |

| Figure 3 – Equivalent circuit for the interaction of the power supply network with an AIC $\dots$                                                                                                                                                   | 20 |

| Figure 4 – Voltage and current vectors of line and converter at fundamental frequency for different load conditions                                                                                                                                 | 23 |

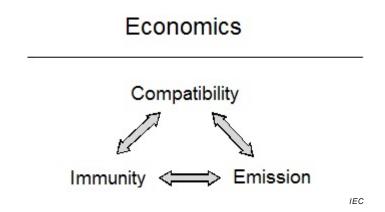

| Figure 5 – The basic issues of EMC as tools of economics                                                                                                                                                                                            | 24 |

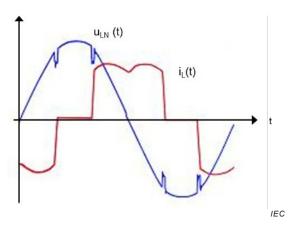

| Figure 6 – Typical power supply network current $i_L(t)$ and voltage $u_{LN}(t)$ of a phase controlled converter with d.c. output and inductive smoothing                                                                                           | 26 |

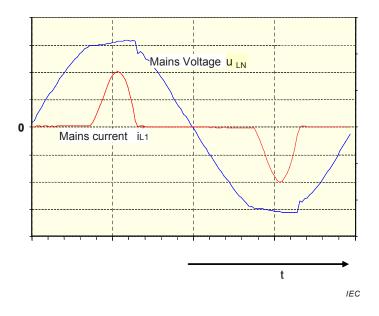

| Figure 7 – Typical power supply network current $i_L(t)$ and voltage $u_{LN}(t)$ of an uncontrolled converter with d.c. output and capacitive smoothing                                                                                             | 26 |

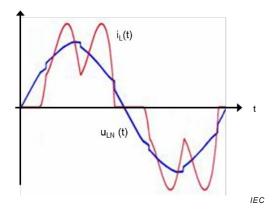

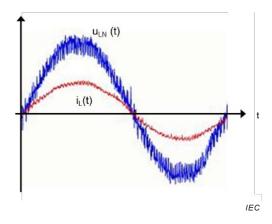

| Figure 8 – Typical power supply network current $i_L(t)$ and voltage $u_{LN}(t)$ of an AIC realized by a PWM Converter with capacitive smoothing without additional filters                                                                         | 26 |

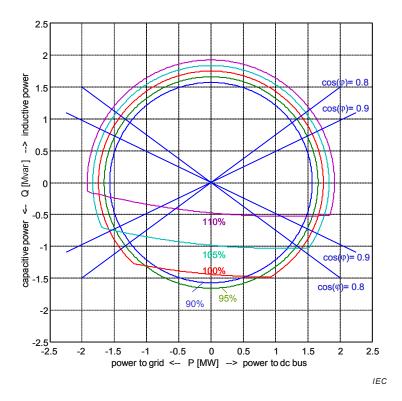

| Figure 9 – Example of attainable active and reactive power of the AIC (VSC-type) at different line to line voltages in per unit (with 10 % combined transformer and filter inductor short-circuit voltage, X/R ratio = 10/1, d.c. voltage = 6,5 kV) | 27 |

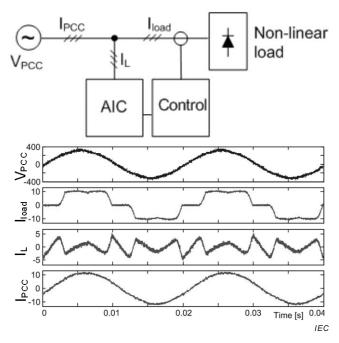

| Figure 10 – Principle of compensating given harmonics in the power supply system by using an AIC and suitable control simultaneously                                                                                                                | 28 |

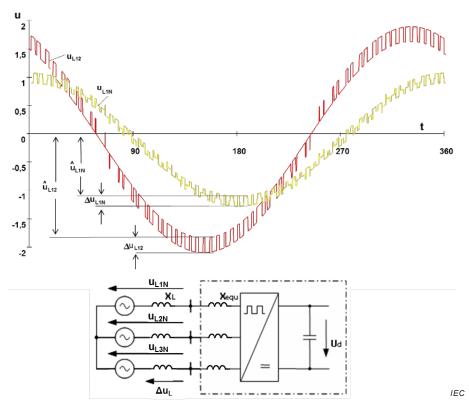

| Figure 11 – Typical Voltage Distortion in the Line-to-Line and Line-to-Neutral Voltage generated by an AIC without additional filters (u in % and t in degrees)                                                                                     | 29 |

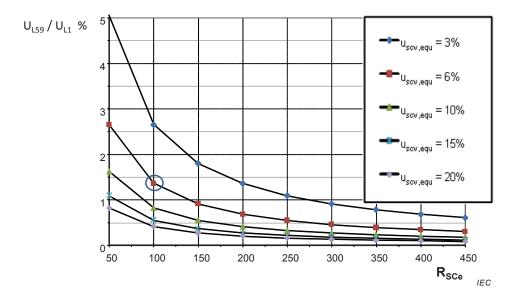

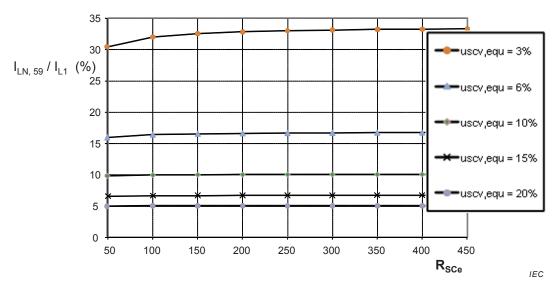

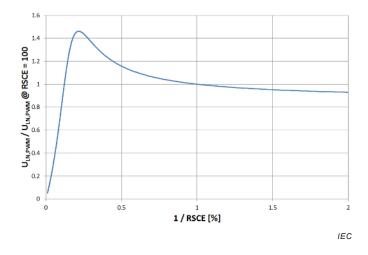

| Figure 12 – Basic characteristic of the relative voltage distortion (59th harmonic) of one AIC operated at a pulse frequency of 3 kHz versus $R_{\sf SCe}$ with the line impedance according to 5.2.4                                               | 30 |

| Figure 13 – Basic characteristic of the relative current emission (59th harmonic) of one AIC at a pulse frequency of 3 kHz versus $R_{SCe}$ with the line impedance according to 5.2.4                                                              | 31 |

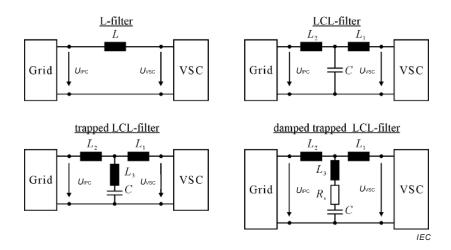

| Figure 14 – Single phase electric circuit of the three commonly used differential mode passive line filter topologies for VSC and one example for passive damping                                                                                   | 31 |

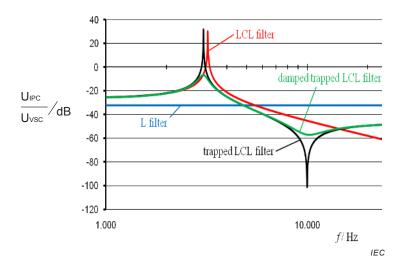

| Figure 15 – Example of the attenuation of the VSC line to line voltage to the line to line voltage at the IPC with state of the art differential mode passive line filter topologies                                                                | 32 |

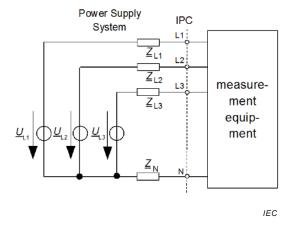

| Figure 16 – Connection of the power supply network impedance measurement equipment                                                                                                                                                                  | 33 |

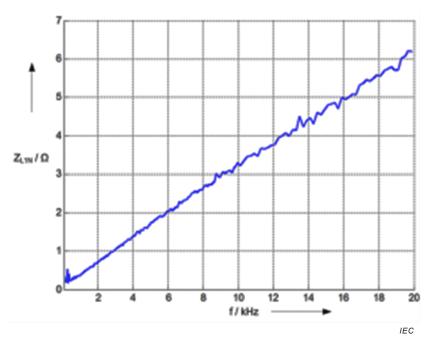

| Figure 17 – Example of the measured impedance of a low-voltage transformer under no load condition S = 630 kVA, $u_{\rm k}$ = 6,08 %                                                                                                                | 34 |

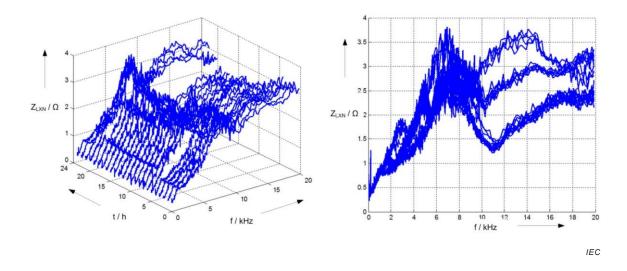

| Figure 18 – Measured variation of the power supply network impedance over the course of a day at one location                                                                                                                                       | 34 |

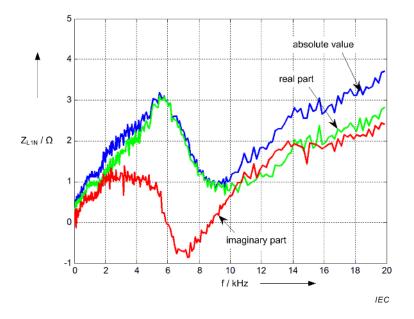

| Figure 19 – Power supply network impedance with partly negative imaginary part                                                                                                                                                                      | 35 |

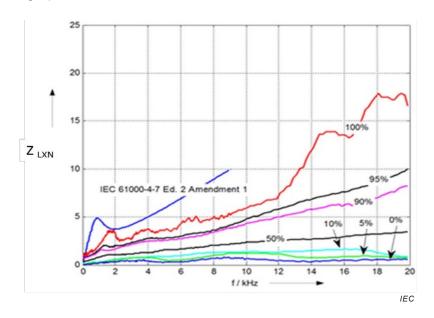

| Figure 20 – Distribution of power system impedance (measured between phase and neutral conductor) in low-voltage systems versus frequency                                                                                                           | 35 |

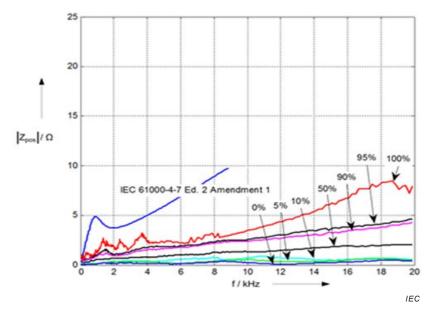

| Figure 21 – Statistical distribution of positive-sequence impedance versus frequency in low-voltage power supply networks                                                                                                                           | 37 |

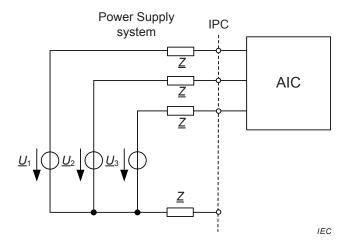

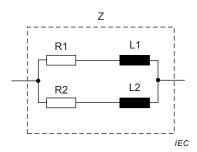

| Figure 22 – Equivalent circuit describing the power supply network impedance                                                                                                                                                                        | 38 |

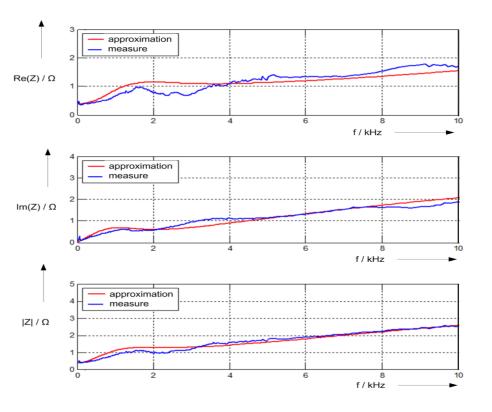

| Figure 23 – Circuit topology for power system simulation                                                                                                                                                                                            | 38 |

| Figure 24 – Approximated and measured 50 % impedance curve                                                                                                                                                                                          | 39 |

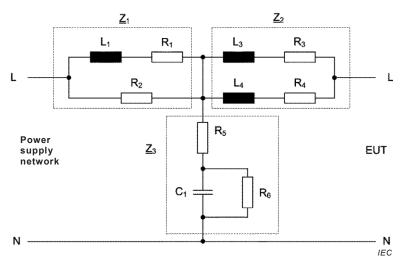

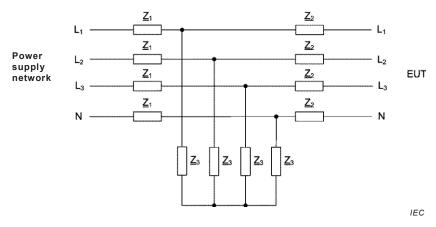

| Figure 25 – Single phase circuit topology according to IEC 61000-4-7+ used for line impedance stabilisation network                                                                                                                                 | 40 |

| Figure 26 – Three-phase circuit topology for the line impedance stabilisation network                                                                                                                                                               | 41 |

| Figure 27 – Impedance variation in the 90 % curve of the LISN described in Figure 26                                                                                                                                                                | 41 |

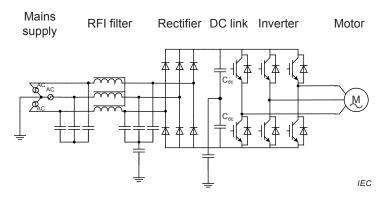

| Figure 28 – PDS with large d.c. capacitance                                                                                                                                                                                                         | 43 |

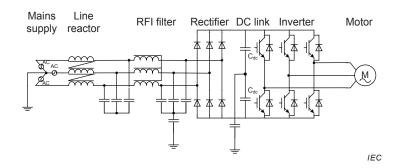

| Figure 29 – PDS with large capacitance and line inductor                                                                                                                                                                    | 43 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 30 – PDS with a large d.c. capacitance and inductors in the d.c. link                                                                                                                                                | 43 |

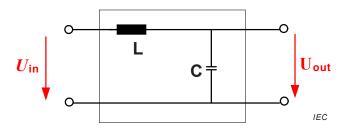

| Figure 31 – Basic EMI filter topology                                                                                                                                                                                       | 45 |

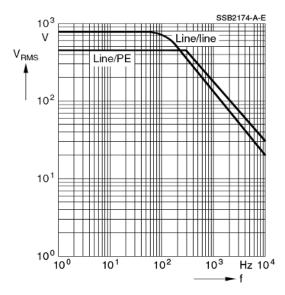

| Figure 32 – Block diagram of a PDS with high frequency EMI filter system                                                                                                                                                    | 45 |

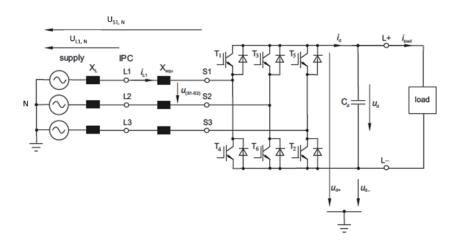

| Figure 33 – Basic illustration of a topology of a two level PWM voltage source AIC                                                                                                                                          | 47 |

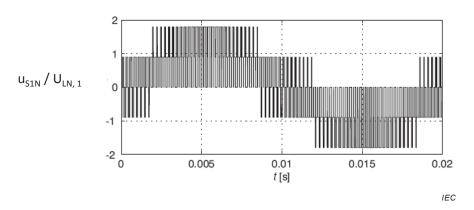

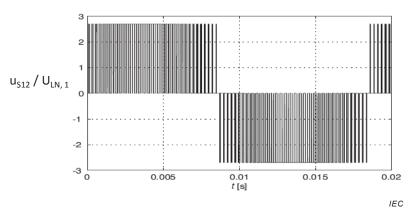

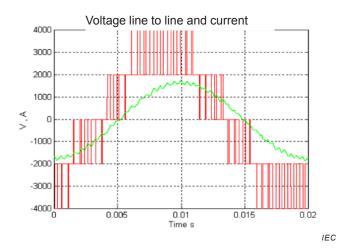

| Figure 34 – Typical waveforms of voltages $u_{\rm S1N}$ / $U_{\rm LN,~1}$ and voltage $u_{\rm S12}$ / $U_{\rm LN,~1}$ at pulse frequency of 4 kHz                                                                           | 48 |

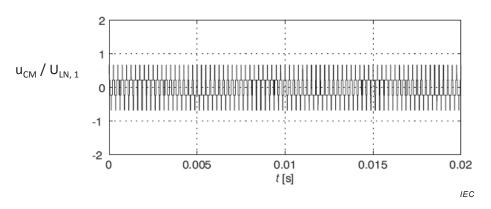

| Figure 35 – Typical waveforms of the common mode voltage $u_{\rm CM}$ / $U_{\rm LN,1}$ at pulse frequency of 4 kHz. Power supply frequency is 50Hz                                                                          | 48 |

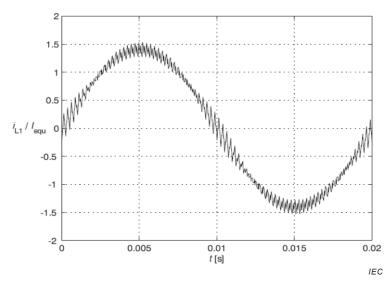

| Figure 36 – Waveform of the current $i_{L1}$ / $I_{equ}$ at pulse frequency of 4 kHz, relative impedance of $u_{SCV,equ}$ = 6 %                                                                                             | 49 |

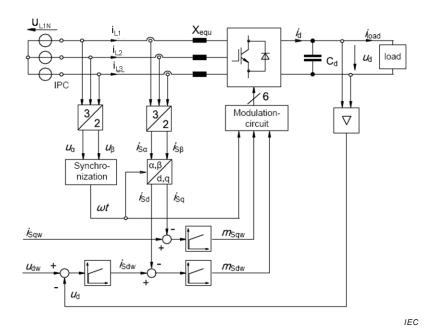

| Figure 37 – Block diagram of a two level PWM AIC                                                                                                                                                                            | 49 |

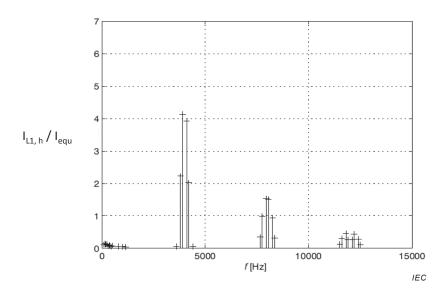

| Figure 38 – Distortion of the current $i_{L1}$ of reactance $X_{equ}$ , pulse frequency: 4 kHz, relative reactance of $u_{SCV,equ}$ = 6 %                                                                                   | 51 |

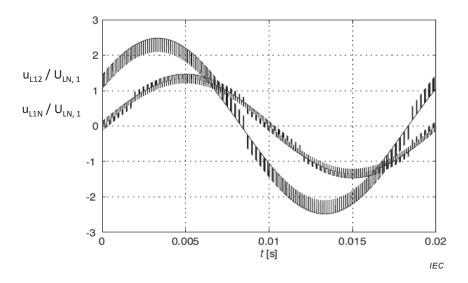

| Figure 39 – Typical voltages $u_{\text{L1N}}$ / $U_{\text{LN, 1}}$ and $u_{\text{L12}}$ / $U_{\text{LN, 1}}$ at pulse frequency of 4 kHz, relative reactance $u_{\text{SCV,equ}}$ = 6 %, $R_{\text{SCe}}$ = 100             | 51 |

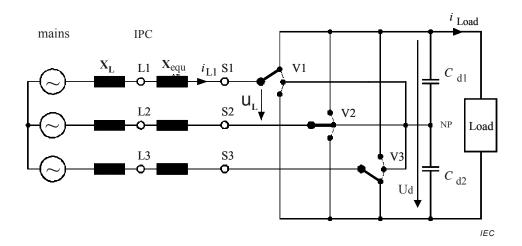

| Figure 40 – Basic topology of a three level AIC. For a Power Drive System (PDS) the same topology may be used also on the load side                                                                                         | 52 |

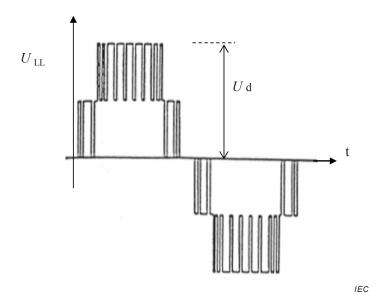

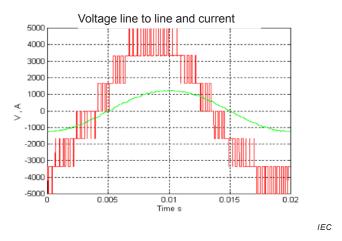

| Figure 41 – Typical curve shape of the phase-to-phase voltage of a three level PWM converter                                                                                                                                | 53 |

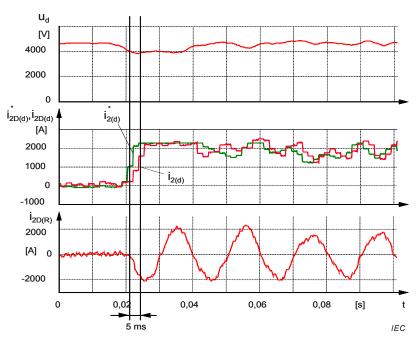

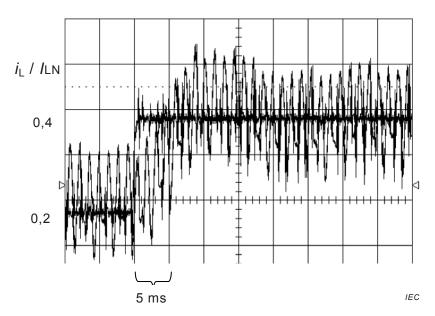

| Figure 42 – Example of a sudden load change of a 13 MW three level converter where the current control achieves a response time within 5 ms                                                                                 | 54 |

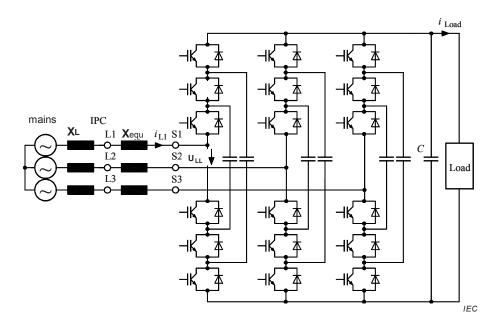

| Figure 43 – Typical topology of a flying capacitor (FC) four level AIC using IGBTs                                                                                                                                          | 55 |

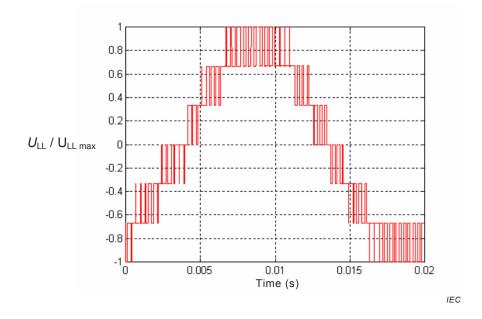

| Figure 44 – Typical curve shape of the phase-to-phase voltage of a multi-(four)-level AIC                                                                                                                                   | 56 |

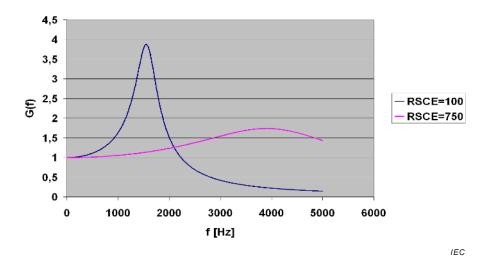

| Figure 45 – Distorting frequencies and amplitudes in the line voltage (measured directly at the bridge terminals in Figure 25 and the line current of a multilevel (four) AIC (transformer with 10 % short-circuit voltage) | 57 |

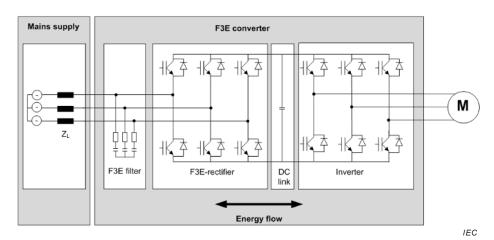

| Figure 46 – Topology of a F3E AIC                                                                                                                                                                                           | 58 |

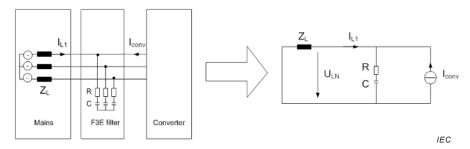

| Figure 47 – Line side filter and equivalent circuit for the F3E-converter behaviour for the power supply network                                                                                                            | 59 |

| Figure 48 – Current transfer function together with $R_{SCe}$ = 100 and $R_{SCe}$ = 750 and a line side filter: $G(f) = i_{L1}/i_{CONV}$                                                                                    | 59 |

| Figure 49 – PWM – voltage distortion over power supply network impedance for F3E-infeed including power supply network side filter                                                                                          | 60 |

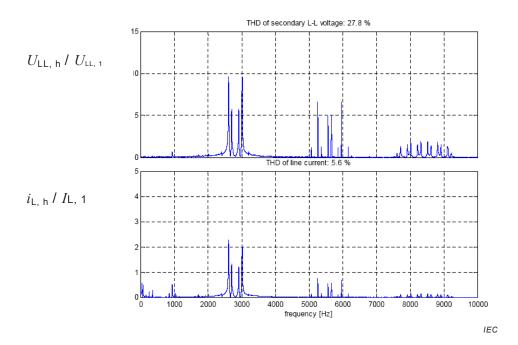

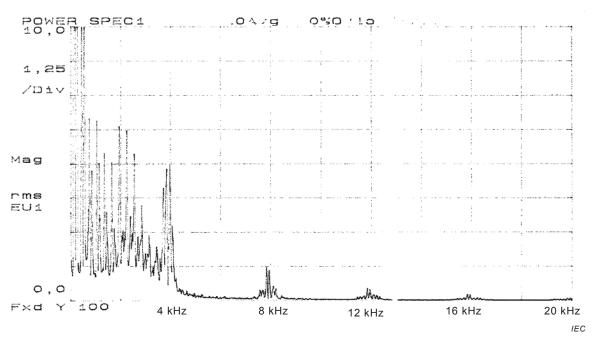

| Figure 50 - Input current spectrum of a 75kW-F3E-converter                                                                                                                                                                  | 61 |

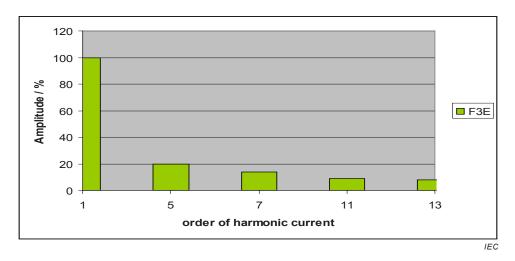

| Figure 51 – Harmonic spectrum of the input current of an F3E-converter with $R_{SCe} = 100$                                                                                                                                 | 61 |

| Figure 52 – An illustration of a distortion effect caused by a single phase converter with capacitive load                                                                                                                  | 62 |

| Figure 53 – a.c. to a.c. AIC pulse chopper, basic circuit                                                                                                                                                                   | 63 |

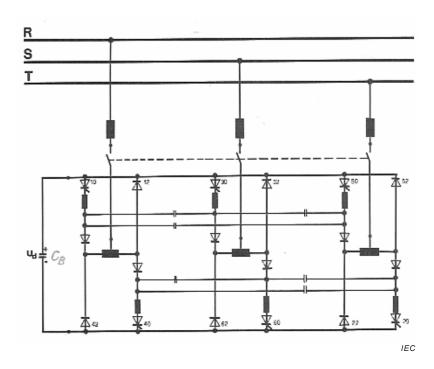

| Figure 54 – Illustration of a converter topology for a current source AIC                                                                                                                                                   | 65 |

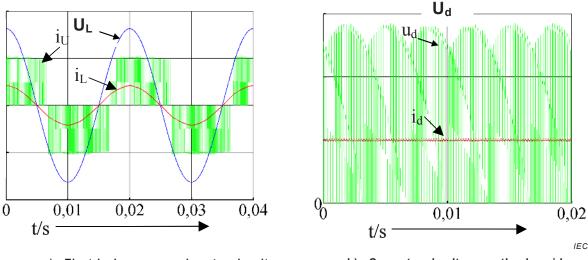

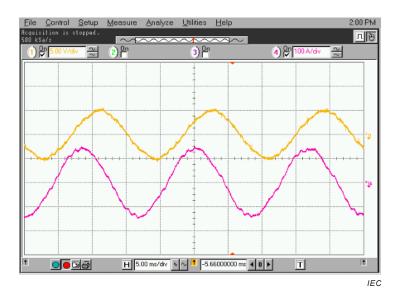

| Figure 55 – Typical waveforms of currents and voltages of a current source AIC with high switching frequency                                                                                                                | 66 |

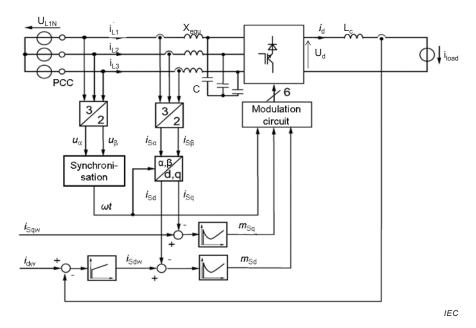

| Figure 56 – Typical block diagram of a current source PWM AIC                                                                                                                                                               | 67 |

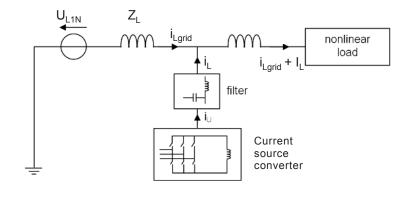

| Figure 57 – Current source AIC used as an active filter to compensate the harmonic currents generated by a nonlinear load                                                                                                   | 67 |

| Figure 58 – Step response (reference value and actual value) of current source AIC with low switching frequency [33]                                                                                                        | 68 |

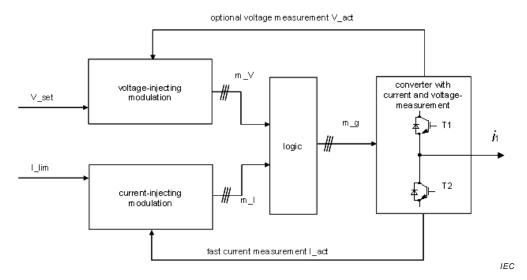

| Figure A.1 – Principle sketch for combined voltage- and current-injecting modulation example for phase leg R                                                                                                                                      | 71  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

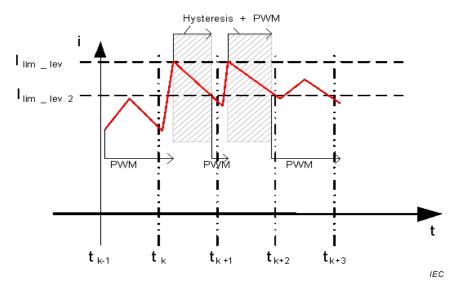

| Figure A.2 – Example for controlled phase current during a voltage dip at the power supply network using hysteresis plus PWM control                                                                                                              | 72  |

| Figure A.3 – Typical waveforms of electrical power supply network current and voltage for a current source AIC with low switching frequency [33]                                                                                                  | 72  |

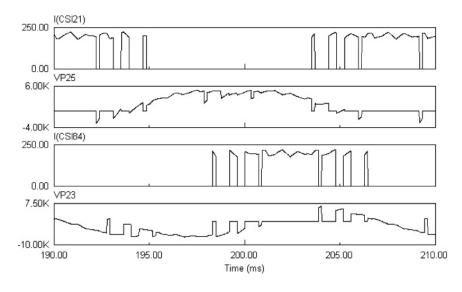

| Figure A.4 – Currents and voltages in a (semiconductor) valve device of an AIC and a machine side converter both of the current source with low pulse frequency [33]                                                                              | 73  |

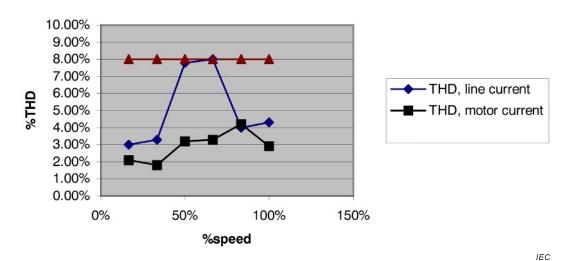

| Figure A.5 – Total harmonic distortion of electrical power supply network and motor current [33] remains always below 8 % (triangles in straight line) in this application                                                                        | 73  |

| Figure A.6 – Basic topology of an AIC with commutation on the d.c. side (six pulse variant)                                                                                                                                                       |     |

| Figure A.7 – Dynamic performance of a reactive power converter                                                                                                                                                                                    | 75  |

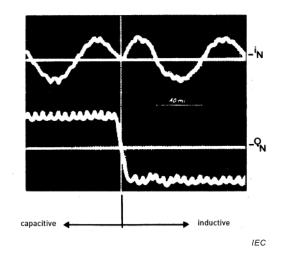

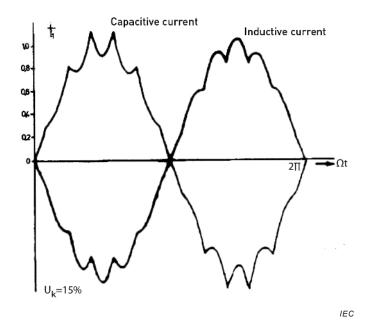

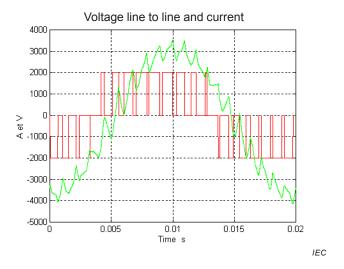

| Figure A.8 – Line side current for a twelve pulse Reactive Power Converter in a capacitive and inductive operation mode ( $u_{SCV,equ} = 15\%$ )                                                                                                  | 75  |

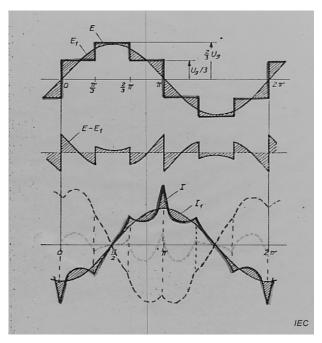

| Figure A.9 – The origin of the current waveform of a RPC by the line voltage (sinusoidal) and the converter voltage (rectangular)                                                                                                                 | 76  |

| Figure A.10 – Two level topology with nominal voltage of maximum 1 200 V and timescale of 5 ms/div                                                                                                                                                | 77  |

| Figure A.11 – Three level topology with nominal voltage of maximum 2 400 V and timescale of 5 ms/div                                                                                                                                              | 77  |

| Figure A.12 – Four level topology with nominal voltage of maximum 3 300 V and timescale of 5 ms/div                                                                                                                                               | 78  |

| Figure A.13 – General influence of significant characteristics to the voltage distortion and current distortion                                                                                                                                   | 79  |

| Figure A.14 – Measured reduction of voltage distortion when four AICs are connected to the power supply network                                                                                                                                   | 80  |

| Figure A.15 – Excerpts from a catalogue information of a power capacitor manufacturer; 760 V AC; (rated voltage: 690 V AC) for temperature calculation                                                                                            | 81  |

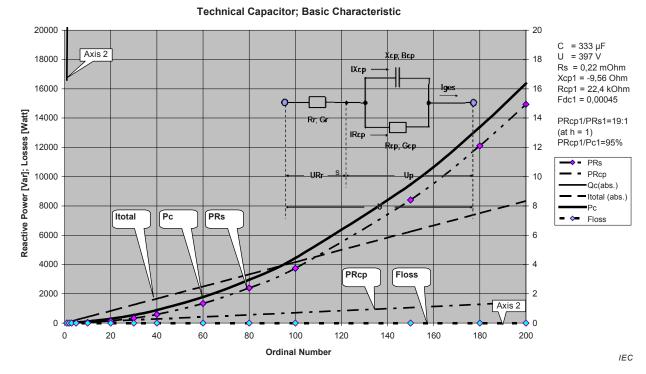

| Figure A.16 – Reactive power and losses of a power capacitor supplied by a source with constant reference voltage and variable frequency $(R_{Cp} = f(h))$                                                                                        | 82  |

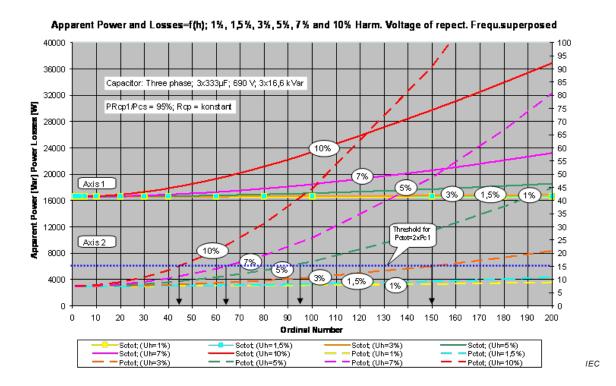

| Figure A.17 – Apparent power and losses of a typical power capacitor at different voltage distortion levels and the critical frequency boundaries (at singular frequency) where the temperature rise reaches substantial values (vertical arrows) | 83  |

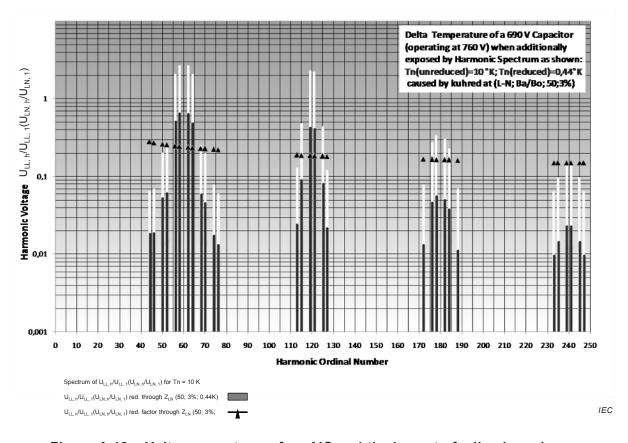

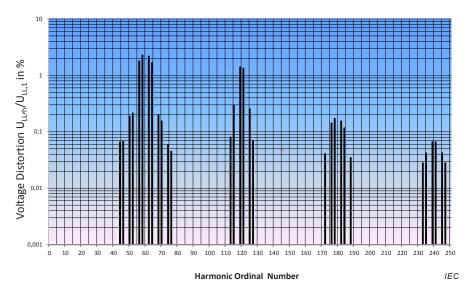

| Figure A.18 – Voltage spectrum of an AIC and the impact of a line impedance reduction to the temperature of the capacitor (from 10 K to 0,44 K) and the composition of the spectrum                                                               | 84  |

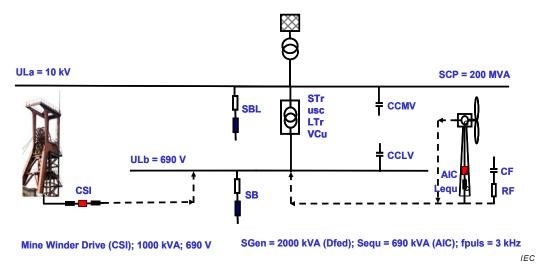

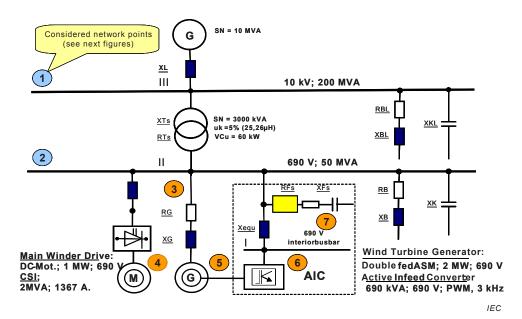

| Figure A.19 – A wind turbine plant and a mine winder drive connected on the same power line                                                                                                                                                       |     |

| Figure A.20 – Power supply network configuration for the plant of Figure A.19 with allocated measurement points                                                                                                                                   |     |

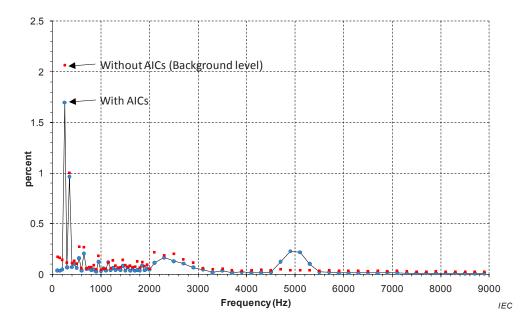

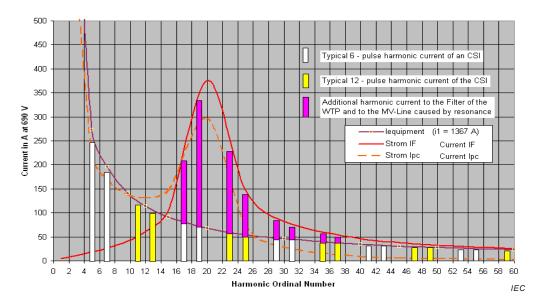

| Figure A.21 – Regular current of the CSI (AIC-filter disabled) and amplification of the current in case of resonance caused by the AIC-filter circuit (when AIC filter is enabled)                                                                | 87  |

| Figure A.22 – Basic principle of impedance measurement                                                                                                                                                                                            |     |

| Figure A.23 – Harmonic current generation by disturbing device                                                                                                                                                                                    |     |

| Figure A.24 – Measurement by switching a resistor                                                                                                                                                                                                 |     |

| Figure A.25 – Measurement by a capacitor bank                                                                                                                                                                                                     |     |

| Figure A.26 – A 6,6 kV power supply network impedance measurement system for                                                                                                                                                                      | 🗸 . |

| islanding detection by injecting interharmonics                                                                                                                                                                                                   | 92  |

| Figure B.1 – Withstand capability level towards harmonic voltages in the power supply network in view of permissible temperature rise within capacitors if the voltage distortion is determined either by one predominating frequency (upper line) or if the distortion is predominantly determined by a harmonic spectrum, caused by several parallel operated AICs (2-Level PWM) (lower line) | 96  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure B.2 – Harmonic voltage spectrum of one 2-Level PWM AIC with acceptable temperature increase of a power capacitor not exceeding 10 K                                                                                                                                                                                                                                                      | 97  |

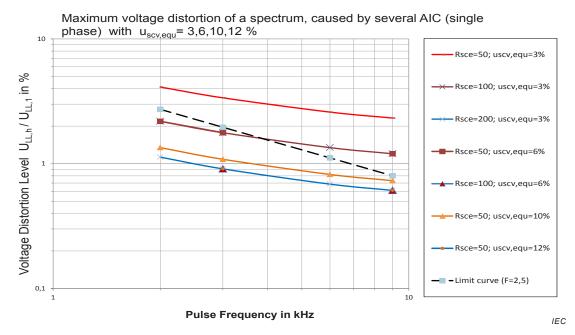

| Figure B.3 – Maximum voltage distortion of a spectrum, caused by several AICs (single phase topologies)                                                                                                                                                                                                                                                                                         | 98  |

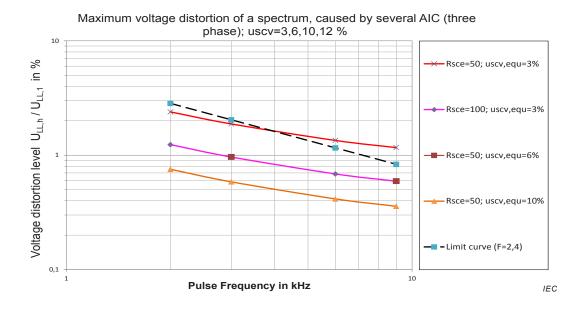

| Figure B.4 – Maximum voltage distortion of a spectrum, caused by several AICs (three phases topologies)                                                                                                                                                                                                                                                                                         | 98  |

| Figure B.5 – Spreadsheet of matching single phase AICs (2-level) to different power supply network conditions in order to apply the power capacitor limit curves                                                                                                                                                                                                                                | 99  |

| Figure B.6 – Spreadsheet of matching three phases AICs (2-level) to different power supply network conditions in order to apply the power capacitor limit curves                                                                                                                                                                                                                                | 99  |

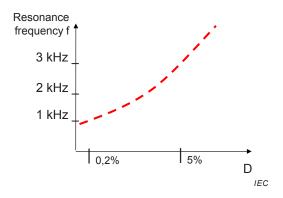

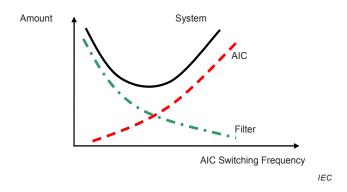

| Figure B.7 – Illustration of the typical power supply network resonance frequency by increasing AIC filtering population, versus the voltage distortion level                                                                                                                                                                                                                                   | 100 |

| Figure B.8 – Sketch of the typical size/cost of an AIC application versus switching frequency of the AIC                                                                                                                                                                                                                                                                                        | 101 |

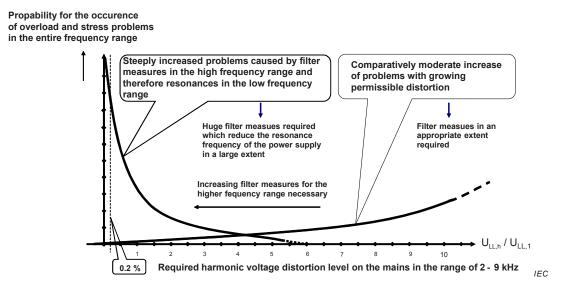

| Figure B.9 – Illustration of the probability of overload and stress problems for the power supply network and the equipment connected thereto, depending on stipulated distortion levels fixed in miscellaneous assumptions                                                                                                                                                                     | 101 |

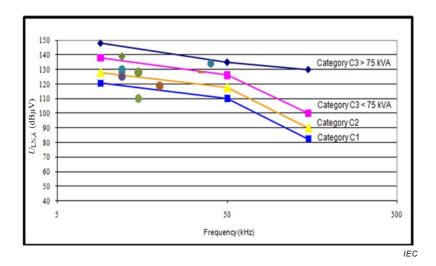

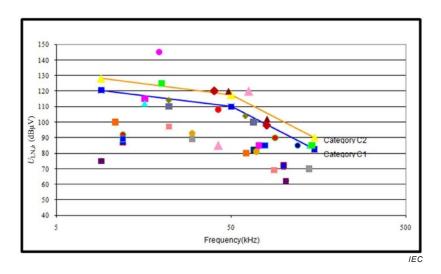

| Figure B.10 – Results of the data collection versus the maximum values proposed in the IEC TS 62578 for products rated above 75 kVA                                                                                                                                                                                                                                                             | 103 |

| Figure B.11 – Results of the data collection versus the maximum values proposed in the IEC TS 62578 for products rated below 75 kVA                                                                                                                                                                                                                                                             | 104 |

| Figure B.12 – Results of the data collection versus the maximum values proposed in the IEC TS 62578 for products rated above 75 kVA                                                                                                                                                                                                                                                             | 104 |

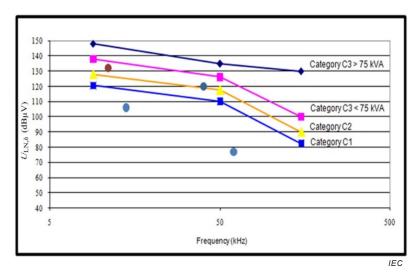

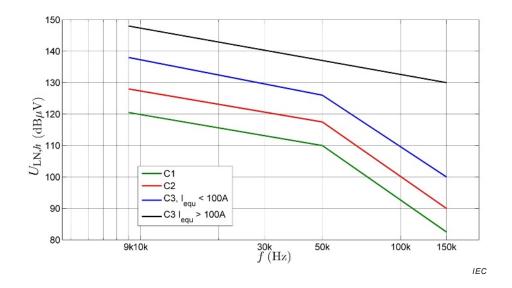

| Figure B.13 – Recommended maximum emission values for AIC of different categories in the range from 9 kHz up to 150 kHz                                                                                                                                                                                                                                                                         | 105 |

| Table 1 – Parameters of line impedance stabilisation network for different power system impedance curves                                                                                                                                                                                                                                                                                        | 39  |

| Table 2 – Parameters of the LISN described in Figure 25 and Figure 26                                                                                                                                                                                                                                                                                                                           |     |

| Table A.1 – Condition state 1: positive current limit reached, transistor T1 is switch-off to reduce the current                                                                                                                                                                                                                                                                                |     |

| Table A.2 – Condition state 2: negative current limit reached, transistor T2 is switch-off to reduce the current                                                                                                                                                                                                                                                                                |     |

| Table A.3 – Condition state 0: current in phase R within tolerance range, pure voltage injection active (e.g. with PWM)                                                                                                                                                                                                                                                                         | 71  |

| Table A.4 – Comparison of different PWM AICs of VSC topology                                                                                                                                                                                                                                                                                                                                    | 76  |

| Table A.5 – Voltage distortion on both power lines (II and III) without and with filter circuit (the filter had been designed to achieve 0,2 % distortion level on the MV-power line)                                                                                                                                                                                                           | ·   |

| Table A.6 – Current distribution within the network described for specific frequencies and on allocated measurement points as pointed out in Figure A.20                                                                                                                                                                                                                                        | 88  |

| Table B.1 – AIC design recommendation for a maximum distortion factor in the frequency range from 2 to 9 kHz                                                                                                                                                                                                                                                                                    | 102 |

| Table B.2 – Recommended maximum emission values for AIC of different categories in the range from 9 kHz up to 150 kHz                                                                                                                                                                                                                                                                           | 106 |

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

# POWER ELECTRONICS SYSTEMS AND EQUIPMENT -

Operation conditions and characteristics of active infeed converter (AIC) applications including design recommendations for their emission values below 150 kHz

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. In exceptional circumstances, a technical committee may propose the publication of a technical specification when

- the required support cannot be obtained for the publication of an International Standard, despite repeated efforts, or

- The subject is still under technical development or where, for any other reason, there is the future but no immediate possibility of an agreement on an International Standard.

Technical specifications are subject to review within three years of publication to decide whether they can be transformed into International Standards.

IEC TS 62578, which is a technical specification, has been prepared by IEC technical committee TC 22: Power electronic systems and equipment.

This second edition cancels and replaces the first edition published in 2009. This edition constitutes a technical revision.

This edition includes the following significant technical changes with respect to the previous edition:

- a) IEC TS 62578, in its revised version includes observed values out of practical applications for emission values below 150 kHz.

- b) Therefore the document has been extended compared to the first edition, several detailed analysis results are given in the extended Annexes.

- c) Design recommendations have been derived from the international working group by an assessment of the power supply impedances between 2 kHz and 9 kHz, a comprehensive analysis of the withstand capability of power capacitors against harmonic currents injected by AIC, immunity tests of equipment and considerations about shifted resonances in the power supply network with increased population of undamped filter capacitors.

The text of this technical specification is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 22/235/DTS    | 22/239/RVC       |

Full information on the voting for the approval of this technical specification can be found in the report on voting indicated in the above table.

The French version of this technical specification has not been voted upon.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- transformed into an International standard,

- reconfirmed.

- withdrawn,

- · replaced by a revised edition, or

- amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

# INTRODUCTION

This revision of the technical specification IEC TS 62578 is necessary because active infeed converters (AIC) are a state of the art technology in power electronic products and will be of major importance in order to realize the "smart grid" and the "energy efficiency" initiatives.

AICs in industrial and domestic use are necessary to feedback energy from an energy source (e.g. solar panels, fuel cells or wind turbines) or from a motor load to the power supply network and make it available for other consumers instead of dissipating it as a waste-heat to the environment.

Dispersed power generating equipment uses AICs to synchronise their voltages and currents to the power supply network or to exchange electrical energy between energy storage devices such as batteries and consumers.

Utilities will require information on how to correctly apply the AICs in order to mitigate harmonics in the power supply network.

AICs can also be used to mitigate pre-existing harmonics in the supply system – information on this is of interest to utilities.

Different possible topologies of AICs are described together with their specific advantages.

Warning: The recommendations of maximum emission values for conducted emissions <150 kHz defined in this document are based on observations and experience gained from state of the art AICs operating today in most power supply networks together with other equipment without creating intolerable interference and should lead to an increased acceptance of using AICs.

Nevertheless it has to be highlighted that electromagnetic environment is subject to changes e.g. because of smart grid deployment and that emission limits that are currently under development by the IEC EMC Committees may be different to the maximum emission values recommended in this document.

This document is being issued in the Technical Specification series of publications (according to the ISO/IEC Directives, Part 1, 3.1.1.1) as a "prospective standard for provisional application" in the field of power electronics because there is an urgent need for guidance on the design and use of active infeed converters (AIC) today and in "smart grid environments".

It remains unclear during revision of this document, how and when the smart grid vision will be realized and to what extent in the future. AICs will be the "key link components" if several electrical energy storage devices or storage technologies and energy users are to be connected together and will interact under "smart grid behaviour" conditions. The power supply network may adapt its future characteristics compared to the state of the art while increasing the installed density of AIC.

# POWER ELECTRONICS SYSTEMS AND EQUIPMENT -

Operation conditions and characteristics of active infeed converter (AIC) applications including design recommendations for their emission values below 150 kHz

# 1 Scope

This Technical Specification IEC TS 62578 describes the operation conditions and typical characteristics of active infeed converters (AIC) of all technologies and topologies which can be connected between the electrical power supply network (lines) a.c. side and a constant current or voltage type d.c. side and which can convert electrical power (active and reactive) in both directions (generative or regenerative).

Applications with active infeed converters are commonly used with the d.c. sides of adjustable speed power drive systems (PDS), uninterruptible power systems (UPS), active filters, photovoltaic systems, wind turbine systems, battery backed power management systems etc. of all voltages and power ratings.

Active infeed converters are generally connected between the electrical power supply network (a.c. side) and a current or voltage d.c. side, with the objective to avoid emitting low frequency harmonics (e.g. less than 1 kHz) by synthesizing a sinusoidal a.c. current. Some of them can additionally compensate the pre-existing harmonic distortion of a given supply side voltage. They are moreover able to control the power factor of a power supply network section by moving the electrical power (active and reactive) in both directions (generative or regenerative), which enables energy saving in the system and stabilizes the power supply voltage or enables coupling of renewable energy sources or electrical energy storage devices to the supply.

A practical and analytical approach for emission values for AICs in power supply networks is given, which is based on the latest results for line impedance values between 2 kHz and 9 kHz and withstand capability of capacitors connected directly to the supply.

This results in design recommendations for emission values below 150 kHz.

The following is excluded from the scope.

- Requirements for the design, development or further functionality of active infeed applications.

- Probability of interactions or influences of the AIC with other equipment caused by parasitic elements in an installation or caused by poor electronic design as well as their mitigations.

- "Overhead line" power supply networks because of lack of information (measurements) of their three phase impedances. This could be the subject for future editions.

### 2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and are indispensable for its application. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60050 (all parts), International Electrotechnical Vocabulary (available at www.electropedia.org)

IEC TR 60725:2012, Consideration of reference impedances and public supply network impedances for use in determining the disturbance characteristics of electrical equipment having a rated current  $\leq$ 75 A per phase

IEC 61800-3, Adjustable speed electrical power drive systems – Part 3: EMC requirements and specific test methods

IEC 61800-5-1, Adjustable speed electrical power drive systems – Part 5-1: Safety requirements – Electrical, thermal and energy

IEC 62040-1, Uninterruptible power systems (UPS) – Part 1: General and safety requirements for UPS

IEC 62103, Electronic equipment for use in power installations

IEC 61000-4-7:2002, Electromagnetic compatibility (EMC) – Part 4-7: Testing and measurement techniques – General guide on harmonics and interharmonics measurements and instrumentation, for power supply systems and equipment connected thereto IEC 61000-4-7:2002/AMD1:2008

CISPR 16-1-1, Radio disturbance and immunity measuring apparatus – Measuring apparatus

#### 3 Terms and definitions

For the purposes of this document, the terms and definitions given in IEC 60500 and the following apply

#### 3.1

# active equalization of the power supply network

ability of an AIC to enable and combine smart grid functionalities with a specific main application

Note 1 to entry: Specific main applications include:

- reduce or avoid emitting low frequency harmonics (e.g. less than 2 kHz) from the power supply network by synthesizing a sinusoidal line current

- contributes to controlling the reactive power of a power supply network

- · exchanging the electrical power (active and reactive) in generative or regenerative modes

- stabilization of the power supply voltage and energy saving in the supply system

- exchanging electrical energy between power supply networks or other power generations applications like fuel cells and electrical energy storage devices

- coupling of decentralized power sources (e.g. from renewable energy) to the power supply network.

#### 3.2

#### a.c. filter

filter consisting of passive components, such as inductors, capacitors and resistors connected to the a.c. side of a converter, designed to reduce the circulation of harmonic currents in the associated system

# 3.3

#### active filter

AIC operating as a filter to control the specific a.c. side harmonic and interharmonics voltages or currents usually without active power flow

#### active infeed application

application using the properties of an active infeed converter

#### 3.5

#### active infeed converter

#### **AIC**

self-commutated electronic power converters of all technologies, topologies, voltages and sizes which are connected between to the a.c. power supply network (lines) and usually a stiff d.c. side (current source or voltage source) and which can convert electric power in both directions (generative or regenerative) and which can control the reactive power or the power factor

Note 1 to entry: Some of them can additionally control the harmonics to reduce the distortion of an applied voltage or current.

Note 2 to entry: Basic topologies may be realized as a Voltage Source Converter (VSC) or a Current Source Converter (CSC).

Note 3 to entry: In IEC 60050-551 these terms (VSC and CSC) are defined as voltage stiff a.c./d.c. converter (551-12-03) and current stiff a.c./d.c. converter (551-12-04). Most of the AICs are bi-directional converters and have sources on the d.c. side. So, they are known as voltage source converters and current source converters in this TS.

Note 4 to entry: Some kind of AIC might be realized without a stiff d.c. side (a.c. matrix converter). Also a.c. conversion equipment could be included.

#### 3.6

# controlled free-wheeling arm

by-pass arm constructed with controllable valve device(s)

#### 3.7

#### controllable harmonics or interharmonics

set of harmonics or interharmonics which can be influenced directly by the control strategy of the AIC

## 3.8

#### conventional converter

converter based on line commutation technology, that cannot control power factor or harmonics

#### 3.9

# converter topology

different possible arrangements of semiconductor valves and their connections

# 3.10

#### d.c. filter

filter on the d.c. side of a converter, designed to reduce the ripple in the associated system

# 3.11

#### d.c. side load

electrical device consuming or generating power connected to the d.c. side

#### 3.12

#### effective supply-side filter impedance

effective impedance of the supply-side filter of the AIC for frequencies in the range of the controllable harmonics or interharmonics

# evidential per unit supply side impedance of the AIC

#### $u_{\sf scv.equ}$

per unit short-circuit voltage drop value of the hardware inductance which is connected between the AIC and the power supply network

$$u_{\text{scv,equ}} = Z_{\text{choke}} / (U_{\text{LN}} / I_{\text{equ}})$$

#### 3.14

#### fundamental and harmonic components

defined in IEC 60050:101, IEC 60050:161 and IEC 60050:551, respectively and are dedicated for the AIC in this document

#### 3.15

#### F3E-infeed

# fundamental frequency front end infeed

fundamental frequency front end voltage source converter with its commutation capacitor on the a.c. side which uses line-frequency switched semiconductor valve devices and has regenerative capability

Note 1 to entry: The d.c.-link capacitor which is normally an electrolytic capacitor is basically replaced by an a.c. line side filter, designed to limit the voltage distortion caused by the PWM currents of the inverter stage

#### 3 16

## generated harmonics or interharmonics

set of harmonics or interharmonics which result from the pulse frequency and the pulse pattern

#### 3.17

# in-plant point of coupling

#### IPC

point on a network inside a system or an installation, electrically nearest to the AIC, at which other apparatus are, or could be, connected

Note 1 to entry: The IPC is usually the point for which electromagnetic compatibility is to be considered. In case of connection to the public supply system the IPC is equivalent to the PCC (Point of Common Coupling).

#### 3.18

#### $k_{\mathsf{zred}}$

ratio of the power supply impedance according to 5.2.4 (95 % values) related to the frequency proportional extrapolated reference impedance according IEC 60725

#### 3.19

#### line impedance of phase x

#### $Z_{\mathsf{Lx.\,h}}$

line impedance of phase x at harmonic order h

Note 1 to entry: The impedance at a harmonic frequency between the star point of the equivalent power supply and one of the phase terminals at a defined point on a network. The point on a network could be defined to be for example the terminals of the AIC or the in-plant point of coupling.

#### 3.20

# long-time energy storage device

device connected to the d.c.-link directly or by a semiconductor valve device, or a converter, providing rated power for typically seconds to minutes

# neutral impedance at harmonic order h

# $Z_{\mathsf{N. h}}$

impedance between the star point of the equivalent power supply and neutral terminal at a defined point on a network

Note 1 to entry: The point on a network could be defined to be for example the terminals of the AIC or the in-plant point of coupling.

#### 3.22

# **PWM** controlled converter

converter using a pulse-width modulation technique in order to control the switching of its semiconductor valve devices

#### 3.23

#### pulse frequency

frequency, resulting from the switching frequency and the converter topology, which characterizes, together with the selected pulse pattern, the lowest frequency of non-controllable harmonics or interharmonics at the IPC (in-plant point of coupling)

Note 1 to entry: The switching frequency itself may not be present as a harmonic or interharmonics

#### 3.24

#### pulse pattern

pattern of the switched voltages or currents, measurable at the terminal of the converter, resulting from pulse frequency and modulation schemes used

#### 3.25

# rated apparent power of equipment

#### $S_{\sf eq}$

value calculated from the rated r.m.s. line current  $I_{\rm equ}$  of the piece of equipment stated by the manufacturer and dependent on the rated interphase voltage  $U_{\rm LL}$

$S_{\rm equ}$  =  $\sqrt{3}$   $\times$   $U_{\rm LL}$   $\times$   $I_{\rm equ}$  for balanced three phase equipment

$S_{

m equ}$  =  $U_{

m LL} imes I_{

m equ}$  for interphase equipment

$S_{\mathrm{eau}}$  =  $U_{\mathrm{LN}} \times I_{\mathrm{eau}}$  for single phase equipment

#### 3.26

# reactive power converter

converter for reactive power compensation that generates or consumes reactive power without the flow of active power except for the power losses in the converter

[SOURCE: IEC 60050-551:1998, 551-12-15]

## 3.27

# short-circuit power

Sec

value of the three-phase short-circuit power calculated from the nominal line to line system voltage  $U_{\rm LL}$  and the impedance  $Z_{\rm Lx,1}$  of the system at the point of common coupling (PCC)

Note 1 to entry: In this case the  $U_{\rm LL}$  is the nominal line to line voltage of the power supply network.

$$S_{SC} = (U_{11})^2 / Z_{1\times 1}$$

where

$Z_{\rm Lx,1}$  is the supply impedance at the fundamental frequency.

#### short-circuit ratio

#### Rsce

characteristic value for the application of a single equipment derived from the Ratio of short-circuit power of the supply to the rated apparent power of the AIC of the single equipment  $(S_{\text{equ}})$

$R_{SCe} = S_{SC} / S_{equ}$  for balanced three phase equipment

$R_{SCe} = S_{SC} / (2* S_{equ})$  for interphase equipment

$R_{SCe} = S_{SC} / (3^* S_{equ})$  for single phase equipment

#### 3.29

## short-time energy storage device

one or more inductors or capacitors providing rated power for about 1 ms to 10 ms and directly connected to the d.c. side

Note 1 to entry: Short time energy storage is used to have a stiff voltage or current characteristic or operate the AIC continually in short time a.c. voltage dip, and time could be more than 10 ms.

Note 2 to entry: Long-time energy storage is used to provide energy to a.c. power system.

#### 3.30

#### switching frequency

frequency with which the semiconductor valve devices of a PWM converter are operated

Note 1 to entry: In some converters the switching frequency may not be the same for all semiconductor valve devices.

#### 3.31

#### total impedance

resulting impedance consisting of the supply impedance and the supply-side filter impedance of the AIC

# 3.32

$U_{\mathsf{LL. 1}}$

fundamental frequency line to line voltage rms value of the power supply network

#### 3.33

$U_{\mathsf{LL.\;h}}$

harmonic line to line voltage rms value of the power supply network

#### 3.34

U<sub>LN. h</sub> / U<sub>LN. 1</sub>

relative voltage (line to neutral voltage) at order h

Note 1 to entry: ratio of a harmonic line to neutral voltage amplitude to the fundamental frequency line to neutral voltage amplitude

#### 3.35

$U_{\rm LL, \, h}$  /  $U_{\rm LL, \, 1}$

relative harmonic voltage (line to line) at order h

#### 3.36

$X_{\mathsf{L, h}}$

actual resulting reactance of the power supply network at the IPC

Note 1 to entry: The index "h" means in any case that the dedicated reactance is considered at a certain harmonic order.

$Z_{L,h}$

actual resulting impedance of the power supply network at the IPC

Note 1 to entry: For harmonic calculation for a single phase load:  $Z_{\rm L} = Z_{\rm Lx} + Z_{\rm LN}$  is used. For a three phase load:  $Z_{\rm L} = Z_{\rm Lx}$  is used. The index "h" means in any case that the dedicated impedance is considered at a certain harmonic order.

# 4 General system characteristics of PWM active infeed converters connected to the power supply network

#### 4.1 General

In this clause, the voltage source AIC, which is used in large numbers, is chosen as the example.

#### 4.2 Basic topologies and operating principles

#### 4.2.1 General

Active Infeed Applications are mainly available with capacitive (VSC) or inductive (CSC) smoothing on the d.c. side. Some converter concepts use no or nearly no d.c.-side smoothing. The majority of installed units utilize capacitive smoothing.

Depending on the rated power and the power supply network availability the connection to the power supply network may be single-phase or three-phase. The three-phase version is selected for the examples.

#### 4.2.2 Operating principles

The main operating principle is to switch the d.c.-side potentials or the d.c.-side currents to the a.c. side conductors with a pulse frequency of normally between 300 Hz and 20 kHz. In this way the desired voltages or currents on the a.c. side are realised as mean values. The pulse frequency is normally high compared to the line frequency and allows quick and accurate control of the voltages and currents on the a.c. side. However, switching between fixed potentials or currents generates undesirable distortions in the high frequency range. Passive a.c-side filters might be required to mitigate those.

A control system allows a precise control of the fundamental and additional harmonic components. The frequency up to which harmonics can be controlled is determined by the pulse frequency of the converter.

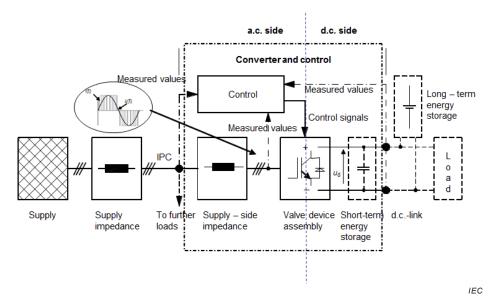

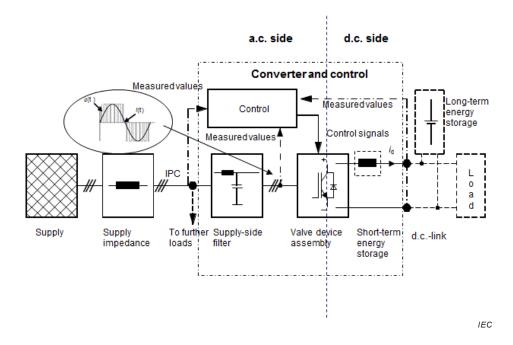

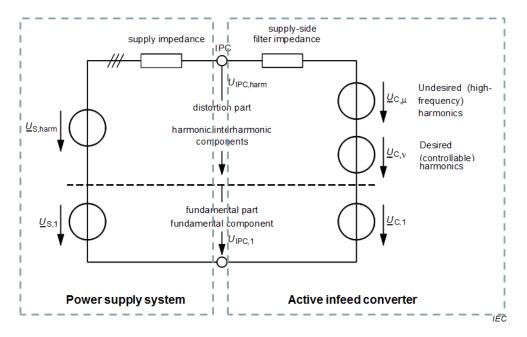

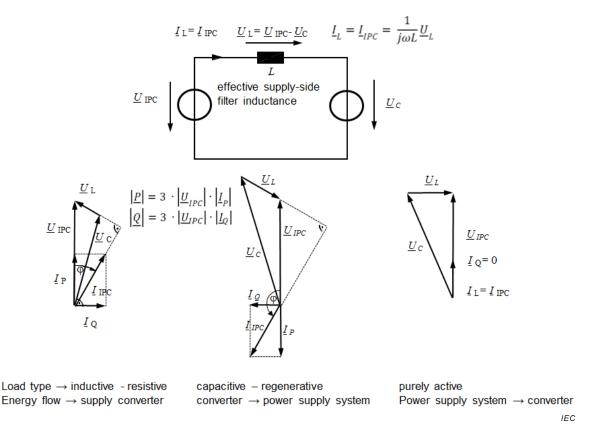

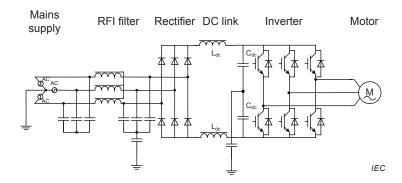

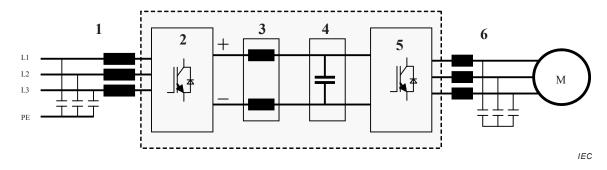

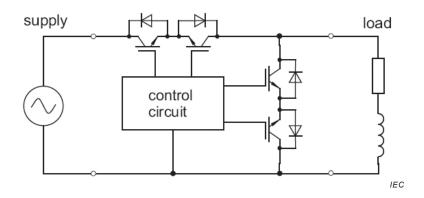

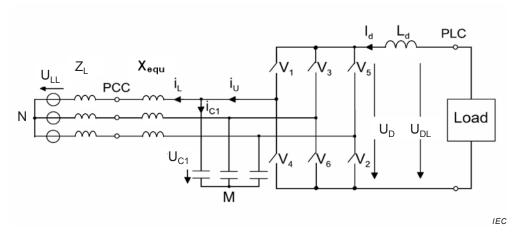

The usual structure of VSC and CSC systems is shown in Figure 1 and Figure 2, respectively:

NOTE The valve device symbols are used merely for illustration.

Figure 1 - AIC in VSC topology, basic structure

$\label{eq:note_norm} \mbox{NOTE} \quad \mbox{The valve device symbols are used merely for illustration}.$

Figure 2 - AIC in CSC topology, basic structure

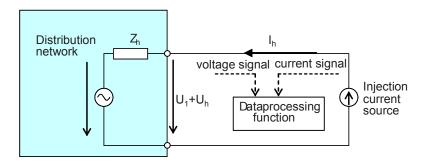

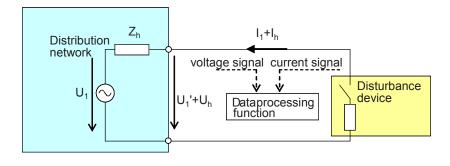

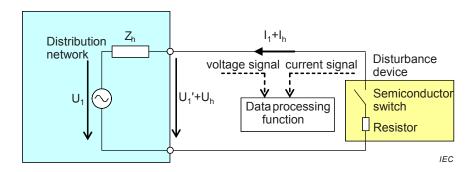

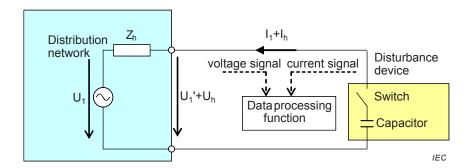

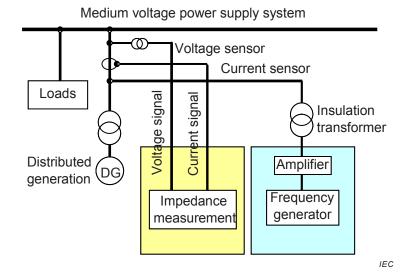

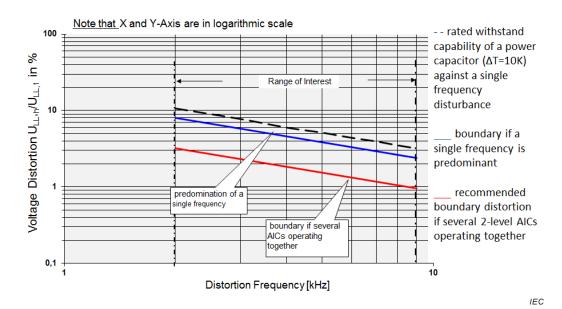

Figure 1 and Figure 2 show that the structure of voltage and current source converter systems is very similar. The main differences can be found on the d.c. side, the a.c. side filters and in the type of semiconductors used for the valve device part of the converter. Details can be found in the sections covering the different topologies.