PD IEC/TR 62433-2-1:2010

# **EMC IC modelling**

Part 2-1: Theory of black box modelling for conducted emission

#### **National foreword**

This Published Document is the UK implementation of IEC/TR 62433-2-1:2010.

The UK participation in its preparation was entrusted to Technical Committee EPL/47, Semiconductors.

A list of organizations represented on this committee can be obtained on request to its secretary.

This publication does not purport to include all the necessary provisions of a contract. Users are responsible for its correct application.

© BSI 2011

ISBN 978 0 580 68978 9

ICS 31.200

Compliance with a British Standard cannot confer immunity from legal obligations.

This Published Document was published under the authority of the Standards Policy and Strategy Committee on 28 February 2011.

#### Amendments issued since publication

Amd. No. Date Text affected

### IEC/TR 62433-2-1

Edition 1.0 2010-10

# TECHNICAL REPORT

# RAPPORT TECHNIQUE

**EMC IC modelling –**

Part 2-1: Theory of black box modelling for conducted emission

Modèles de circuits intégrés CEM -

Partie 2-1: Théorie du modèle de la boîte noire pour les émissions conduites

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

PRICE CODE CODE PRIX

ICS 31.200

ISBN 978-2-88912-208-0

### CONTENTS

| FOI   | REWC                  | )RD                                                                           | 3    |  |

|-------|-----------------------|-------------------------------------------------------------------------------|------|--|

| 1     | Scop                  | e                                                                             | 5    |  |

| 2     | Integ                 | Integrated circuit and modelling board                                        |      |  |

| 3     | Assumptions           |                                                                               |      |  |

|       | 3.1                   | ICEM-CE                                                                       | 7    |  |

|       | 3.2                   | Black box model                                                               | 9    |  |

| 4     | Modelling             |                                                                               |      |  |

|       | 4.1                   | Terminals and objectives                                                      | 9    |  |

|       | 4.2                   | Admittance matrix                                                             |      |  |

|       | 4.3                   | Matrix compaction                                                             |      |  |

| 5     | 4.4                   | Black box model structure                                                     |      |  |

| 5     | Parameter extractions |                                                                               |      |  |

|       | 5.1<br>5.2            | General  Equivalent internal activities                                       |      |  |

|       | 5.3                   | Equivalent passive distribution network                                       |      |  |

|       | 5.4                   | Parameter extraction method using finite impedance termination                |      |  |

|       | 5.5                   | Black box model including the reference terminal                              |      |  |

| 6     | Imple                 | ementation                                                                    | . 17 |  |

|       | 6.1                   | General                                                                       | .17  |  |

|       | 6.2                   | Configuration of the application board                                        | . 17 |  |

|       | 6.3                   | Implementation of black box models                                            | .20  |  |

|       | 6.4                   | Solutions to noise voltages and noise currents                                |      |  |

|       |                       | (informative) Nodal equation                                                  |      |  |

|       |                       | (informative) Example of black box modelling                                  |      |  |

| Bib   | liogra                | ohy                                                                           | .28  |  |

| T: ~. | 1                     | Integrated singuit and its modelling board                                    | c    |  |

| _     |                       | - Integrated circuit and its modelling board                                  |      |  |

| _     |                       | - Basic ICEM-CE model structure for an IC                                     |      |  |

|       |                       | - Representation of the integrated circuit and its modelling board by ICEM-CE |      |  |

| •     |                       | - Structure of the ICEM-CE for IC black box modelling                         |      |  |

| Figi  | ure 5                 | - IC Black box model structure                                                | . 12 |  |

| Fig   | ure 6                 | - IC black box model description with circuit elements                        | . 13 |  |

| Figi  | ure 7                 | - Setup for extraction of equivalent IAs                                      | . 14 |  |

| Figi  | ure 8 -               | - Definition of phase                                                         | . 15 |  |

| Figi  | ure 9 -               | - Setup for extraction of equivalent PDN                                      | . 16 |  |

| Figi  | ure 10                | - Setup for extraction of equivalent IAs and PDN                              | .16  |  |

| Figi  | ure 11                | - Configuration of the application board                                      | . 18 |  |

|       |                       | 2 – Setup for simulation of the application board                             |      |  |

| _     |                       | 1 – The ICEM-CE model                                                         |      |  |

| _     |                       | 2 – Spectrum of equivalent IA                                                 |      |  |

| _     |                       | 3 – Calculated admittances                                                    |      |  |

| _     |                       | 4 – Noise voltage and noise current                                           |      |  |

| гıgl  | uit D.                | + - NOISE VUITAYE AND NOISE GUITENL                                           | . 41 |  |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### **EMC IC MODELLING -**

#### Part 2-1: Theory of black box modelling for conducted emission

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

The main task of IEC technical committees is to prepare International Standards. However, a technical committee may propose the publication of a technical report when it has collected data of a different kind from that which is normally published as an International Standard, for example "state of the art".

IEC 62433-2-1, which is a technical report, has been prepared by subcommittee 47A: Integrated circuits, of IEC technical committee 47: Semiconductor devices.

The text of this technical report is based on the following documents:

| Enquiry draft | Report on voting |

|---------------|------------------|

| 47A/826A/DTR  | 47A/834/RVC      |

Full information on the voting for the approval of this technical report can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

A list of all parts of IEC 62433 series, under the general title *EMC IC modelling*, can be found on the IEC website.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- · reconfirmed,

- withdrawn,

- replaced by a revised edition, or

- amended.

IMPORTANT – The 'colour inside' logo on the cover page of this publication indicates that it contains colours which are considered to be useful for the correct understanding of its contents. Users should therefore print this document using a colour printer.

#### **EMC IC MODELLING -**

#### Part 2-1: Theory of black box modelling for conducted emission

#### 1 Scope

This part of IEC 62433-2-1 covers black box modelling which has the potential to make the modelling of conducted emission very simple, very fast, and can provide complete protection of proprietary information of IC vendors.

This technical report is intended to provide the theoretical background on black box modelling for IC conducted emission.

#### 2 Integrated circuit and modelling board

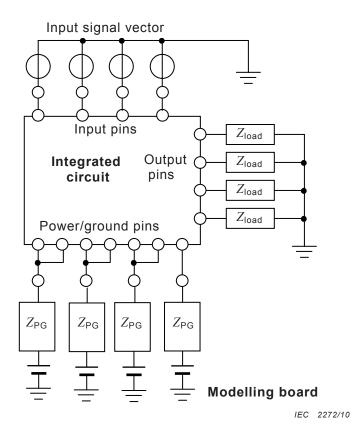

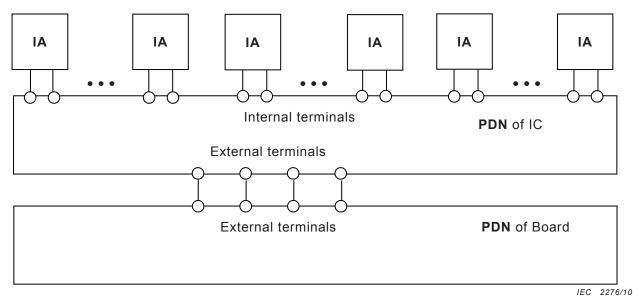

Figure 1 shows an integrated circuit (IC) and a modelling board. The IC is equipped with power/ ground pins, output pins and input pins. Usually an IC requires different power supply connections, namely, to supply digital cores, I/Os, and analogue circuits. Each one of these power supplies may have plural pins.

An IC cannot be activated by itself. To activate the IC properly, the IC has to be provided with power supplies, a set of input signals or an input signal vector, and appropriate loads for output pins.

To achieve these requirements, the modelling board is used. The modelling board provides minimum requirements for the activation. It supplies power, and input signals to the IC, and it gives typical loads for the output pins. In addition, power/ ground pins of the same category are connected to each other in the modelling board resulting in one terminal for each category of the power/ ground supply at the interface of the modelling board.

The board is also used for parameter extractions for modelling the IC. The IC modelling includes the board. The relationship between the IC modelling and the modelling board is just like the relationship between measured data and measurement board that affects measurement data. Therefore the modelling board should be as simple and general as possible.

Figure 1a) - Entire structure

Figure 1b) - Structure of the IC part

Figure 1 - Integrated circuit and its modelling board

TR 62433-2-1 © IEC:2010

#### 3 Assumptions

#### 3.1 ICEM-CE

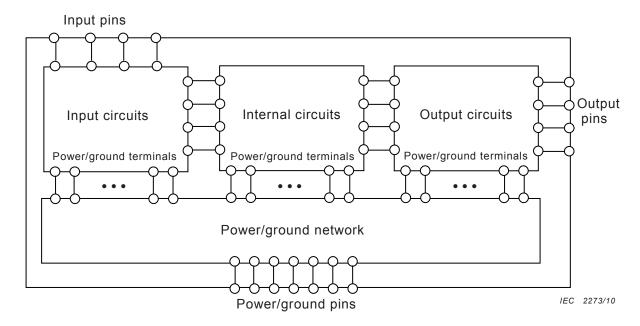

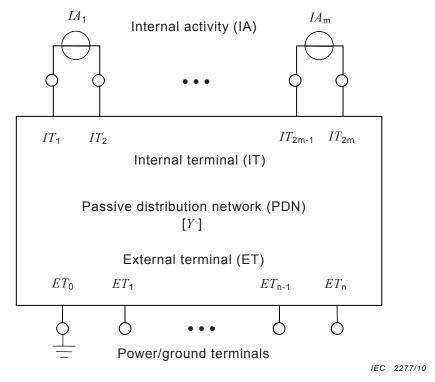

ICEM-CE is a macro model that approximates conducted emission behaviour of an IC using two types of components, internal activity (IA) and passive distribution network (PDN) as shown in Figure 2. These two types of components are connected through internal terminals (ITs).

The IAs represent noise sources that originate in switching of active devices within the IC. The PDN represents noise propagation characteristics from the internal terminals to the external terminals (ETs).

The black box modelling is based on this ICEM-CE model structure.

Figure 2 - Basic ICEM-CE model structure for an IC

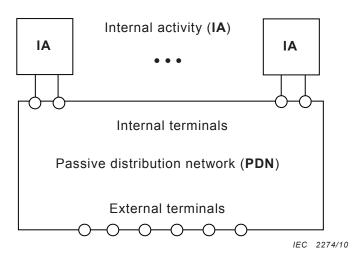

Figure 3 shows how to make an ICEM-CE model for the example of an IC and its modelling board shown in Figure 1. Figure 3a) shows the assignment of IA and PDN. The IA part includes input vector generators and output loads on the modelling board. The PDN part consists of the IC PDN part and Board PDN part. The IC PDN part consists of the power/ ground network of the die and the package of the IC. Figure 3b) shows the ICEM-CE structure of the IC and its modeling board with IAs and PDNs.

Figure 3a) - IA and PDN assignment

Figure 3b) - ICEM-CE representation

Figure 3 - Representation of the integrated circuit and its modelling board by ICEM-CE

#### 3.2 Black box model

In black box modelling, the PDN is described using a numerical matrix. To represent the PDN using a matrix, the PDN is assumed to be a linear circuit. Although the PDN is usually non-linear, this assumption is generally valid because noise voltages are small enough.

The elements of the matrix depend on noise frequency. Therefore, the PDN and the IAs should be described in frequency domain, and the PDN and IAs should be given for each frequency concerned.

The PDN can be represented either by an impedance matrix or an admittance matrix. This technical report uses an admittance matrix because admittance is more convenient than impedance to combine other models to the black box model.

#### 4 Modelling

#### 4.1 Terminals and objectives

As shown in Figure 1 and Figure 3, an input signal vector is applied to the IC through input terminals. The signal vector activates the IC and it causes IAs inside the IC. Therefore, the voltages and currents of the input terminals are conditions for the modelling. Noise voltages and currents at the input terminals are not the objectives of the modelling.

For the output pins of the IC, the modelling board provides typical loads. These loads generate IAs at the output circuits of the IC and consequently, from the IAs noise voltages and noise currents appear at the power/ ground terminals. This effect is included into the black box modelling. Output terminals themselves are also a source of conducted emissions, but the black box modelling given in this technical report cannot handle these emissions, because the characteristics of output circuits are non-linear. To simulate conducted emissions through output terminals, other black box modelling such as IMIC or IBIS has to be combined with this black box modelling.

Users cannot manipulate the internal terminals shown in Figure 2 that connect the IAs to the PDN. Therefore, the noise voltages and noise currents of internal terminals are also not the objectives of the black box modelling. But for the first step of this study, these terminals have to be used for the modelling, because these terminals provide the noise sources to the PDN. They are necessary particularly when a model is built from design data.

As the result, the objectives of the black box modelling are to provide models that can be used for numerical calculation of conducted emissions through power and ground terminals of an IC, which is applicable for an application board.

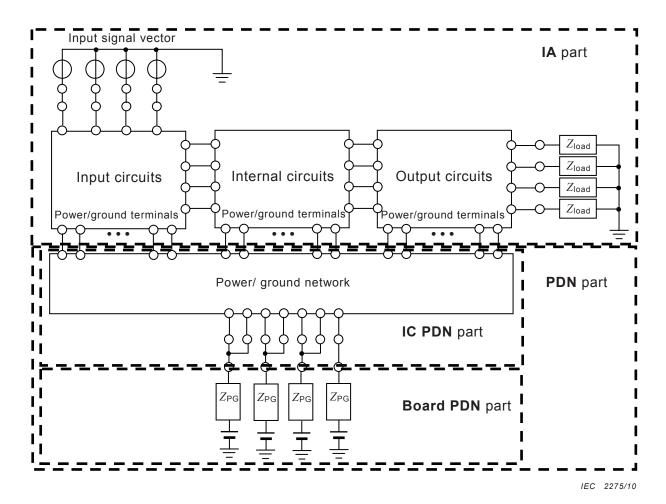

The ICEM-CE model structure for the black box modelling is shown in Figure 4. The IAs are expressed by current sources, and the PDN is given as an admittance matrix.

The noise voltages of the power/ ground terminals are defined with reference to a reference ground terminal (ET0) that is directly connected to the reference plane of the modelling board. The other power/ ground terminals of the PDN are named as ETx. The value of n is the number of power/ ground terminals minus one. The number of IAs is m. Therefore there are  $2 \cdot m$  internal terminals, and these terminals are named as ITx as shown in Figure 4.

Figure 4 - Structure of the ICEM-CE for IC black box modelling

#### 4.2 Admittance matrix

The PDN in Figure 4 is assumed to be a linear circuit. Therefore, the PDN can be expressed using an admittance matrix based on the nodal analysis method. The equation that expresses the IC, shown as Figure 4, is given below.

Here,  $V_{\rm ETx}$  and  $I_{\rm ETx}$  are the noise voltage and the noise current of ETx, respectively.  $V_{\rm ITx}$  and  $I_{\rm ITx}$  represent the noise voltage and the noise current of ITx, respectively.

NOTE Equation 1 describes the PDN without using variables of voltages and currents for internal nodes, which connect passive elements making up the PDN. Annex A gives the proof of the equation.

The admittance matrix is regular and its dimension is (n+2m, n+2m). For simplicity, Equation (1) is represented using sub-matrices and vectors as follows. In this equation, IAs substitute the currents of the internal terminals.

$$\begin{bmatrix}

[Y_{\mathsf{ET}\,\mathsf{ET}}] & [Y_{\mathsf{ET}\,\mathsf{IT}}] \\

[Y_{\mathsf{IT}\,\mathsf{ET}}] & [Y_{\mathsf{IT}\,\mathsf{IT}}]

\end{bmatrix} \times \begin{bmatrix}

[V_{\mathsf{ET}}] \\

[V_{\mathsf{IT}}]

\end{bmatrix} = \begin{bmatrix}

[I_{\mathsf{ET}}] \\

[I_{\mathsf{IT}}]

\end{bmatrix}$$

(2)

where,

TR 62433-2-1 © IEC:2010

$[Y_{\mathsf{ETET}}]$  is the regular admittance sub-matrix that represents interactions between ETs;

$[Y_{ET,IT}]$  is the admittance sub-matrix that represents interactions between ETs and ITs;

$[Y_{\mathsf{ITET}}]$  is the admittance sub-matrix that represents interactions between ITs and ETs;

$[Y_{|T||T}]$  is the regular admittance sub-matrix that represents interactions between ITs;

$[V_{\text{FT}}]$  is the voltage vector that represents noise voltages of ETs;

$[V_{\rm IT}]$  is the voltage vector that represents noise voltages of ITs;

$I_{FT}$  is the current vector that represents noise currents of ETs; and

$I_{\rm IT}$  is the current vector that represents noise currents of ITs.

$[I_{\rm IT}]$  is given as follows.

$$\begin{bmatrix} I_{1T} \end{bmatrix} = \begin{bmatrix} IA \end{bmatrix} \equiv \begin{bmatrix} IA_1 \\ -IA_1 \\ \vdots \\ IA_m \\ -IA_m \end{bmatrix}$$

(3)

#### 4.3 Matrix compaction

$[V_{\rm IT}]$  is eliminated out from Equation (2), as follows.

Equation (2) can be expanded into following two equations, combining Equation (3).

$$[Y_{\mathsf{FT}\,\mathsf{FT}}] \times [V_{\mathsf{FT}}] + [Y_{\mathsf{FT}\,\mathsf{IT}}] \times [V_{\mathsf{IT}}] = [I_{\mathsf{FT}}] \tag{4}$$

$$[Y_{\mathsf{IT}\,\mathsf{ET}}] \times [V_{\mathsf{ET}}] + [Y_{\mathsf{IT}\,\mathsf{IT}}] \times [V_{\mathsf{IT}}] = [IA]$$

$$(5)$$

From Equation (5),  $[V_{\text{IT}}]$  is obtained as follows.

$$[V_{\mathsf{IT}}] = [Y_{\mathsf{IT}\,\mathsf{IT}}]^{-1} \times ([IA] - [Y_{\mathsf{IT}\,\mathsf{ET}}] \times [V_{\mathsf{ET}}])$$

(6)

By substituting Equation (6) by Equation (4),  $[V_{\text{IT}}]$  can be eliminated out from Equation (4).

$$([Y_{\text{ET} \, \text{ET}}] - [Y_{\text{ET} \, \text{IT}}] \times [Y_{\text{IT} \, \text{IT}}]^{-1} \times [Y_{\text{IT} \, \text{ET}}]) \times [V_{\text{ET}}] = [I_{\text{ET}}] - [Y_{\text{ET} \, \text{IT}}] \times [Y_{\text{IT} \, \text{IT}}]^{-1} \times [IA]$$

(7)

The coefficient of  $[V_{\rm ET}]$  in the left-hand side is an admittance matrix whose dimension is (n, n). And the second term of the right-hand side is a current vector with n-dimension. The dimension of  $[I\!A']$  is n, and the dimension of  $[Y'_{\rm ETET}]$  is (n, n). Therefore,  $[I\!A']$  and  $[Y'_{\rm ETET}]$  can be defined as follows.

$$[IA'] = -[Y_{\mathsf{ET}\,\mathsf{IT}}] \times [Y_{\mathsf{IT}\,\mathsf{IT}}]^{-1} \times [IA]$$

(8)

$$[Y'_{\text{ETET}}] = [Y_{\text{ETET}}] - [Y_{\text{ETIT}}] \times [Y_{\text{ITIT}}]^{-1} \times [Y_{\text{ITET}}]$$

(9)

Then, Equation (7) becomes very simple.

$$[Y'_{\mathsf{ET}\,\mathsf{ET}}] \times [V_{\mathsf{ET}}] = [I_{\mathsf{ET}}] + [IA'] \tag{10}$$

#### 4.4 Black box model structure

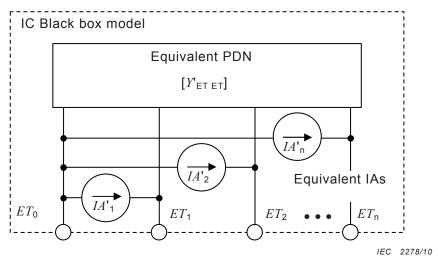

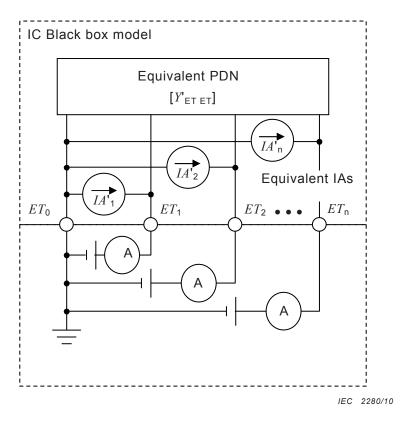

In Equations (8) and (9), [IA'] and  $[Y'_{\mathsf{ETET}}]$  are constant. Therefore [IA'] and  $[Y'_{\mathsf{ETET}}]$  are named as "equivalent internal activities (equivalent IAs)" and "equivalent passive distribution network (equivalent PDN)", respectively.

Equation (10) means that the black box model structure consists of an equivalent PDN and equivalent IAs as illustrated in the dotted area of Figure 5.

Compared with Figure 4, the IAs at the internal terminals are modified and transferred to the parallel positions to the external terminals. And the PDN is modified and simplified.

Figure 5 - IC Black box model structure

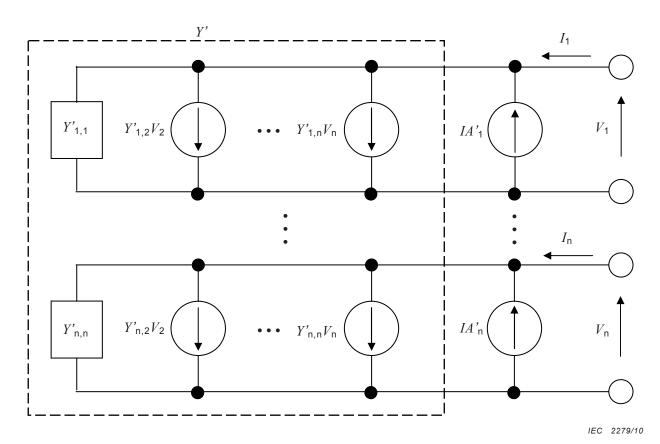

The IC black box model structure, as shown in Figure 5, is modelled using the expression having the (n+1) external terminals including the reference, where the number of the independent terminal voltage is n. Equation (10) is the Y matrix expression that determines the n external terminal voltages except for the reference as independent variables, and it is the n port circuit which has the reference terminal as the common negative terminal and the other terminals as the positive terminals. A n port circuit of black box model is expressed with circuit elements as shown in Figure 6. It consists of the parallel connection of passive elements having the admittance of the diagonal elements of the Y matrix, voltage controlled current sources having the current of the product of the non-diagonal element value and the other port voltage, and the independent current source having the current calculated from Equation (8).

The Y matrix expression of Equation (10) can be converted into an expression using Z or S matrices easily using conversion formulas.

Figure 6 - IC black box model description with circuit elements

#### 5 Parameter extractions

#### 5.1 General

The black box model for conducted emission consists of two components, the equivalent IAs and the equivalent PDN. To build a black box model from measurements, elements of these two components should be obtained. This clause describes the methods used to obtain these components from measurements.

The equivalent IAs depend on the operational mode and power supply condition of the IC. Therefore, the typical power supply condition and the repetitive specific input signal vector that corresponds to the operational mode should be applied to the power/ ground terminals and the input terminals of the modelling board during the measurements of equivalent IAs, respectively.

The equivalent PDN is assumed as a linear function, but it actually depends on voltages. Therefore, the typical power supply is given to the power/ground terminals of the modelling board during the measurements. Relatively small signals should be used for the measurements to assure the assumption is valid.

#### 5.2 Equivalent internal activities

From Equation (10), the equivalent noise current sources can be,

$$[IA'] = -[I_{\text{FT}}], \text{ when } [V_{\text{FT}}] = [0]$$

(11)

This means that the equivalent IAs can be obtained by measuring the  $[I_{\rm ET}]$  under the condition that all the external terminals are RF shorted to the reference terminal. The configuration of the measurement setup is shown in Figure 7.

Figure 7 - Setup for extraction of equivalent IAs

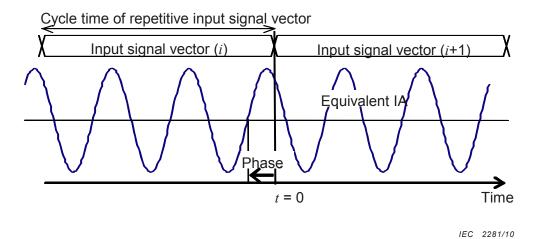

Each value of  $[I_{\text{ET}}]$  is a complex number; therefore, the amplitude and phase for each current element should be measured.

One way is to measure the amplitude and phase in frequency domain directly for each external terminal for each frequency concerned. In this method, the phases should be determined with reference to the cycle of the input signal vector. The definition is given in Figure 8.

Figure 8 - Definition of phase

The other way is to measure the waveforms of the external terminals in the time domain. The time is also determined with reference to the start of the cycle of the input signal vector. After that, the waveforms should be converted into frequency domain using the Fourier transformation.

#### 5.3 Equivalent passive distribution network

Now all elements of the equivalent IAs are already known. Therefore each element of the admittance matrix of equivalent PDN can be derived from Equation (10) as shown in Equation (12).

$$Y'_{ij} = \frac{I_i + IA'_i}{V_j}$$

, at all  $V_{i \neq j} = 0$  (12)

Here,  $I_i$  is the measured current while  $V_j$  is the given signal voltage for the measurement. The configuration of the measurement setup for  $Y'_{ij}$  is shown in Figure 9. In this measurement, the phase of  $V_j$  and  $V_j$  and  $V_j$  should be given with reference to the cycle of the input vector, because the input signal vector determines the phase of IA.

Figure 9 – Setup for extraction of equivalent PDN

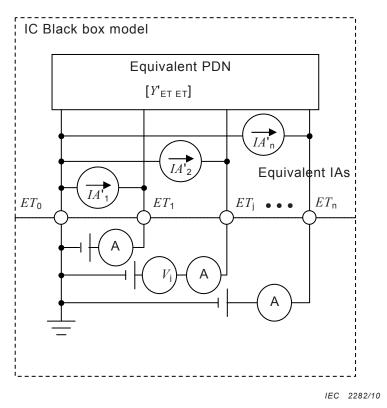

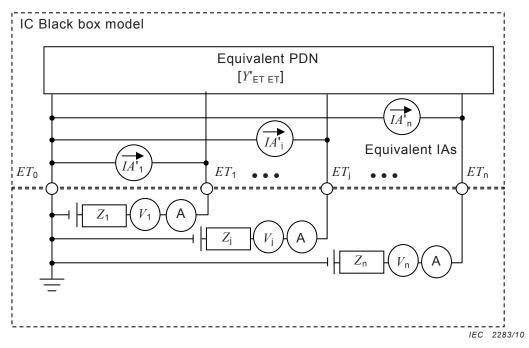

#### 5.4 Parameter extraction method using finite impedance termination

The parameter extraction method explained above is the one by using RF short termination for each external port. In reality a complete RF short is difficult for some cases, in particular for measurements of the real devices. Thus a parameter extraction method using finite impedance termination is described herein.

Figure 10 - Setup for extraction of equivalent IAs and PDN

Figure 10 shows the setup structure of limited impedance termination. Each terminal is terminated with a series of a DC power supply, an AC voltage source, a current meter, and a finite impedance element. The circuit of Figure 10 can be expressed using n independent equations. The number of elements of Y is  $n^2$  and that of the IA' is n. Then the number of unknowns is n(n+1). Then n(n+1) equations are necessary to get all element values of Y and IA'. As the circuit of Figure 10 has n independent equations for each excitation, it needs n+1 independent sets of external AC voltage sources to determine the all unknown values.

For Figure 10, its terminal condition is expressed as below.

$$[V_{\mathsf{FT}}] = [Z_{\mathsf{PSPS}}] \times [I_{\mathsf{FT}}] + [V] \tag{13}$$

$$[I_{\text{ET}}] = [Z_{\text{PSPS}}]^{-1} \times [[V_{\text{ET}}] - [V]] = [Y_{\text{PSPS}}] \times [[V_{\text{ET}}] - [V]]$$

(14)

The combination of Equations (10) and (13), or Equations (10) and (14), give the following equations.

$$[Y'_{ETET}] \times [[Z_{PSPS}] \times [I_{ET}] + [V]] = [I_{ET}] + [IA']$$

(15)

$$[Y'_{\mathsf{FTFT}}] \times [V_{\mathsf{FT}}] = [[Y_{\mathsf{PSPS}}] \times [[V_{\mathsf{FT}}] - [V]]] + [IA']$$

(16)

By using Equation (15), the combination according to (n+1) of input [V] and its response  $[I_{\text{ET}}]$  leads  $[Y'_{\text{ETET}}]$  and [IA']. And by using Equation (16), the combination according to (n+1) of input [V] and its response  $[V_{\text{ET}}]$  leads  $[Y'_{\text{ETET}}]$  and [IA'].

To do this for example, we can input one AC voltage source at one external terminal while setting all other AC sources to zero, and repeat this for each external terminal. There will also be one case where all AC sources are zero. When we solve the equations from real measurement data, we can add the other drive patterns (the drive from plural ports) because with measurement error, it is useful to use the least-squares method to optimize the parameters.

#### 5.5 Black box model including the reference terminal

The reference terminal is not included in [IA'] and [Y'] described above. When we implement ICs on a board, expanding [IA'] and [Y'] so that they include the reference terminal is convenient because generally the reference terminal is necessary when an IC is placed on a board like the other terminals. As shown in detail in Annex A, IA' element of the reference terminal is calculated from the summation of IA' elements with the reference terminal set as zero. The Y element of the reference terminal is calculated from the summation of Y elements where the reference terminal along a row or a column is zero.

#### 6 Implementation

#### 6.1 General

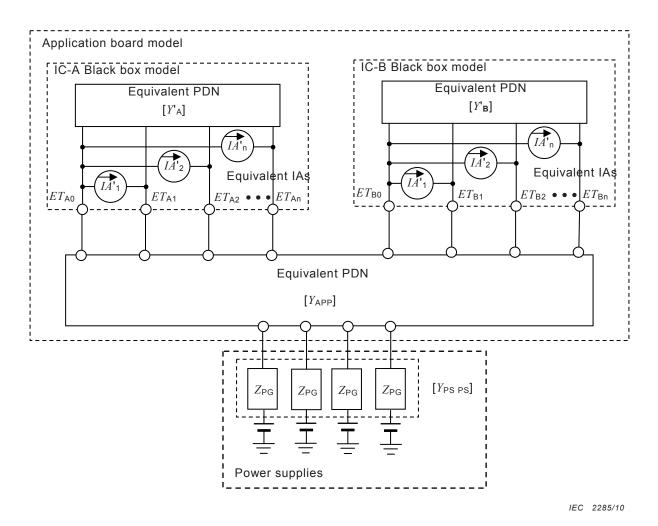

This clause describes the methodology for implementation of the black box models into an application board, taking as an example an application board with two black box models. An example is given in Annex B.

#### 6.2 Configuration of the application board

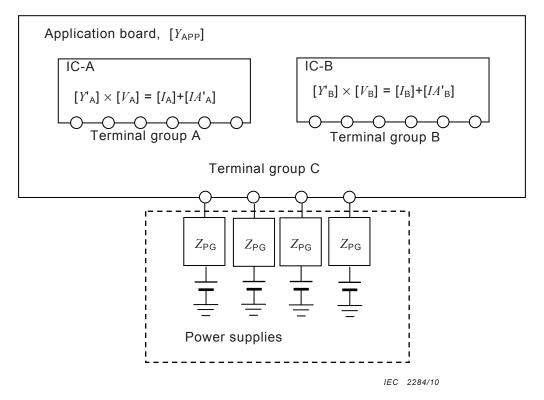

The configuration of the application board is shown in Figure 11. The board contains two ICs, IC-A and IC-B, and these are connected to the application board using the terminal group A and the terminal group B, respectively.

The board is also equipped with the terminal group C. The application board receives power supplies and ground from the outside environment using these terminals.

Figure 11 - Configuration of the application board

The components for simulation of the application board consist of IC-A black box model, IC-B black box model, PDN model of the power/ ground network of the application board, and models of the power supplies. The connection of the components for simulation is shown in Figure 12.

Figure 12 - Setup for simulation of the application board

Let's suppose that the black box models for IC-A and IC-B, and the admittance matrix of the application board are already known as follows. Each IC model used here is the black box model including its reference terminal.

$$[Y'_{\mathsf{A}}] \times [V_{\mathsf{A}}] = [I_{\mathsf{A}}] + [IA'_{\mathsf{A}}] \tag{17}$$

$$[Y_B] \times [V_B] = [I_B] + [IA_B]$$

(18)

Here,  $[V_{\rm A}]$ ,  $[V_{\rm B}]$  and  $[V_{\rm C}]$  are the noise voltage vectors of terminal group A, B and C, respectively.  $-[I_{\rm A}]$ ,  $-[I_{\rm B}]$  and  $[I_{\rm C}]$  are the noise current vectors of terminal group A, B and C, respectively.

And the admittance matrix of the application board is given as follows.

$$[Y_{\mathsf{APP}}] = \begin{bmatrix} [Y_{\mathsf{A}\,\mathsf{A}}] & [Y_{\mathsf{A}\,\mathsf{B}}] & [Y_{\mathsf{A}\,\mathsf{C}}] \\ [Y_{\mathsf{B}\,\mathsf{A}}] & [Y_{\mathsf{B}\,\mathsf{B}}] & [Y_{\mathsf{B}\,\mathsf{C}}] \\ [Y_{\mathsf{C}\,\mathsf{A}}] & [Y_{\mathsf{C}\,\mathsf{B}}] & [Y_{\mathsf{C}\,\mathsf{C}}] \end{bmatrix}$$

(19)

In Equation (19), the sub-matrix  $[Y_{AB}]$  represents the interactions between terminal A and terminal B, the sub-matrix  $[Y_{AC}]$  represents interactions between terminal A and terminal C, etc.

#### 6.3 Implementation of black box models

The whole application board can be expressed by Equation (20) as shown below.

$$\begin{bmatrix}

[Y_{AA}] & [Y_{AB}] & [Y_{AC}] \\

[Y_{BA}] & [Y_{BB}] & [Y_{BC}]

\end{bmatrix} \times \begin{bmatrix} [V_{A}] \\

[V_{B}] \\

[V_{C}] \end{bmatrix} = \begin{bmatrix} -[I_{A}] \\

-[I_{B}] \\

[I_{C}]

\end{bmatrix}$$

(20)

The currents of terminal group A and B have negative signs, since the noise currents to the IC models and the noise currents to the application board are opposite.

$[I_A]$  and  $[I_B]$  in Equation (20) can be eliminated out by substituting these using Equation (17) and (18). As the result, the following equation that represents the whole system is obtained.

$$\begin{bmatrix}

[Y_{AA}] + [Y'_{A}] & [Y_{AB}] & [Y_{AC}] \\

[Y_{BA}] & [Y_{BB}] + [Y'_{B}] & [Y_{BC}] \\

[Y_{CA}] & [Y_{CB}] & [Y_{CC}]

\end{bmatrix} \times \begin{bmatrix}

[V_{A}] \\

[V_{B}] \\

[V_{C}] \end{bmatrix} = \begin{bmatrix}

[IA'_{A}] \\

[IA'_{B}] \\

[IC]

\end{bmatrix}$$

(21)

#### 6.4 Solutions to noise voltages and noise currents

Initially, one supposes that as a general boundary condition of the system, an admittance matrix of power supplies  $[Y_{PSPS}]$  is given. The relationship between  $[V_C]$  and  $[I_C]$  is given by the following equation.

$$[Y_{\mathsf{PSPS}}] \times [V_{\mathsf{C}}] = -[I_{\mathsf{C}}] \tag{22}$$

Equation (21) becomes Equation (23) by substituting  $[I_{\mathbb{C}}]$  using Equation (22).

$$\begin{bmatrix}

[Y_{AA}] + [Y'_{A}] & [Y_{AB}] & [Y_{AC}] \\

[Y_{BA}] & [Y_{BB}] + [Y'_{B}] & [Y_{BC}] \\

[Y_{CA}] & [Y_{CB}] & [Y_{CC}] + [Y_{PSPS}]

\end{bmatrix} \times \begin{bmatrix}

[V_{A}] \\

[V_{B}] \\

[V_{C}]

\end{bmatrix} = \begin{bmatrix}

[II'_{A}] \\

[II'_{B}] \\

[0]$$

(23)

Then, the general solutions of  $[V_{\rm A}]$ ,  $[V_{\rm B}]$  and  $[V_{\rm C}]$  can be derived as follows.

$$\begin{bmatrix}

[V_{A}] \\

[V_{B}] \\

[V_{C}]

\end{bmatrix} = \begin{bmatrix}

[Y_{AA}] + [Y'_{A}] & [Y_{AB}] & [Y_{AC}] \\

[Y_{BA}] & [Y_{BB}] + [Y'_{B}] & [Y_{BC}] \\

[Y_{CA}] & [Y_{CB}] & [Y_{CC}] + [Y_{PSPS}]

\end{bmatrix}^{-1} \times \begin{bmatrix}

[II'_{A}] \\

[II'_{B}] \\

[0]$$

(24)

And the general solutions of  $[I_A]$ ,  $[I_B]$  and  $[I_C]$  are obtained from Equation (20) using voltage vectors given in Equation (24).

$$\begin{bmatrix} -\begin{bmatrix} I_{A} \end{bmatrix} \\ -\begin{bmatrix} I_{B} \end{bmatrix} \\ \begin{bmatrix} I_{C} \end{bmatrix} \end{bmatrix} = \begin{bmatrix} \begin{bmatrix} Y_{AA} \end{bmatrix} & \begin{bmatrix} Y_{AB} \end{bmatrix} & \begin{bmatrix} Y_{AC} \end{bmatrix} & \begin{bmatrix} Y_{AC} \end{bmatrix} \\ \begin{bmatrix} Y_{BA} \end{bmatrix} & \begin{bmatrix} Y_{BB} \end{bmatrix} & \begin{bmatrix} Y_{BC} \end{bmatrix} & \begin{bmatrix} Y_{CC} \end{bmatrix} \end{bmatrix} \times \begin{bmatrix} \begin{bmatrix} V_{A} \end{bmatrix} & \begin{bmatrix} V_{CC} \end{bmatrix} \end{bmatrix}$$

Second, one considers a specific boundary condition that the impedances of the power supplies are low enough compared to other components. This condition is specific but it is a normal assumption for many applications. In this case,  $[V_C]$  can be assumed as [0].

The particular solutions of the noise voltage vectors for this condition are obtained from Equation (21).

$$\begin{bmatrix}

[Y_{AA}] + [Y'_{A}] & [Y_{AB}] & [Y_{AC}] \\

[Y_{BA}] & [Y_{BB}] + [Y'_{B}] & [Y_{BC}] \\

[Y_{CA}] & [Y_{CB}] & [Y_{CC}]

\end{bmatrix} \times \begin{bmatrix}

[V_{A}] \\

[V_{B}] \\

[0]\end{bmatrix} = \begin{bmatrix}

[IA'_{A}] \\

[IA'_{B}] \\

[I_{C}]

\end{bmatrix}$$

(26)

$$\begin{bmatrix} \begin{bmatrix} V_{\mathsf{A}} \end{bmatrix} \\ \begin{bmatrix} V_{\mathsf{B}} \end{bmatrix} \end{bmatrix} = \begin{bmatrix} \begin{bmatrix} Y_{\mathsf{A}} & A \end{bmatrix} + \begin{bmatrix} Y_{\mathsf{A}} & B \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{A}} & B \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{A}} & B \end{bmatrix} & \begin{bmatrix} IA'_{\mathsf{A}} & B \end{bmatrix} \\ \begin{bmatrix} Y_{\mathsf{B}} & A \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{B}} & A \end{bmatrix} + \begin{bmatrix} Y_{\mathsf{B}} & A \end{bmatrix} & \begin{bmatrix} IA'_{\mathsf{B}} & A \end{bmatrix} \\ \end{bmatrix} \tag{27}$$

By setting  $[V_C]$  as [0] in Equation (20), the noise current vectors are derived as follows.

$$\begin{bmatrix} -\begin{bmatrix} I_{\mathsf{A}} \end{bmatrix} \\ -\begin{bmatrix} I_{\mathsf{B}} \end{bmatrix} \\ \begin{bmatrix} I_{\mathsf{C}} \end{bmatrix} \end{bmatrix} = \begin{bmatrix} \begin{bmatrix} Y_{\mathsf{A}\,\mathsf{A}} \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{A}\,\mathsf{B}} \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{A}\,\mathsf{C}} \end{bmatrix} \\ \begin{bmatrix} Y_{\mathsf{B}\,\mathsf{A}} \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{B}\,\mathsf{C}} \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{B}\,\mathsf{C}} \end{bmatrix} \\ \begin{bmatrix} Y_{\mathsf{C}\,\mathsf{A}} \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{C}\,\mathsf{C}} \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{C}\,\mathsf{C}} \end{bmatrix} \end{bmatrix} \times \begin{bmatrix} \begin{bmatrix} V_{\mathsf{A}} \end{bmatrix} \\ \begin{bmatrix} V_{\mathsf{B}} \end{bmatrix} \end{bmatrix}$$

(28)

$$\begin{bmatrix} -\begin{bmatrix} I_{A} \end{bmatrix} \\ -\begin{bmatrix} I_{B} \end{bmatrix} \\ \begin{bmatrix} I_{C} \end{bmatrix} \end{bmatrix} = \begin{bmatrix} \begin{bmatrix} Y_{AA} \end{bmatrix} & \begin{bmatrix} Y_{AB} \end{bmatrix} & \begin{bmatrix} Y_{AB} \end{bmatrix} \\ \begin{bmatrix} Y_{BA} \end{bmatrix} & \begin{bmatrix} \begin{bmatrix} V_{A} \end{bmatrix} \end{bmatrix} & \begin{bmatrix} \begin{bmatrix} V_{A} \end{bmatrix} \end{bmatrix}$$

$$\begin{bmatrix} I_{C} \end{bmatrix} & \begin{bmatrix} I_{C}$$

As described in this clause, using the black box model, the noise voltages and the noise currents of an application board can be obtained by simple matrix calculations.

## Annex A (informative)

#### Nodal equation

#### A.1 Purpose

This annex is intended to review the fundamentals of the nodal equation. The annex gives proof of Equation (1) that represents characteristics of a PDN using only its external nodes; i.e. external terminals and internal terminals.

#### A.2 Review

Consider a passive distribution network with (n + 1) nodes. The 0 node is the reference node. For each node, the following equation is derived from Kirchhoff's first law.

$$I_{i} = \sum_{j \neq i} y_{ij} \times (V_{i} - V_{j})$$

(A.1)

$$I_{i} = \sum_{j \neq i} y_{ij} \times V_{i} - \sum_{j \neq i} y_{ij} \times V_{j}$$

(A.2)

Here,  $V_{\rm i}$  and  $I_{\rm i}$  are the voltage and the current flowing into the node i, respectively.  $y_{\rm i\,j}$  is the admittance of the element that is located between node i and node j.

Using an admittance matrix, Equation (A.2) can be rewritten as a nodal equation as follows.

$$\begin{bmatrix} \sum_{j\neq 0} y_{0,j} & -y_{0,1} & \cdots & -y_{0,i-1} & -y_{0,i} & -y_{0,i+1} & \cdots & -y_{0,n-1} & -y_{0,n} \\ -y_{1,0} & \sum_{j\neq 1} y_{1,j} & \cdots & -y_{1,i-1} & -y_{1,i} & -y_{1,i+1} & \cdots & -y_{1,n-1} & -y_{1,n} \\ \vdots & \vdots & \ddots & \vdots & \ddots & \ddots & \ddots & \vdots \\ -y_{i-1,0} & -y_{i-1,1} & \sum_{j\neq i-1} y_{i-1,j} & -y_{i-1,i} & -y_{i-1,i+1} & \cdots & -y_{i-1,n-1} & -y_{i-1,n} \\ -y_{i,0} & -y_{i,1} & \cdots & -y_{i,i-1} & \sum_{j\neq i} y_{i,j} & -y_{i,j+1} & \cdots & -y_{i,n-1} & -y_{i,n} \\ -y_{i+1,0} & -y_{i+1,1} & \cdots & -y_{i+1,i-1} & -y_{i+1,i} & \sum_{j\neq i+1} y_{i+1,j} & \cdots & -y_{i+1,n-1} & -y_{i+1,n} \\ \vdots & \vdots & \ddots & \vdots & \ddots & \ddots & \vdots \\ -y_{n-1,0} & -y_{n-1,1} & \cdots & -y_{n-1,i-1} & -y_{n-1,i+1} & \cdots & y_{n-1,i} & -y_{n-1,i} \\ -y_{n,0} & -y_{n,1} & \cdots & -y_{n,i-1} & -y_{n,i+1} & \cdots & -y_{n,n-1} & \sum_{j\neq n} y_{n,j} \end{bmatrix}$$

$$(A.3)$$

The value of each diagonal element is the summation of admittances of passive elements that are connected to the corresponding node. The matrix is symmetrical because  $y_{ij} = y_{ji}$ .

In Equation (A.3) the summation of all elements in each column or each row becomes zero. Namely this matrix is singular. Therefore we usually use the partial matrix and the partial

vector except the reference node. With these relations, we can generate a matrix including the reference node from the partial matrix excluding the reference node.

#### A.3 Proof of Equation (1)

Consider the PDN that consists of n-nodes. And m-nodes are external nodes and n minus m nodes are internal nodes. Then, Equation (A.3) can be written as follows.

$$\begin{bmatrix} Y_{11} & . & Y_{1m} & Y_{1m+1} & . & Y_{1n} \\ . & . & . & . & . & . \\ \frac{Y_{m1}}{Y_{m+11}} & . & Y_{mm} & Y_{mm+1} & . & Y_{mn} \\ . & . & . & . & . & . \\ Y_{n1} & . & Y_{nm} & Y_{nm+1} & . & Y_{nn} \end{bmatrix} \cdot \begin{bmatrix} V_{1} \\ . \\ V_{m} \\ V_{m+1} \end{bmatrix} = \begin{bmatrix} I_{1} \\ . \\ V_{m} \\ I_{m+1} \\ . \\ V_{n} \end{bmatrix}$$

$$(A.4)$$

$$\begin{bmatrix} Y_{\mathsf{EE}} \\ Y_{\mathsf{IE}} \end{bmatrix} & \begin{bmatrix} Y_{\mathsf{EI}} \\ Y_{\mathsf{II}} \end{bmatrix} \times \begin{bmatrix} Y_{\mathsf{EI}} \\ Y_{\mathsf{II}} \end{bmatrix} = \begin{bmatrix} I_{\mathsf{E}} \\ I_{\mathsf{II}} \end{bmatrix}$$

(A.5)

where,

$[Y_{\text{FF}}]$  is the regular admittance matrix that represents interactions between external nodes;

$[Y_{E1}]$  is the matrix that represents admittances between external and internal nodes;

$[Y_{1F}]$  is the matrix that represents admittances between internal and external nodes;

$[Y_{11}]$  is the regular matrix that represents admittances between internal nodes;

$[V_{\rm F}]$  is the vector that represents voltages of external nodes;

$[V_1]$  is the vector that represents voltages of internal nodes;

$I_{\rm F}$  is the vector that represents currents of external nodes; and

$[I_1]$  is the vector that represents currents of internal nodes.

Equation (A.5) can be expanded into following two equations.

$$[Y_{EE}] \times [V_{E}] + [Y_{EI}] \times [V_{I}] = [I_{E}]$$

(A.6)

$$[Y_{|E}] \times [V_{E}] + [Y_{|I}] \times [V_{I}] = [I_{I}]$$

(A.7)

Note that  $[I_1]$  is [0], because the outside environment cannot access internal nodes. From Equation (A.7),  $[V_1]$  is obtained as follows.

$$[V_1] = [Y_{11}]^{-1} \times [Y_{1E}] \times [V_{E}]$$

(A.8)

By substituting Equation (A.8) into Equation (A.6),  $[V_1]$  can be eliminated.

$$([Y_{EE}] + [Y_{IE}] \times [Y_{II}]^{-1} \times [Y_{IE}]) \times [V_{E}] = [I_{E}]$$

(A.9)

The coefficient of  $\left[V_{\mathrm{E}}\right]$  is an admittance matrix that is represented only by external nodes.

# Annex B (informative)

#### Example of black box modelling

#### **B.1** Objective

This annex gives an example of black box modelling and its application taking an example of ICEM-CE model.

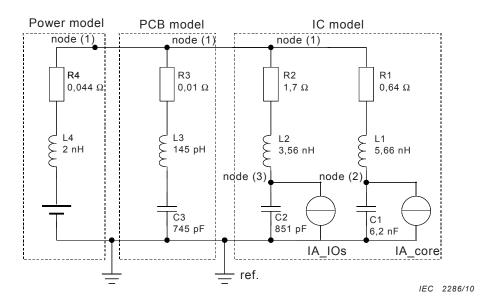

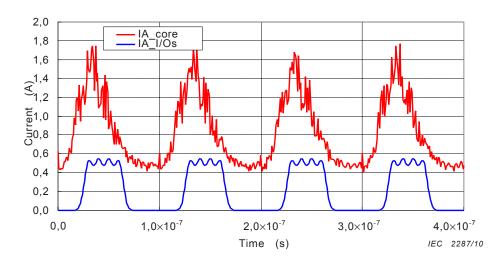

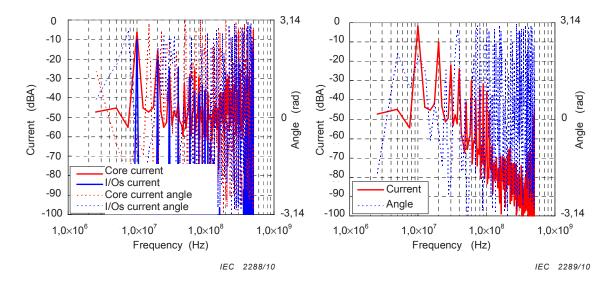

A diagram of the ICEM-CE model that includes the IC, PCB, and power source models is given in Figure A.1. The IC model has two IAs, an IA for core activity and an IA for I/O activity. And the IC model has one external terminal (node (1)), and two internal terminals (node (2), (3)). The IC is operated under a 10 MHz clock, and the operational mode needs four machine cycles. Therefore, the cycle time of the operation is 400 ns. The Waveforms of the IAs over the operational cycle time are given in Figure B.1b).

Figure B.1a) - Circuit diagram

Figure B.1b) - Waveforms of internal activities

Figure B.1 - The ICEM-CE model

#### B.2 Black box modelling

#### **B.2.1** Equivalent PDN

Equation (2) for the IC model becomes as Equation (B.1).

$$\begin{bmatrix} \frac{(R_{1}+j\omega L_{1})^{-1}+(R_{2}+j\omega L_{2})^{-1}}{-(R_{1}+j\omega L_{1})^{-1}} & -(R_{1}+j\omega L_{1})^{-1} & -(R_{2}+j\omega L_{2})^{-1} \\ -(R_{2}+j\omega L_{2})^{-1} & (R_{1}+j\omega L_{1})^{-1}+j\omega C_{1} & 0 \\ -(R_{2}+j\omega L_{2})^{-1} & 0 & (R_{2}+j\omega L_{2})^{-1}+j\omega C_{2} \end{bmatrix} \times \begin{bmatrix} V_{1} \\ V_{2} \\ V_{3} \end{bmatrix} = \begin{bmatrix} I_{1} \\ IA_{core} \\ IA_{I/OS} \end{bmatrix}$$

(B.1)

The admittance matrix of Equation (B.1) can be compacted using Equation (2). As a result, the admittance matrix, voltage vector and current vector become simple complex numbers as shown below.

$$Y'_{\mathsf{FTFT}} \times V_1 = I_1 + IA' \tag{B.2}$$

$$Y'_{\mathsf{ETET}} \equiv [Y_{\mathsf{ETET}}] - [Y_{\mathsf{ETIT}}] \times [Y_{\mathsf{ITIT}}]^{-1} \times [Y_{\mathsf{ITET}}]$$

(B.3)

#### B.2.2 Equivalent IA

According to Equation (8), the equivalent IA can be obtained using the following equation.  $IA_{\rm core}$  and  $IA_{\rm I/Os}$  can be derived from waveforms using Fourier transformation.

$$IA' = -[Y_{\mathsf{ET}\,\mathsf{IT}}] \times [Y_{\mathsf{IT}\,\mathsf{IT}}]^{-1} \times \begin{bmatrix} IA_{\mathsf{core}} \\ IA_{\mathsf{I/Os}} \end{bmatrix}$$

(B.4)

Figure B.2a) - IA\_core and IA\_I/Os

Figure B.2b) - Equivalent IA

Figure B.2 - Spectrum of equivalent IA

#### B.3 Noise voltage and noise current

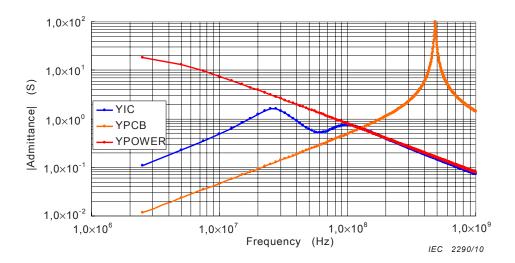

The PCB and power source models are given in Equation (B.5) and (B.6), respectively. Figure B.3 shows the calculated admittance of the IC, PCB and power source.

$$Y_{PCB} = \left(0.01 + j\omega \times 145E - 12 + \frac{1}{j\omega \times 745E - 12}\right)^{-1}$$

(B.5)

$$Y_{\text{Power}} = (0.044 + j\omega \times 2E - 9)^{-1}$$

(B.6)

Figure B.3 - Calculated admittances

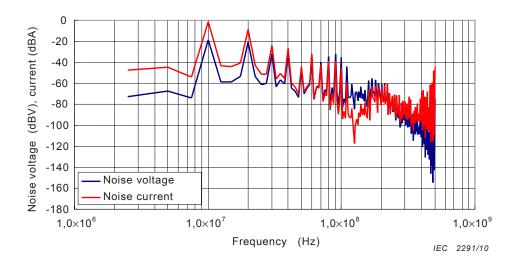

The noise voltage and noise current of node (1) can be calculated using the following equations. Figure B.4 shows the results.

$$V_1 = (Y'_{ETET} + Y_{PCB} + Y_{Power})^{-1} \times IA'$$

(B.7)

$$I_{PCB} + I_{Power} = (Y_{PCB} + Y_{Power}) \times V_1$$

(B.8)

Figure B.4 – Noise voltage and noise current

#### **Bibliography**

IEC 61967 (all parts), Integrated Circuits - Measurement of electromagnetic emissions

IEC 62014-1, Electronic design automation libraries – Part 1: Input/output buffer information specifications (IBIS version 3.2)

IEC/TS 62433-1, EMC IC modelling - Part 1: General modelling framework1

IEC/TS 62404, Logic digital integrated circuits – Specification for I/O Interface Model for Integrated Circuit (IMIC version 1.3)

<sup>1</sup> To be published.

### **British Standards Institution (BSI)**

BSI is the independent national body responsible for preparing British Standards and other standards-related publications, information and services. It presents the UK view on standards in Europe and at the international level. It is incorporated by Royal Charter.

#### **Revisions**

British Standards are updated by amendment or revision. Users of British Standards should make sure that they possess the latest amendments or editions.

It is the constant aim of BSI to improve the quality of our products and services. We would be grateful if anyone finding an inaccuracy or ambiguity while using this British Standard would inform the Secretary of the technical committee responsible, the identity of which can be found on the inside front cover.

Tel: +44 (0)20 8996 9001 Fax: +44 (0)20 8996 7001

BSI offers Members an individual updating service called PLUS which ensures that subscribers automatically receive the latest editions of standards.

Tel: +44 (0)20 8996 7669 Fax: +44 (0)20 8996 7001 Email: plus@bsigroup.com

### **Buying standards**

You may buy PDF and hard copy versions of standards directly using a credit card from the BSI Shop on the website **www.bsigroup.com/shop.** In addition all orders for BSI, international and foreign standards publications can be addressed to BSI Customer Services.

Tel: +44 (0)20 8996 9001 Fax: +44 (0)20 8996 7001 Email: orders@bsigroup.com

In response to orders for international standards, it is BSI policy to supply the BSI implementation of those that have been published as British Standards, unless otherwise requested.

#### Information on standards

BSI provides a wide range of information on national, European and international standards through its Knowledge Centre.

Tel: +44 (0)20 8996 7004 Fax: +44 (0)20 8996 7005 Email: knowledgecentre@bsigroup.com

Various BSI electronic information services are also available which give details on all its products and services.

Tel: +44 (0)20 8996 7111 Fax: +44 (0)20 8996 7048 Email: info@bsigroup.com

BSI Subscribing Members are kept up to date with standards developments and receive substantial discounts on the purchase price of standards. For details of these and other benefits contact Membership Administration

Tel: +44 (0)20 8996 7002 Fax: +44 (0)20 8996 7001 Email: membership@bsigroup.com

Information regarding online access to British Standards via British Standards Online can be found at **www.bsigroup.com/BSOL**

Further information about BSI is available on the BSI website at **www.bsi-group.com/standards**

### Copyright

Copyright subsists in all BSI publications. BSI also holds the copyright, in the UK, of the publications of the international standardization bodies. Except as permitted under the Copyright, Designs and Patents Act 1988 no extract may be reproduced, stored in a retrieval system or transmitted in any form or by any means – electronic, photocopying, recording or otherwise – without prior written permission from BSI. This does not preclude the free use, in the course of implementing the standard of necessary details such as symbols, and size, type or grade designations. If these details are to be used for any other purpose than implementation then the prior written permission of BSI must be obtained. Details and advice can be obtained from the Copyright & Licensing Manager.

Tel: +44 (0)20 8996 7070 Email: copyright@bsigroup.com

#### **BSI Group Headquarters**

389 Chiswick High Road London W4 4AL UK

Tel +44 (0)20 8996 9001 Fax +44 (0)20 8996 7001 www.bsigroup.com/standards