BS 5760-7: 1991 IEC 1025:1990

# Reliability of systems, equipment and components —

Part 7: Guide to fault tree analysis

# Committees responsible for this British Standard

The preparation of this British Standard was entrusted by the Quality, Management and Statistics Standards Policy Committee (QMS/-) to Technical Committee QMS/23, upon which the following bodies were represented:

Association for Consumer Research (ACRE)

Association of Consulting Engineers

British Gas plc

British Railways Board

Cable and Wireless plc

City University

Civil Aviation Authority

Cranfield Information Technology Institute

Cranfield Institute of Technology

Design Council

EEA (the Association of Electronics, Telecommunications and Business Equipment Industries)

Electricity Industry in United Kingdom

Electronic Components Industry Federation

Engineering Equipment and Materials Users' Association

GAMBICA (BEAMA Ltd.)

Institute of Petroleum

Institute of Quality Assurance

Institution of Electrical Engineers

Institution of Plant Engineers

Ministry of Defence

National Computing Centre Ltd.

Railway Industry Association of Great Britain

Safety and Reliability Society

Society of British Aerospace Companies Limited

Society of Motor Manufacturers and Traders Limited

United Kingdom Atomic Energy Authority

University of Technology, Loughborough

This British Standard, having been prepared under the direction of the Quality, Management and Statistics Standards Policy Committee, was published under the authority of the Standards Board and comes into effect on 20 December 1991

#### Amendments issued since publication

The following BSI references relate to the work on this standard: Committee reference QMS/2:

$\begin{array}{l} {\rm Committee\ reference\ QMS/23} \\ {\rm Draft\ 90/97821\ announced\ in} \\ {\it BSI\ News\ May\ 1991} \end{array}$

ISBN 0 580 20338 7

| Amd. No. | Date | Comments |

|----------|------|----------|

|          |      |          |

|          |      |          |

|          |      |          |

|          |      |          |

|          |      |          |

## Contents

|                                                        | Page               |

|--------------------------------------------------------|--------------------|

| Committees responsible                                 | Inside front cover |

| National foreword                                      | ii                 |

| Introduction                                           | 1                  |

| 1 Scope                                                | 1                  |

| 2 Normative references                                 | 1                  |

| 3 Definitions                                          | 1                  |

| 4 Symbols                                              | 1                  |

| 5 General                                              | 1                  |

| 5.1 Fault tree structure                               | 1                  |

| 5.2 Objectives                                         | 2                  |

| 5.3 Applications                                       | 2                  |

| 6 Principles                                           | 2                  |

| 6.1 General considerations                             | 2                  |

| 6.2 System structure                                   | 2                  |

| 6.3 Events considered                                  | 3                  |

| 6.4 Approaches                                         | 3                  |

| 7 Procedures                                           | 3                  |

| 7.1 Scope of analysis                                  | 3                  |

| 7.2 System familiarization                             | 3                  |

| 7.3 Top event identification                           | 4                  |

| 7.4 Fault tree construction                            | 4                  |

| 7.5 Fault tree evaluation                              | 6                  |

| 8 Identification and labelling                         | 8                  |

| 9 Report                                               | 8                  |

| Annex A (normative) Symbols                            | 10                 |

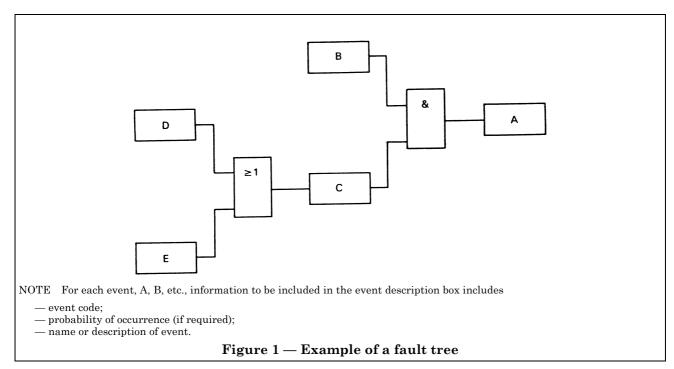

| Figure 1 — Example of a fault tree                     | 4                  |

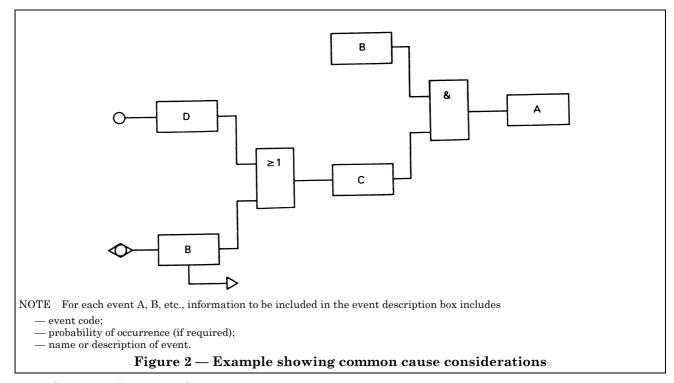

| Figure 2 — Example showing common cause considerations | 5                  |

| Publication(s) referred to                             | Inside back cover  |

### National foreword

This Part of BS 5760 has been prepared under the direction of the Quality, Management and Statistics Standards Policy Committee. It is identical with IEC 1025:1990, "Fault tree analysis (FTA)", published by the International Electrotechnical Commission (IEC).

Eight Parts of this standard have been published and these may be summarized as follows:

Part 0. Introductory guide to reliability. This Part provides guidance to directors of companies who need to know why reliability is important to them, to engineers not trained in quality and reliability to show how reliability should influence their technical decision making, and to middle management not specialized in engineering, to explain how measures to achieve reliability should be integrated with other aspects of project management to give optimum results.

Part 1. Guide to reliability and maintainability programme management. This Part discusses the essential features of a comprehensive reliability and maintainability programme for the planning, organization, direction and control of resources to produce systems, equipment and components which will be reliable and maintainable. It includes consideration of the specification and assessment of reliability and maintainability and of arrangements for the collection of reliability data.

Part 2. Guide to the assessment of reliability. This Part recommends general procedures for the assessment of reliability of hardware systems and contains guidance for the reliability practitioner on the quantitative and statistical aspects of reliability, such as reliability modelling, the provision of data, and the concepts of redundancy and simulation.

Part 3. Guide to reliability practices: examples. This Part contains authentic practical examples illustrating the principles established in Parts 1 and 2 of BS 5760.

Part 4. Guide to specification clauses relating to the achievement and development of reliability in new and existing items. This Part provides more detailed guidance on the specification of reliability.

Part 5. Guide to failure modes, effects, and criticality analysis (FMEA and FMECA). This Part describes failure modes and effects analysis (FMEA) and failure modes, effects and criticality analysis (FMECA), and gives guidance on the application of these techniques.

Part 6. Guide to programmes for reliability growth. This Part describes procedures to expose and remove weaknesses in hardware and software items in order to achieve acceptable reliability in a product. It explains basic concepts, management and test procedures and describes techniques for analysis and correction of failures.

Part 7. Guide to fault tree analysis. This Part describes fault tree analysis and gives guidance on the application of this technique which may be used to identify factors affecting the reliability, performance and safety characteristics of a system.

Further Parts are envisaged in order to provide guidance on other techniques of reliability management. At present two further Parts are in the process of being drafted, and these are as follows.

<sup>1)</sup>Part 8. Guide to the assessment of reliability of systems containing software. This Part will provide guidance on the assessment of reliability of systems containing software.

Part 9. Guide to reliability block diagrams

ii © BSI 04-2000

<sup>&</sup>lt;sup>1)</sup> Currently published as a Draft for Development, DD 198:1991.

#### **Cross-references**

International Standard Corresponding British Standard IEC 50(191):1990 BS 4778 Quality vocabulary

Section 3.2:1991 Glossary of international terms

(Identical)

IEC 617-12:1983 BS 3939 Guide for graphical symbols for electrical

$power,\,telecommunications~and~electronics~diagrams$

Part 12:1985 Binary logic elements

(Identical)

A British Standard does not purport to include all the necessary provisions of a contract. Users of British Standards are responsible for their correct application.

Compliance with a British Standard does not of itself confer immunity from legal obligations.

#### Summary of pages

This document comprises a front cover, an inside front cover, pages i to iv, pages 1 to 12, an inside back cover and a back cover.

This standard has been updated (see copyright date) and may have had amendments incorporated. This will be indicated in the amendment table on the inside front cover.

#### Introduction

Several analytical methods of dependability analysis are available, of which fault tree analysis (FTA) is one. The purpose of each method and their individual or combined applicability in evaluating the reliability and availability of a given system or component should be examined by the analyst before starting the FTA. Consideration should also be given to the results available from each method, data required to perform the analysis, complexity of analysis, and other factors identified in this standard.

Fault tree analysis is concerned with the identification and analysis of conditions and factors which cause or contribute to the occurrence of a defined undesirable event, usually one which significantly affects system performance, economy, safety or other required characteristics. FTA is often applied to the safety analysis of systems.

#### 1 Scope

This International Standard describes fault tree analysis, and gives guidance on its application, as follows:

- by defining basic principles;

- by providing the steps necessary to perform an analysis;

- by identifying appropriate assumptions, events and failure modes;

- by providing identification rules and symbols.

#### 2 Normative references

The following standards contain provisions which, through reference in this text, constitute provisions of this International Standard. At the time of publication, the editions indicated were valid. All standards are subject to revision, and parties to agreements based on this International Standard are encouraged to investigate the possibility of applying the most recent editions of the standards listed below. Members of IEC and ISO maintain registers of currently valid International Standards.

IEC 50(191):1990, International Electrotechnical Vocabulary (IEV), Chapter 191: Dependability and quality of service.

IEC 617-12:1983, Graphical symbols for diagrams, Part 12: Binary logic elements.

#### 3 Definitions

Terms and definitions are in accordance with International Electrotechnical Vocabulary (IEV), Chapter 191.

#### 4 Symbols

The graphical representation of the fault tree requires that symbols, identifiers and labels be used in a consistent manner. The detailed rules are given in clause 8 and Annex A.

#### 5 General

#### 5.1 Fault tree structure

The fault tree itself is an organized graphical representation of the conditions or other factors causing or contributing to the occurrence of a defined undesirable event, referred to as the "top event". The representation is in a form which can be understood, analyzed and, as necessary, rearranged to facilitate the identification of:

- factors affecting the reliability and performance characteristics of the system, for example component fault modes, operator mistakes, environmental conditions, software faults;

- conflicting requirements or specifications which may affect reliable performance;

- common events affecting more than one functional component, which could cancel the benefits of specific redundancies.

Fault tree analysis is basically a deductive (top-down) method of analysis aimed at pinpointing the causes or combinations of causes that can lead to the defined top event. The analysis is mainly qualitative but, depending on certain conditions, it may also be quantitative (see **7.5.2**).

#### 5.2 Objectives

There are several reasons for performing a fault tree analysis independently of, or in conjunction with, other dependability analyses. These include:

- the identification of the causes or combinations of causes leading to the top event;

- the determination of whether a particular system reliability measure meets a stated requirement;

- the demonstration that assumptions made in other analyses, regarding the independence of systems and non-relevance of failures, are not violated;

- the determination of the factor(s) which most seriously affect a particular reliability measure and the changes required to improve that measure;

- the identification of common events or common cause failures.

#### 5.3 Applications

The fault tree is particularly suited to the analysis of complex systems comprising several functionally related or dependent subsystems with different performance objectives. This is especially true whenever the system design requires the collaboration of many specialized technical design groups. Examples of systems to which fault tree analysis is commonly applied include nuclear power generating stations, aeroplanes, communication systems, chemical and other industrial processes, etc.

#### 6 Principles

#### 6.1 General considerations

The development of the fault tree should start early in the system design stage. The growth of the fault tree should be such that it reflects the progress of the design. Thus an increased understanding of the fault modes will be obtained as the design proceeds. The "analysis concurrent with design" allows for early systems design change as significant fault modes are identified. Many final fault trees will be large, in which case a computer may be needed to handle them. Software is available to facilitate analysis. It is important to note that fault tree events are not confined solely to software or hardware faults, but include all conditions or other factors which are relevant to the top event for the system concerned.

In order to use the fault tree technique effectively as a method for system analysis, the procedure shall consist of at least the following steps:

- definition of the scope of the analysis;

- familiarization with the design, functions, and operation of the system;

- definition of the top event;

- construction of the fault tree;

- analysis of the fault tree logic;

- reporting on results of the analysis.

If a numerical analysis is planned, it will be necessary to define a technique for numerical assessment. The selection of the data to be used and numerical evaluation of the reliability measures are additional requirements.

#### 6.2 System structure

Each system should be defined by a description of the system function and by an identification of the system interfaces. Such a definition should include:

- a summary of the design intent;

- the boundaries of the system, such as electrical, mechanical and operational interfaces; such boundaries will be governed by the interaction and interfaces with other systems and should be described by identifying the particular functions, for example power supply, and parts, for example fuse, which form the interfaces;

- the physical structure of the system, as opposed to the functional structure;

- the identification of operational modes together with a description of system operation and the expected or acceptable performance in each operational mode;

- the system's environmental conditions, and relevant human aspects, etc;

— a list of applicable documents, for example drawings, specifications, operating manuals, which give details of the equipment design and operation. Task duration, time interval between (periodic) tests, as well as time available for corrective maintenance actions should be known, as should the support equipment and personnel involved. Specific information on prescribed operating during each operational phase is also required.

In addition to the above, it is recommended to prepare a list of symbols, identification markings, conventions, and formats for data files, when necessary in a machine-readable form to permit the fault tree structure and description to be exchanged between computers.

#### 6.3 Events considered

Events arising from all causes shall be included in the fault tree. Such causes should include the effects of all environmental or other conditions to which the item might be subjected including those which are possible during operation, even if outside the design specification.

Where relevant, fault trees should take into account the effects of mistakes and of deficiencies in computer software including that used for control and status monitoring.

Events which the analyst has considered, but excluded from further analysis as not applicable, should be documented but not included in the final fault tree.

If the fault tree highlights a system performance problem caused by an existing fault, then the event describing that fault should be included in the fault tree. It should be marked as an event which already exists. This should be done in order to consider the effect and order of multiple faults.

#### 6.4 Approaches

Fault tree development starts with the definition of the top event. The top event is the output of the top gate, while the corresponding input events identify possible causes and conditions for the occurrence of the top event. Each input event may itself be an output event of a lower level gate.

If the output event of a gate defines the inability to perform of a function, the corresponding input events could be hardware faults or performance limitations. If the output event defines a hardware fault, the corresponding input events could be hardware faults, lack of control and essential supplies, if applicable and not already included as part of the performance limitations.

The development of a particular fault tree branch terminates after any one or more of the following have been reached:

- basic events; i.e. independent events for which the relevant characteristics can be defined by means other than a fault tree;

- events which need not be developed further, as defined by the analyst;

- events which have been or will be developed further in another fault tree; if an event is developed further such an event must bear the same identification as the corresponding event on the other fault tree so that the latter tree effectively forms a continuation of the former.

#### 7 Procedures

Fault tree analysis proceeds in steps. The specific steps followed for a particular system may not be exactly the same as those followed for another system. However, the following fundamental steps shall be common to all fault tree analyses.

#### 7.1 Scope of analysis

The definition of the scope should include the definition of the system to be analyzed, the purpose and extent of the analysis and the basic assumptions made. These assumptions should include those related to the expected operating and maintenance conditions as well as to system performance under all possible conditions of use.

#### 7.2 System familiarization

In order that a fault tree analysis may be carried out successfully, a detailed knowledge of the system is required. However, some systems may be too complex to be understood fully by one person. In this case, the process of familiarization requires that the necessary specialized knowledge be obtained and incorporated as appropriate into the fault tree analysis. The information necessary is noted in **5.2**.

© BSI 04-2000 3

#### 7.3 Top event identification

The top event is the focus of the entire analysis. Such an event may be the onset or existence of a dangerous condition, or the inability of the system to provide a desired performance.

The top event should be defined in measurable units, whenever possible.

#### 7.4 Fault tree construction

#### 7.4.1 Fault tree format

Fault trees may be drawn either vertically or horizontally. If the vertical arrangement is used, the top event should be at the top of the page and the basic events at the bottom. If the horizontal arrangement is used, the top event may be on the left or right of the page.

Two examples (see Figure 1 and Figure 2) are used to show the development and representation of a fault tree. Symbols used in these examples include:

- event description box;

- fault tree logic symbol (gates);

- gate input connection line;

- transfer-out symbol (common cause);

- transfer-in symbol;

- terminating symbol (for example basic event).

In Figure 1, event A will occur only if both events B and C occur. Event C is present if either event D or E occurs.

If an event represents a common cause, it is shown in the fault tree as a set of events. These events are linked to whatever events they affect. All common events in the set shall have the same event code and be marked by a transfer-in symbol, except the event on the lowest level in the set which is marked by a transfer-out symbol.

If the fault tree is presented in several sections, an event representing a common cause which appears on two or more of the sections shall be treated as follows:

— the event shall be marked with a terminating symbol or, if further developed, with a transfer-out gate symbol on only one of the sections;

— on the section where the terminating or gate symbol is used, the occurrence of the common event on other sections shall be indicated by a transfer-in gate symbol.

An example of a fault tree showing common cause considerations is shown in Figure 2. Event B is a common cause event which is analyzed further on another fault tree. Event D is a basic event.

#### 7.4.2 Construction procedure

Dependability analyses should be documented in such a way that results can be reviewed and any changes needed can be incorporated in order to reflect changes in design, operating procedures or improved understanding of the physics of failure. In order that this may be done, a systematic approach to the construction is required. To implement this systematic approach, two concepts have to be understood and used consistently. These are the concepts of "immediate cause" and of "basic unit".

The "immediate cause" concept requires that the analyst determine the immediate necessary and sufficient causes for the occurrence of the top event. It should be noted that these are not the basic causes of the event but the immediate causes or immediate mechanisms for the event to occur.

The immediate, necessary and sufficient causes of the top event are now treated as sub-top events and the analyst proceeds to determine their immediate, necessary and sufficient causes.

In this way, the analyst proceeds down the tree transferring attention from mechanism to mode, and continually approaching a finer resolution of mechanism and modes, until ultimately the limit of resolution of the tree is reached.

Strict adherence to the concept of "immediate cause" is necessary to ensure that fault modes are not omitted by reason of the assumption that such modes have been included previously.

The concept of "basic units" can be used to save the analyst the effort of developing fault tree diagrams which do not yield new or useful information. A basic unit is treated as if it were a single unit or component or dealt with separately.

In order that the unit be considered "basic", it is necessary and sufficient that the following three requirements be satisfied:

- both the functional and physical boundaries shall be clearly defined;

- operation of the unit shall not depend on any supporting function, or all events related to the unit shall be expressed by a single OR gate having one of the inputs representing a fault of the unit, the remaining inputs representing inability to perform the corresponding support functions;

© BSI 04-2000 5

— no events shall be related to a part within the unit that appears elsewhere in the fault tree.

#### 7.4.3 Fault characteristics

It is necessary for the analyst to consider carefully item faults, particularly in categories such as primary fault and secondary fault resulting from primary and secondary failures.

In determining the classification of a fault, consideration shall be given to the operating and environmental stresses and comparison made with the maximum stresses for which the item has been qualified.

#### 7.5 Fault tree evaluation

The primary purposes of logical (qualitative) and numerical (quantitative) analyses of a system are:

- identification of events which can directly cause a system failure, and the probability of such events;

- assessment of fault tolerance of the system (ability to function even after a specified number of lower level failures or events contributing to the occurrence of a system failure have happened);

- verification of the independence of failure of systems, subsystems or components;

- assessment of data to locate critical components and failure mechanisms;

- identification of device failure diagnostics, inputs to repair and maintenance strategies, etc.

The assessment of fault tolerance of the system includes a determination of the degree of redundancy in the system and a verification that the redundancy is not impaired through common events (common cause events). Although the major part of fault tolerance assessment does not require the use of numerical data, such numerical data are required to evaluate which combinations of events causing a system fault are the most likely to occur.

#### 7.5.1 Logical analysis

Three basic techniques are used for logical analysis: investigation, boolean reduction and determination of minimal cut sets.

#### Investigation

Investigation includes a review of the fault tree structure, identification of common events and a search for independent branches. Investigation provides the analyst with important information which, in some cases, may be sufficient to eliminate the need for further analyses. In all other cases, investigation is necessary for a correct decision on the type and extent of further analyses. Direct visual investigation of a plotted tree is possible only for small trees, not exceeding about 70 events. Investigation of larger trees, as arise from the analysis of actual systems, requires a suitable computer tool, but the overall approach remains the same.

Investigation starts with the review of the fault tree structure. All events which are linked to the top event through a continuous chain of OR gates are events which cause the top event to occur. Therefore, if a fault tree consists only of OR gates, no further analysis is required. If the fault tree includes other gate types, the analyzed system incorporates some sort of redundancy or other fault prevention features which could be invalidated by common cause events. Investigation should identify common cause events, but should not assume that their presence is benign. Such conclusions can be drawn only after a thorough analysis using boolean reduction or determination of minimal cut sets. As the difficulty of the analysis increases rapidly with the size of the fault tree, inspection of the fault tree allows the analyst to identify which branches of the fault tree are independent and can thus be analyzed separately.

#### - Boolean reduction

Boolean reduction is used for the evaluation of the effects of common events (identical events occurring in different branches) in fault trees where the occurrence of the top event does not depend on timing or sequencing of events. Boolean reduction can be carried out by solving boolean equations for the fault tree.

#### - Methods of minimal cut sets

There are several methods of determining minimal cut sets but application to larger trees may be difficult and incomplete. Various computer programs are available to assist the analyst.

A cut set is a group of events which, when occurring together, (may) cause the top event to happen. A minimal cut set is the smallest such group in which all events must occur (in proper sequence) for the top event to occur. If any of the events in a minimal cut set does not occur, it prevents the top event from occurring. The words in parentheses in the definition above extend the definition of minimal cut sets to fault trees dependent on sequencing of events. In those instances, the minimal cut set determines the group of events with the potential to cause the top event. The effects of sequencing of events in this group can be analyzed using the state-transition diagram, which, however, is beyond the scope of this standard.

#### 7.5.2 Numerical analysis

The purpose of numerical analysis is to provide a quantitative assessment of the probability of occurrence of the top event or a selected set of events. Numerical analysis is also used to support and to supplement the logical analysis. In order to perform a numerical evaluation of a fault tree, probabilistic data at the component level are required. Reliability and availability prediction techniques, actual test or field use data may be used to establish the quantitative values.

#### 7.5.3 Examples of a simple evaluation using boolean algebra applied to fault tree analysis

— Application to fault tree analysis

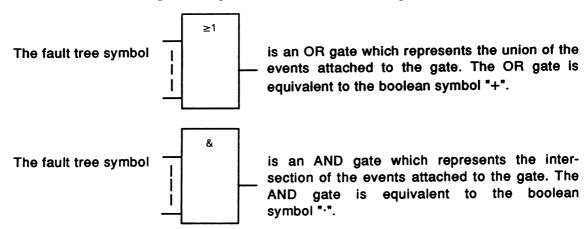

In fault trees which consist only of AND, OR and NOT gates, there is a one-to-one correspondence between the boolean algebraic expression and the fault tree representation.

OR and AND symbols for boolean algebra may be expressed with other symbology, such as that used with many computer program languages. Consistency is required, however.

Considering the fault tree as shown in Figure 1, we can write

$$C = D + E$$

$$A = B \cdot C = B \cdot (D + E)$$

Applying the distributive law, we have

$$A = B \cdot D + B \cdot E$$

— Application to minimal cut sets

The expression for the top event can be written in terms of a finite number of minimal cut sets, which are unique to that top event.

The general form is

$$T = M_1 + M_2 + \dots + M_i + \dots + M_P$$

where T is the top event and M<sub>i</sub> are the minimal cut sets. Each minimal cut set consists of a combination of specific component faults, and the general minimal cut set can be expressed as

$$\mathbf{M} = \mathbf{X}_1 \cdot \mathbf{X}_2 \cdot \dots \cdot \mathbf{X}_i \cdot \dots \cdot \mathbf{X}_c$$

where  $X_i$  is a basic event on the tree.

Consider the fault tree shown in Figure 1. The minimal cut sets of the top event are in this case  $B \cdot D$  and  $B \cdot E$ .

© BSI 04-2000 7

#### 8 Identification and labelling

Each event in the fault tree shall be uniquely identified. Events should be labelled so that cross reference from the fault tree to the corresponding design documentation can easily be made.

The top event of the fault tree is the undesirable event which is the primary reason for undertaking the fault tree analysis. It should be noted that only a single top event may be associated with a given fault tree.

If several events in a fault tree all refer to different fault modes of the same item, then such events shall be labelled so as to enable them to be distinguished. At the same time it should be clear that they are a group of events related to the same item.

If a particular event, for example inability of a particular valve to close, occurs in several places in a tree, or if it occurs in several trees, all such occurrences shall bear the same label. However, events which are similar but which involve different items shall not bear the same identification.

A typical event code should contain information relating to system identification, component identification and fault mode.

The fault tree is in effect a diagram in which the events are linked by logic gates. Each gate has one output event but one or more input events.

The input events identify possible causes and conditions for the occurrence of the output events. However, such linking does not necessarily define the sequential (time) relationship between the events.

The basic fault tree uses AND, OR and NOT gates. However, for complex systems analysis, additional gate symbols may be required to assure that the fault trees are readable and as simple as possible. Annex A shows the standardized basic symbols in accordance with IEC 617-12, together with possible alternatives. A supplementary set of more specialized symbols may be developed if required. However, it is important for the analyst to define and report those symbols being used and ensure uniform and consistent use throughout a given fault tree analysis. This is particularly true if computer-aided techniques are to be used (see end of **6.2**).

In developing the fault tree, the analyst should also use appropriate symbology and identification to make it clear, when applicable, that

- the event or whole branch is also used elsewhere in the tree;

- the depicted part of the tree includes events used also in another part of the tree;

- a common cause event shown in one part of the analysis is further developed elsewhere.

This is necessary for the graphical presentation of fault trees.

#### 9 Report

The report of the fault tree analysis should include as a minimum the basic items listed below. Additional and supplementary information may be provided to increase clarity, especially in cases of complex systems analyses. A prescribed format is not proposed by this standard.

Basic items in the report should be

- objective and scope;

- system description

- a) design description

- b) system operation

- c) detailed system boundaries definitions;

- assumptions

- a) system design assumptions

- b) operation, maintenance, test and inspection assumptions

- c) reliability and availability modelling assumptions;

- system fault definition and criteria;

- fault tree analysis

- a) analysis

- b) data

- c) symbols used;

— results and conclusions.

Supplementary data items which may be included are

- system block or circuit diagrams;

- summary of reliability and maintainability data and sources used;

- fault tree description in computer readable form (for complex systems analyses).

# Annex A (normative) Symbols

Annex A forms an integral part of this International Standard.

| Preferred symbol Alternative symbol |              | Function               | Description                                                                                                                                                                                                                                      |  |

|-------------------------------------|--------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| - &                                 |              | AND gate               | Event occurs only if all input events occur simultaneously                                                                                                                                                                                       |  |

|                                     | <del>-</del> | OR gate                | Event occurs if any of the input events occur, either alone or in any combination                                                                                                                                                                |  |

| =1                                  | <del></del>  | Exclusive-OR gate      | Event occurs only if one of the input events occurs alone (used typically with two input events)                                                                                                                                                 |  |

|                                     |              | NOT gate               | Event represents a condition which is<br>an inverse of the condition defined by<br>the input event                                                                                                                                               |  |

| <del></del>                         |              | INHIBIT gate           | Event occurs only if input event attached to the right occurs while the event attached to the bottom and forming the condition is in force; if the condition is caused by the occurrence of another event, INHIBIT gate implies timing of events |  |

|                                     | m/n          | Redundant<br>structure | Event occurs if at least m of the (n) input events occur                                                                                                                                                                                         |  |

| Preferred symbol | Alternative symbol | Function                      | Description                                                                                                                   |

|------------------|--------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                  |                    | Gate (general)                | General symbol of gate; its function shall be defined within the symbol                                                       |

|                  |                    | Event<br>description<br>block | Name or description of the event, event code, and probability of occurrence (as required) shall be included within the symbol |

| —                |                    | Basic event                   | Event which cannot be subdivided                                                                                              |

|                  |                    | Undeveloped<br>event          | Event for which further subdivision<br>was not done (usually because it was<br>considered unnecessary)                        |

| $\rightarrow$    |                    | Analyzed elsewhere            | Event which is further developed on another fault tree                                                                        |

|                  |                    | House                         | Event which has happened, or will happen with certainty                                                                       |

|                  |                    | Zero event                    | Event which cannot happen                                                                                                     |

| <b>─</b>         |                    | Transfer-in                   | Event defined elsewhere in the fault tree                                                                                     |

| <del></del>      |                    | Transfer-out                  | Replicated event — used elsewhere                                                                                             |

## Publication(s) referred to

See national foreword.

BS 5760-7: 1991 IEC 1025:1990

## **BSI** — British Standards Institution

BSI is the independent national body responsible for preparing British Standards. It presents the UK view on standards in Europe and at the international level. It is incorporated by Royal Charter.

#### Revisions

British Standards are updated by amendment or revision. Users of British Standards should make sure that they possess the latest amendments or editions.

It is the constant aim of BSI to improve the quality of our products and services. We would be grateful if anyone finding an inaccuracy or ambiguity while using this British Standard would inform the Secretary of the technical committee responsible, the identity of which can be found on the inside front cover. Tel: 020 8996 9000. Fax: 020 8996 7400.

BSI offers members an individual updating service called PLUS which ensures that subscribers automatically receive the latest editions of standards.

#### **Buying standards**

Orders for all BSI, international and foreign standards publications should be addressed to Customer Services. Tel: 020 8996 9001. Fax: 020 8996 7001.

In response to orders for international standards, it is BSI policy to supply the BSI implementation of those that have been published as British Standards, unless otherwise requested.

#### Information on standards

BSI provides a wide range of information on national, European and international standards through its Library and its Technical Help to Exporters Service. Various BSI electronic information services are also available which give details on all its products and services. Contact the Information Centre. Tel: 020 8996 7111. Fax: 020 8996 7048.

Subscribing members of BSI are kept up to date with standards developments and receive substantial discounts on the purchase price of standards. For details of these and other benefits contact Membership Administration. Tel: 020 8996 7002. Fax: 020 8996 7001.

#### Copyright

Copyright subsists in all BSI publications. BSI also holds the copyright, in the UK, of the publications of the international standardization bodies. Except as permitted under the Copyright, Designs and Patents Act 1988 no extract may be reproduced, stored in a retrieval system or transmitted in any form or by any means – electronic, photocopying, recording or otherwise – without prior written permission from BSI.

This does not preclude the free use, in the course of implementing the standard, of necessary details such as symbols, and size, type or grade designations. If these details are to be used for any other purpose than implementation then the prior written permission of BSI must be obtained.

If permission is granted, the terms may include royalty payments or a licensing agreement. Details and advice can be obtained from the Copyright Manager. Tel: 020 8996 7070.

BSI 389 Chiswick High Road London W4 4AL