# Semiconductor devices — Discrete devices —

Part 9: Insulated-gate bipolar transistors (IGBTs)

ICS 31.080.30

## **National foreword**

This British Standard is the UK implementation of IEC 60747-9:2007. It supersedes BS IEC 60747-9:1998 which is withdrawn.

The UK participation in its preparation was entrusted to Technical Committee EPL/47, Semiconductors.

A list of organizations represented on this committee can be obtained on request to its secretary.

This publication does not purport to include all the necessary provisions of a contract. Users are responsible for its correct application.

Compliance with a British Standard cannot confer immunity from legal obligations.

This British Standard was published under the authority of the Standards Policy and Strategy Committee on 30 November 2007

© BSI 2007

Amendments issued since publication

| Amd. No. | Date | Comments |

|----------|------|----------|

|          |      |          |

|          |      |          |

|          |      |          |

|          |      |          |

ISBN 978 0 580 54381 4

## IEC 60747-9

Edition 2.0 2007-09

# INTERNATIONAL STANDARD

Semiconductor devices – Discrete devices – Part 9: Insulated-gate bipolar transistors (IGBTs)

## CONTENTS

| 1    | Scop   | )e                                                                                                                                                                 | 5  |  |

|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| 2    | Norn   | ive references5                                                                                                                                                    |    |  |

| 3    | Term   | Terms and definitions                                                                                                                                              |    |  |

|      | 3.1    | Graphical symbol of IGBT                                                                                                                                           | 5  |  |

|      | 3.2    | General terms                                                                                                                                                      | 6  |  |

|      | 3.3    | Terms related to ratings and characteristics; voltages and currents                                                                                                | 6  |  |

|      | 3.4    | Terms related to ratings and characteristics; other characteristics                                                                                                | 8  |  |

| 4    | Lette  | er symbols                                                                                                                                                         | 10 |  |

|      | 4.1    | General                                                                                                                                                            | 10 |  |

|      | 4.2    | Additional general subscripts                                                                                                                                      | 10 |  |

|      | 4.3    | List of letter symbols                                                                                                                                             |    |  |

| 5    | Esse   | ential ratings and characteristics                                                                                                                                 | 12 |  |

|      | 5.1    | Ratings (limiting values)                                                                                                                                          |    |  |

|      | 5.2    | Characteristics                                                                                                                                                    |    |  |

| 6    | Mea    | suring methods                                                                                                                                                     |    |  |

|      | 6.1    | General                                                                                                                                                            |    |  |

|      | 6.2    | Verification of ratings (limiting values)                                                                                                                          |    |  |

| _    | 6.3    | Methods of measurement                                                                                                                                             |    |  |

| 7    |        | ptance and reliability                                                                                                                                             |    |  |

|      | 7.1    | General requirements                                                                                                                                               |    |  |

|      | 7.2    | Specific requirements                                                                                                                                              |    |  |

|      | 7.3    | Type tests and routine tests                                                                                                                                       | 46 |  |

| Anı  | nex A  | (normative) Measuring method for collector-emitter breakdown voltage                                                                                               | 48 |  |

|      |        | (normative) Measuring method for inductive load turn-off current under                                                                                             |    |  |

|      |        | conditions                                                                                                                                                         | 50 |  |

| Anı  | nex C  | (normative) Forward biased safe operating area (FBSOA)                                                                                                             | 52 |  |

|      |        | (normative) Case non-rupture                                                                                                                                       |    |  |

|      |        | (·············)                                                                                                                                                    |    |  |

| Rih  | liogra | phy                                                                                                                                                                | 57 |  |

| ٥.۵  | nogra  | F''J                                                                                                                                                               |    |  |

| Fia  | ure 1  | <ul> <li>Circuit for measuring the collector-emitter voltages VCES, VCER, VCEX</li> </ul>                                                                          | 16 |  |

|      |        | - Circuit for testing the gate-emitter voltage ±VGFS                                                                                                               |    |  |

| _    |        | 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3 3                                                                                                                            |    |  |

|      |        | - Circuit for measuring collector current                                                                                                                          |    |  |

|      |        | Circuit for measuring peak collector current                                                                                                                       |    |  |

|      |        | - Test circuit of reverse safe operating area (RBSOA)                                                                                                              | 20 |  |

|      |        | <ul> <li>Waveforms of gate-emitter voltage V<sub>GE</sub> and collector current I<sub>C</sub> during</li> </ul>                                                    | 20 |  |

|      |        |                                                                                                                                                                    |    |  |

| _    |        | - Circuit for testing safe operating pulse width at load short circuit (SCSOA1)                                                                                    | ∠1 |  |

|      |        | <ul> <li>Waveforms of gate-emitter voltage V<sub>GE</sub>, collector current I<sub>C</sub> and voltage</li> <li>Ing load short-circuit condition SCSOA1</li> </ul> | 22 |  |

| _    | _      | Short-circuit safe operating area 2 (SCSOA2)                                                                                                                       |    |  |

| , 19 | 4100   | chort or our out of operating area 2 (0000A2)                                                                                                                      | 20 |  |

| Figure 10 – Waveforms during SCSOA2                                                                                                                                                                                        | 23 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 11 – Circuit for measuring the collector-emitter sustaining voltage $V_{\text{CE*sus}}$                                                                                                                             | 24 |

| Figure 12 – Operating locus of the collector current                                                                                                                                                                       | 25 |

| Figure 13 – Circuit for measuring the collector-emitter saturation voltage VCEsat                                                                                                                                          | 26 |

| Figure 14 – Basic circuit for measuring the gate-emitter threshold voltage                                                                                                                                                 | 27 |

| Figure 15 – Circuit for measuring the collector cut-off current                                                                                                                                                            | 28 |

| Figure 16 – Circuit for measuring the gate leakage current                                                                                                                                                                 | 29 |

| Figure 17 – Circuit for measuring the input capacitance                                                                                                                                                                    | 30 |

| Figure 18 – Circuit for measuring the output capacitance                                                                                                                                                                   | 31 |

| Figure 19 – Circuit for measuring the reverse transfer capacitance                                                                                                                                                         | 32 |

| Figure 20 – Circuit for measuring the gate charge                                                                                                                                                                          | 33 |

| Figure 21 – Basic gate charge waveform                                                                                                                                                                                     | 33 |

| Figure 22 – Circuit for measuring the short-circuit internal gate resistance                                                                                                                                               | 34 |

| Figure 23 – Circuit for measuring turn-on times and energy                                                                                                                                                                 | 35 |

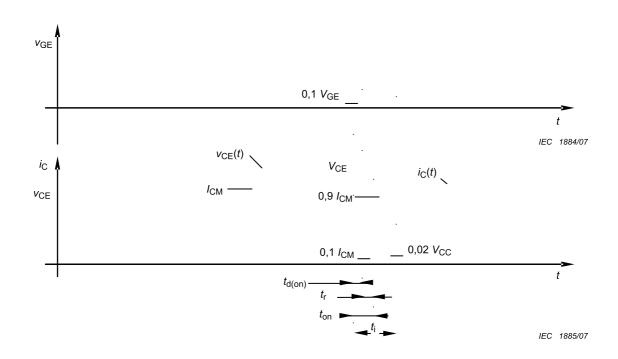

| Figure 24 – Waveforms during turn-on times                                                                                                                                                                                 | 36 |

| Figure 25 – Circuit for measuring turn-off times and energy                                                                                                                                                                | 37 |

| Figure 26 – Waveforms during turn-off times                                                                                                                                                                                | 37 |

| Figure 27 – Circuit for measuring the variation with temperature of the collector-emitter voltage $V_{\text{CE}}$ at a low measuring current $I_{\text{C1}}$ and for heating up the IGBT by a high current $I_{\text{C2}}$ | 39 |

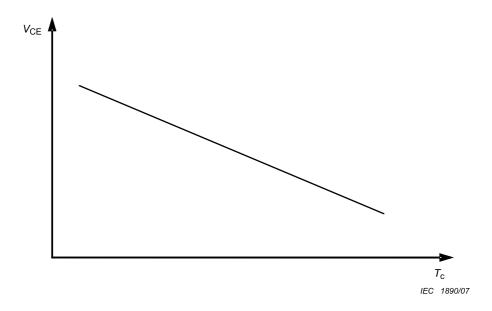

| Figure 28 – Typical variation of the collector-emitter voltage $V_{CE}$ at a low measuring current $I_{C1}$ with the case temperature $T_{C}$ (when heated from outside, i.e. $T_{C} = T_{Vj}$ )                           | 40 |

| Figure 29 – Circuit for measuring thermal resistance and transient thermal impedance: method 2                                                                                                                             | 41 |

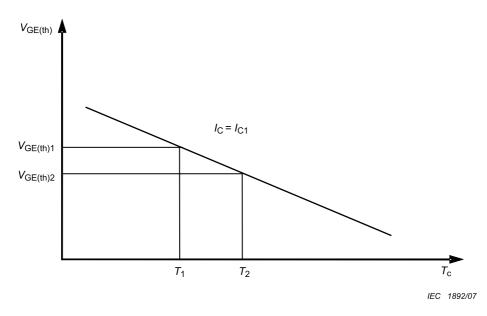

| Figure 30 – Typical variation of the gate-emitter threshold voltage $V_{GE(th)}$ at a low measuring current $I_{C2}$ with the case temperature $T_{C}$ (when heated from the outside, i.e. $T_{C} = T_{Vi}$ )              | 42 |

| Figure 31 – $I_C$ , $V_{GE}$ and $T_C$ with time                                                                                                                                                                           |    |

| Figure 32 – Circuit for high-temperature blockings                                                                                                                                                                         | 44 |

| Figure 33 – Circuit for high-temperature gate bias                                                                                                                                                                         |    |

| Figure 34 – Circuit for intermittent operating life                                                                                                                                                                        | 45 |

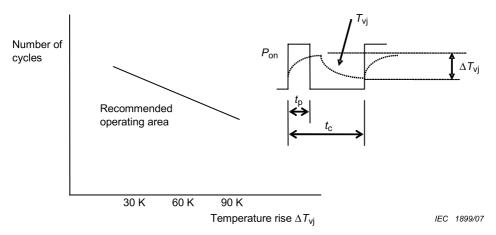

| Figure 35 – Expected number of cycles versus temperature rise $\Delta T_{vj}$                                                                                                                                              | 46 |

| Figure A.1 – Circuit for testing the collector-emitter breakdown voltage                                                                                                                                                   |    |

| Figure B.1 – Measuring circuit for inductive load turn-off current                                                                                                                                                         | 50 |

| Figure B.2 – Waveforms of collector current IC and collector voltage VCE during turn-off.                                                                                                                                  | 50 |

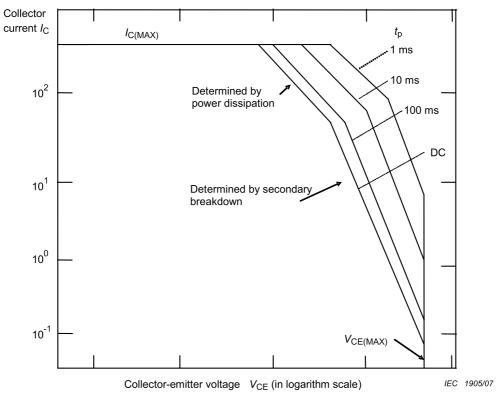

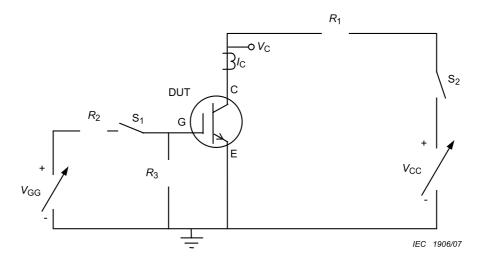

| Figure C.1 – Test circuit of forward biased safe operating area (method 1)                                                                                                                                                 | 52 |

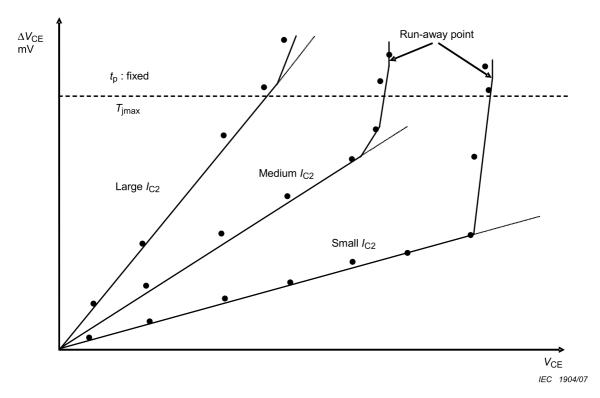

| Figure C.2 – Typical $\Delta V_{CE}$ versus collector-emitter voltage $V_{CE}$ characteristics                                                                                                                             | 53 |

| Figure C.3 – Typical forward biased safe operating area                                                                                                                                                                    |    |

| Figure C.4 – Circuit testing forward biased safe operating area (method 2)                                                                                                                                                 | 54 |

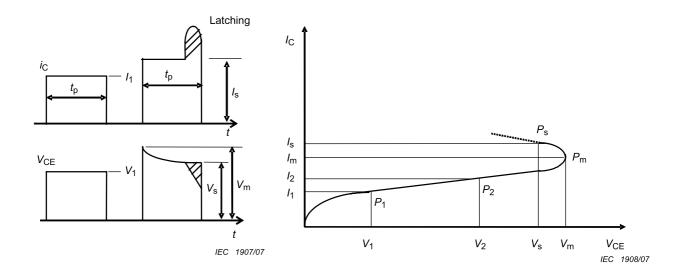

| Figure C.5 – Latching mode operation waveforms                                                                                                                                                                             | 55 |

| Figure C.6 – Latching mode I-V characteristic                                                                                                                                                                              | 55 |

| Table 1 – Acceptance-defining characteristics                                     | 15 |

|-----------------------------------------------------------------------------------|----|

| Table 2 – Acceptance-defining characteristics for endurance and reliability tests | 44 |

| Table 3 – Minimum type and routine tests for IGBTs when applicable                | 47 |

## SEMICONDUCTOR DEVICES – DISCRETE DEVICES –

## Part 9: Insulated-gate bipolar transistors (IGBTs)

## 1 Scope

This part of IEC 60747 gives product specific standards for terminology, letter symbols, essential ratings and characteristics, verification of ratings and methods of measurement for insulated-gate bipolar transistors (IGBTs).

## 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60747-1:2006, Semiconductor devices - Part 1: General

IEC 60747-2, Semiconductor devices – Discrete devices and integrated circuits – Part 2: Rectifier diodes

IEC 60747-6, Semiconductor devices - Part 6: Thyristors

IEC 61340 (all parts), Electrostatics

## 3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

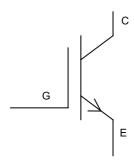

#### 3.1 Graphical symbol of IGBT

The graphical symbol as shown below is used in this edition of IEC 60747-9.

Graphical symbol

NOTE Only the graphical symbol for N-channel IGBT is used in this standard. It equally applies for the measurement of P-channel devices. In the case of P-channel devices polarity must be adapted.

#### 3.2 General terms

#### 3.2.1

## insulated-gate bipolar transistor

#### **IGBT**

transistor having a conduction channel and a PN junction. The current flowing through the channel and the junction is controlled by an electric field resulting from a voltage applied between the gate and emitter terminals See IEV 521-04-05.

NOTE With collector-emitter voltage applied, the PN junction is forward biased.

#### 322

#### **N-channel IGBT**

IGBT that has one or more N-type conduction channels See IEV 521-05-06.

#### 3.2.3

#### P-channel IGBT

IGBT that has one or more P-type conduction channels See IEV 521-04-05.

#### 3.2.4

## collector current (of an IGBT)

$I_{c}$

direct current that is switched (controlled) by the IGBT

#### 3.2.5

## collector terminal, collector (of an IGBT)

C

for an N-channel (a P-channel) IGBT, the terminal to (from) which the collector current flows from (to) the external circuit

See IEV 521-07-05 and IEV 521-05-02.

#### 3.2.6

## emitter terminal, emitter (of an IGBT)

Ε

for an N-channel (a P-channel) IGBT, the terminal from (to) which the collector current flows to (from) the external circuit

See IEV 521-07-04.

#### 3.2.7

## gate terminal, gate (of an IGBT)

G

terminal to which a voltage is applied against the emitter terminal in order to control the collector current

See IEV 521-07-09.

## 3.3 Terms related to ratings and characteristics; voltages and currents

#### 3.3.1

#### collector-emitter (d.c.) voltage

voltage between collector and emitter

#### 3.3.2

## collector-emitter voltage with gate-emitter short-circuited

#### Vces

collector-emitter voltage at which the collector current has a specified low (absolute) value with gate-emitter short-circuited

#### 3.3.3

#### collector-emitter sustaining voltage

#### $V_{CF*sus}$

collector-emitter breakdown voltage at relatively high values of collector current where the breakdown voltage is relatively insensitive to changes in collector current, for a specified termination between gate and emitter terminals

NOTE 1 The specified termination between gate and emitter terminals is indicated in the letter symbol by the third subscript '\*'; see 4.1.2 of IEC 60747-7.

NOTE 2 When necessary, a suitable qualifier is added to the basic term to indicate a specific termination between gate and emitter terminals.

Example: Collector-emitter sustaining voltage with gate and emitter terminals short-circuited  $V_{\rm CESsus}$ .

NOTE 3 The basic term may be shortened if the meaning is clear from the letter symbol used.

Example: Collector-emitter sustaining voltage  $V_{CFRsus}$ .

NOTE 4 This term is important for high-voltage devices, for example more than 4 kV.

#### 3.3.4

#### collector-emitter breakdown voltage

#### $V_{(BR)CES}$

voltage between collector and emitter above which the collector current rises steeply, with gate to emitter short-circuited See IEV 521-05-06.

#### 3.3.5

#### collector-emitter saturation voltage

#### $V_{CFsat}$

collector-emitter voltage under conditions of gate-emitter voltage at which the collector current is essentially independent of the gate-emitter voltage

#### 3.3.6

## gate-emitter (d.c.) voltage

voltage between gate and emitter

#### 3.3.7

## gate-collector (d.c.) voltage

voltage between gate and collector

#### 3.3.8

#### gate-emitter threshold voltage

#### V<sub>GE(th</sub>

gate-emitter voltage at which the collector current has a specified low (absolute) value

#### 3.3.9

## electrostatic discharge voltage

voltage that can be applied to the gate terminal without destruction of the isolation layer See IEV 521-05-27

#### 3.3.10

#### collector cut-off current

collector current at a specific collector-emitter voltage below the breakdown region and gate off-state

#### 3.3.11

## collector current

current through collector

#### 3.3.12

#### tail current

#### $I_{CZ}$

collector current during the tail time

#### 3.3.13

#### gate leakage current

#### IGES

leakage current into the gate terminal at a specified gate-emitter voltage with the collector terminal short-circuited to the emitter terminal

#### 3.3.14

#### safe operating area

#### SOA

collector current versus collector emitter voltage where the IGBT is able to turn-on and turn-off without failure

#### 3.3.14.1

#### forward bias safe operating area

#### **FBSOA**

collector current versus collector emitter voltage where the IGBT is able to turn-on and is able to be on-state without failure

#### 3.3.14.2

#### reverse bias safe operating area

#### **RBSOA**

collector current versus collector emitter voltage where the IGBT is able to turn-off without failure

#### 3.3.14.3

## short circuit safe operating area

#### SCSOA

short circuit duration and collector emitter voltage where the IGBT is able to turn-on and turn-off without failure

#### 3.4 Terms related to ratings and characteristics; other characteristics

## 3.4.1

## input capacitance

#### $C_{\text{ies}}$

capacitance between the gate and emitter terminals with the collector terminal short-circuited to the emitter terminal for a.c.

#### 3.4.2

## output capacitance

#### Coes

capacitance between the collector and emitter terminals with the gate terminal short-circuited to the emitter terminal for a.c.

## 3.4.3

## reverse transfer capacitance

#### $C_{res}$

capacitance between the collector and gate terminals

#### 3.4.4

## gate charge

#### $Q_{\mathsf{G}}$

charge required to raise the gate-emitter voltage from a specified low to a specified high level

#### 3.4.5

#### internal gate resistance

$r_{q}$

internal series resistance

#### 3.4.6

## turn-on energy (per pulse)

#### $E_{or}$

energy dissipated inside the IGBT during the turn-on of a single collector current pulse

NOTE The corresponding turn-on power dissipation under periodic pulse conditions is obtained by multiplying  $E_{on}$  by the pulse frequency.

#### 3.4.7

## turn-off energy (per pulse)

#### East

energy dissipated inside the IGBT during the turn-off time plus the tail time of a single collector current pulse

NOTE The corresponding turn-off power dissipation under periodic pulse conditions is obtained by multiplying  $E_{\rm off}$  by the pulse frequency.

#### 3.4.8

## turn-on delay time

#### $t_{d(on)}, t_{d}$

time interval between the beginning of a voltage pulse across the input terminals which switches the IGBT from the off-state to the on-state and the beginning of the rise of the collector current

NOTE Usually, the time is measured between points corresponding to 10 % of the input and output pulse amplitudes.

#### 3.4.9

#### rise time

t,

time interval between the instants at which the rise of the collector current reaches specified lower and upper limits, respectively, when the IGBT is being switched from the off-state to the on-state

NOTE  $\,$  Usually the lower and upper limits are 10 % and 90 % of the pulse amplitude.

#### 3.4.10

#### turn-on time

#### $t_{on}$

sum of the turn-on delay time and the rise time

#### 3.4.11

#### turn-off delay time

#### $t_{d(off)}, t_{s}$

time interval between the end of the voltage pulse across the input terminals which has held the IGBT in its on-state and the beginning of the fall of the collector current when the IGBT is switched from the on-state to the off-state

NOTE Usually, the time is measured between points corresponding to  $90\,\%$  of the input and output pulse amplitudes.

#### 3.4.12

#### fall time

te

time interval between the instants at which the fall of the collector current reaches specified upper and lower limits, respectively, when the IGBT is switched from the on-state to the off-state

NOTE Usually, the upper and lower limits are 90 % and 10 % of the pulse amplitude.

#### 3.4.13

## turn-off time

#### $t_{\rm off}$

sum of the turn-off delay time and the fall time

#### 3.4.14

#### tail time

$t_z$

time interval from the end of the turn-off time to the instant at which the collector current has fallen to 2 % or lower specified value

## 4 Letter symbols

## 4.1 General

General letter symbols for IGBTs are defined in Clause 4 of IEC 60747-1.

## 4.2 Additional general subscripts

C,c collector

E,e emitter

G,g gate

sat saturation

th threshold

Z,z tail

S termination with a short circuit

R termination with a resistor

X termination with specified gate emitter voltage

sus sustaining

## 4.3 List of letter symbols

| Name and designation                                              | Letter symbol          |  |  |  |

|-------------------------------------------------------------------|------------------------|--|--|--|

| 4.3.1 Voltages                                                    |                        |  |  |  |

| Collector-emitter voltage                                         | V <sub>CE</sub>        |  |  |  |

| Collector-emitter voltage, gate-emitter short-circuited           | V <sub>CES</sub>       |  |  |  |

| Collector-emitter sustaining voltage                              | V <sub>CE*sus</sub>    |  |  |  |

| Collector-emitter breakdown voltage, gate-emitter short-circuited | V <sub>(BR)CES</sub>   |  |  |  |

| Collector-emitter saturation voltage                              | V <sub>CEsat</sub>     |  |  |  |

| Gate-emitter voltage                                              | $V_{GE}$               |  |  |  |

| Gate-emitter voltage, collector-emitter short-circuited           | $V_{GES}$              |  |  |  |

| Gate-emitter threshold voltage                                    | $V_{\rm GE(th)}$       |  |  |  |

| Collector-gate voltage, gate-emitter resistance specified         | $V_{\text{CGR}}$       |  |  |  |

| 4.3.2 Currents                                                    |                        |  |  |  |

| Collector current                                                 | I <sub>C</sub>         |  |  |  |

| Peak collector current                                            | I <sub>CM</sub>        |  |  |  |

| Repetitive peak collector current                                 | I <sub>CRM</sub>       |  |  |  |

| Collector-emitter cut-off current, gate-emitter short-circuited   | I <sub>CES</sub>       |  |  |  |

| Tail current                                                      | I <sub>CZ</sub>        |  |  |  |

| Gate current                                                      | $I_{G}$                |  |  |  |

| Gate leakage current, collector-emitter short-circuited           | I <sub>GES</sub>       |  |  |  |

| 4.3.3 Other electrical magnitudes                                 |                        |  |  |  |

| Input capacitance                                                 | C <sub>ies</sub>       |  |  |  |

| Output capacitance                                                | C <sub>oes</sub>       |  |  |  |

| Reverse transfer capacitance                                      | C <sub>res</sub>       |  |  |  |

| Gate charge                                                       | $Q_{G}$                |  |  |  |

| Internal gate resistance                                          | $r_{ m g}$             |  |  |  |

| Turn-on power dissipation                                         | Pon                    |  |  |  |

| Turn-on energy                                                    | E <sub>on</sub>        |  |  |  |

| Turn-off power dissipation                                        | P <sub>off</sub>       |  |  |  |

| Turn-off energy                                                   | E <sub>off</sub>       |  |  |  |

| Conducting state power dissipation                                | P <sub>cond</sub>      |  |  |  |

| Conducting state energy                                           | E <sub>cond</sub>      |  |  |  |

| Total power dissipation                                           | P <sub>tot</sub>       |  |  |  |

| 4.3.4 Time                                                        |                        |  |  |  |

| Tail time                                                         | tz                     |  |  |  |

| 4.3.5 Thermal magnitudes                                          |                        |  |  |  |

| Thermal resistance junction to heatsink                           | $R_{th(j-c)}$          |  |  |  |

| Transient thermal impedance junction to heatsink                  | $Z_{\mathrm{th(j-c)}}$ |  |  |  |

## 5 Essential ratings and characteristics

## 5.1 Ratings (limiting values)

Ratings shall be valid for the whole range of operating conditions as stated for the particular device, with reference to a curve where appropriate.

## 5.1.1 Ambient or case or virtual junction operating temperature ( $T_a$ or $T_c$ or $T_{vi}$ )

Maximum and minimum values.

## 5.1.2 Storage temperature $(T_{stg})$

Maximum and minimum values.

## 5.1.3 Collector-emitter voltage with gate-emitter short-circuited ( $V_{CES}$ )

Maximum value.

NOTE This rating should not be less than  $V_{(BR)CES}$ . (See 5.2.1.)

## 5.1.4 Gate-emitter voltages with collector emitter short circuit ( $V_{GES}$ )

Maximum positive and negative values.

## 5.1.5 Continuous collector current $(I_C)$

Maximum value.

## 5.1.6 Repetitive peak collector current (I<sub>CRM</sub>)

Maximum value for rectangular pulses with specified pulse duration and duty cycle.

## 5.1.7 Non-repetitive peak collector current (I<sub>CSM</sub>)

Maximum value for a rectangular pulse with specified pulse duration.

## 5.1.8 Total power dissipation ( $P_{tot}$ )

Maximum value with a derating curve where appropriate.

#### 5.1.9 Maximum safe operating area

Diagram showing the maximum rated collector current  $I_{\rm c}$  after turn-on, which may not be exceeded, even under best cooling conditions, as a function of the collector-emitter voltage  $V_{\rm CE}$  before and during turn-on for direct current and various pulse durations at 25 °C case temperature.

## 5.1.10 Maximum reverse biased safe operating area (RBSOA)

Diagram showing the area of collector current  $I_{\rm C}$  and collector-emitter voltage  $V_{\rm CE}$  which the IGBTs will sustain simultaneously for a short period of time during turn-off without failure under the specified conditions.

## 5.1.11 Maximum short circuit safe operating area (SCSOA)

SCSOA is given by a pair of values of short-circuit duration  $t_{\rm psc}$  and collector-emitter voltage  $V_{\rm CE}$  which may not be exceeded under the load short-circuit conditions. The device may be turned on and turned off again for shorting a voltage source without failure.

## 5.1.12 Maximum terminal current ( $I_{tRMS}$ ) (where appropriate)

Maximum r.m.s. value of the current through the main terminal.

## 5.1.13 Mounting force (F)

Maximum and minimum values, where appropriate.

## 5.1.14 Mounting torque (M)

Maximum and minimum values, where appropriate.

## 5.2 Characteristics

Characteristics shall be given at  $T_{vj}$  = 25 °C except where otherwise stated; and at one other specified temperature.

## 5.2.1 Collector-emitter breakdown voltage ( $V_{(BR)CES}$ )

Minimum value with gate-emitter short-circuited and at specified collector current.

## 5.2.2 Collector-emitter sustaining voltage ( $V_{CE*sus}$ )

Where appropriate, minimum value at specified collector current and gate conditions.

#### 5.2.3 Collector-emitter saturation voltage ( $V_{CFsat}$ )

Maximum value at specified gate voltage and collector current.

## 5.2.4 Gate-emitter threshold voltage $(V_{GE(th)})$

Minimum and maximum values at specified collector-emitter voltage and collector current.

## 5.2.5 Collector-emitter cut-off current ( $I_{CE^*}$ )

Maximum value at specified high collector-emitter voltage and for a specified termination between gate and emitter terminals.

## 5.2.6 Gate leakage current (I<sub>GES</sub>)

Maximum value at the maximum rated gate-emitter voltage.

## 5.2.7 Capacitances

Typical values of the following, at specified collector-emitter voltage and test frequency.

#### 5.2.7.1 Input capacitance ( $C_{ies}$ )

Typical input capacitance as small-signal value, in common-emitter configuration, under specified bias conditions and at a specified frequency, with the output short-circuited to a.c.

## 5.2.7.2 Output capacitance ( $C_{oes}$ )

Typical output capacitance as small-signal value, in common-emitter configuration, under specified bias conditions and at a specified frequency, with the input short-circuited to a.c.

## 5.2.7.3 Reverse transfer capacitance ( $C_{res}$ )

Typical reverse transfer capacitance as small-signal value, in common-emitter configuration, under specified bias conditions and at a specified frequency.

## 5.2.8 Gate charge $(Q_G)$

Typical value at specified values of gate-emitter voltage, collector-emitter voltage before turn-on and collector current after turn-on.

## 5.2.9 Internal gate resistance $(r_{q})$

Maximum and/or typical value with collector short circuited to emitter in a.c. at the specified values of gate -emitter voltage, collector -emitter voltage and frequency

## 5.2.10 Turn-on energy $(E_{on})$

Maximum value per pulse under the following specified conditions:

- collector-emitter voltage before turn-on;

- collector current after turn-on;

- load conditions:

- gate-emitter voltage;

- resistance in the gate-emitter circuit;

- case or ambient temperature or virtual junction temperature.

## 5.2.11 Turn-off energy ( $E_{off}$ )

Maximum value per pulse under the following specified conditions:

- collector current before turn-off;

- collector-emitter voltage after turn-off;

- · load conditions;

- gate-emitter voltage;

- resistance in the gate-emitter circuit;

- case or ambient temperature or virtual junction temperature.

#### 5.2.12 Switching times

## 5.2.12.1 Turn-on delay time $(t_{d(on)})$ and rise time $(t_r)$

Maximum values under the following specified conditions:

- collector-emitter voltage before turn-on;

- collector current after turn-on,

- load conditions:

- gate-emitter voltage;

- resistance in the gate-emitter circuit.

## 5.2.12.2 Turn-off delay time $(t_{d(off)})$ , fall time $(t_f)$ and tail time $(t_z)$

Maximum values with a free-wheeling diode connected under the following specified conditions:

- · collector-emitter voltage after turn-off;

- collector current before turn-off;

- load conditions;

- gate-emitter voltage;

- resistance in the gate-emitter circuit.

## 5.2.13 Thermal resistance junction to case $(R_{th(i-c)})$

Maximum value for case-rated IGBTs.

## 5.2.14 Thermal resistance junction to ambient $(R_{th(i-a)})$

Maximum value for ambient-rated IGBTs.

## 5.2.15 Transient thermal impedance junction to case $(Z_{th(i-c)})$

For case-rated IGBTs, diagram showing the maximum values against the time elapsed after a step change in power dissipation, or analytical elements.

## 5.2.16 Transient thermal impedance junction to ambient $(Z_{th(j-a)})$

For ambient-rated IGBTs, diagram showing the maximum values against the time elapsed after a step change in power dissipation.

## 6 Measuring methods

#### 6.1 General

The polarities shown in these circuits are applicable to N channel devices. The circuits can be adapted for P channel devices by inverting the polarities of the meters, generators and power supplies. The handling precautions given in IEC 61340 and the measuring method procedures given in 60747-1 apply.

## 6.2 Verification of ratings (limiting values)

After the following test, confirm the IGBT characteristics specified in Table 1.

$\begin{array}{c|c} \textbf{Characteristics} & \textbf{Acceptance criteria} \\ & I_{\text{CES}} & I_{\text{CES}} < \text{USL} \\ & I_{\text{GES}} & I_{\text{GES}} < \text{USL} \\ & & & & & & & & & & & & \\ \hline & V_{\text{CE(sat)}} & & & & & & & & & & \\ \hline & V_{\text{GE(th)}} & & & & & & & & & & & \\ \hline & V_{\text{GE(th)}} & & & & & & & & & & & \\ \hline \end{array}$

Table 1 – Acceptance-defining characteristics

NOTE USL: upper specification limit LSL: lower specification limit

## 6.2.1 Collector-emitter voltages ( $V_{CES}$ , $V_{CER}$ , $V_{CEX}$ )

## **6.2.1.1** Purpose

To verify that an IGBT withstands the rated collector-emitter voltages  $V_{\text{CES}}$ ,  $V_{\text{CER}}$  or  $V_{\text{CEX}}$  under specified conditions.

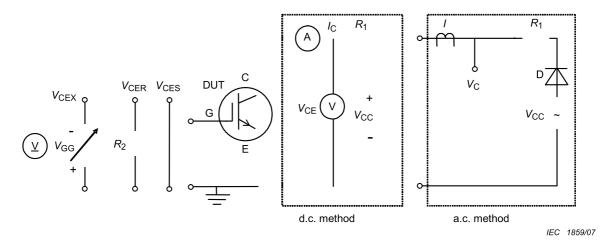

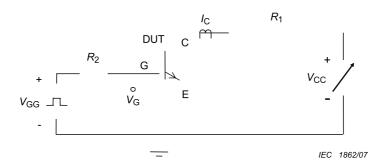

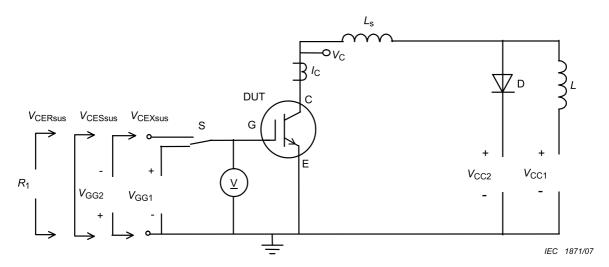

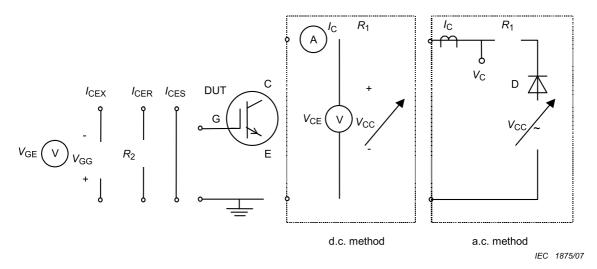

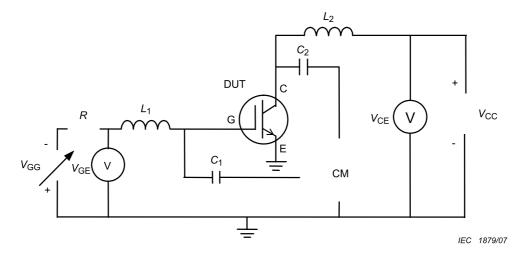

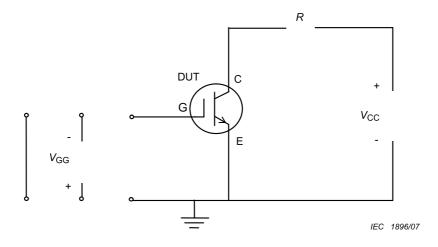

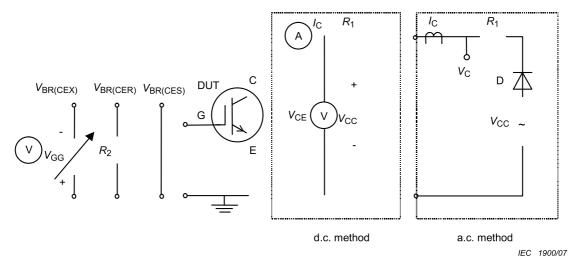

## **6.2.1.2** Circuit diagram (see Figure 1)

DUT (device under test)

Figure 1 – Circuit for measuring the collector-emitter voltages  $V_{CES}$ ,  $V_{CER}$ ,  $V_{CEX}$

## 6.2.1.3 Circuit description

$V_{\rm CC}$  and  $V_{\rm GG}$  are the voltage supply.  $R_1$  is a circuit protection resistor.

## 6.2.1.4 Test procedure

There are two methods, i.e. the d.c. method and the a.c. method, with circuits according to Figure 1.

The specified conditions between gate and emitter shall be applied. The collector-emitter voltage is set to the specified value.

## 6.2.1.5 Specified conditions

- Collector-emitter voltage V<sub>CE</sub>

- Ambient or case or virtual junction temperature  $T_{a}$  or  $T_{c}$  or  $T_{vj}$

- V<sub>CEX</sub>: gate-emitter voltage –V<sub>GG</sub>

- V<sub>CER</sub>: resistor connected between gate and emitter

- V<sub>CES</sub>: short circuit between gate and emitter

## 6.2.2 Gate-emitter voltage with collector emitter short circuit ( $\pm V_{GES}$ )

## **6.2.2.1** Purpose

To verify that an IGBT withstands the rated gate emitter voltage  $\pm V_{\text{GE}}$  under specified conditions.

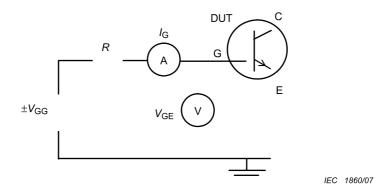

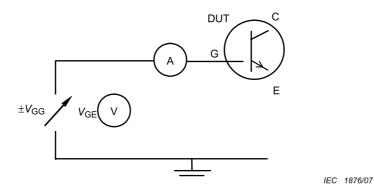

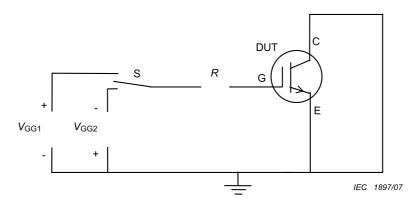

## **6.2.2.2** Circuit diagram (see Figure 2)

Figure 2 – Circuit for testing the gate-emitter voltage  $\pm V_{GES}$

## 6.2.2.3 Circuit description

$V_{\rm GG}$  is the voltage supply. R is a circuit protection resistor.

## 6.2.2.4 Test procedure

The gate-emitter voltage  $V_{GE}$  is set to the specified value. A small protective resistor R is to be provided.

## 6.2.2.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_{a}$  or  $T_{c}$  or  $T_{vj}$

- Gate-emitter leakage current I<sub>GES</sub>

- Short circuit between collector and emitter

## 6.2.3 Maximum collector current $(I_C)$

#### 6.2.3.1 Purpose

To verify that the collector current capability of an IGBT is not less than the maximum rated value  $I_{\rm C}$  under specified conditions.

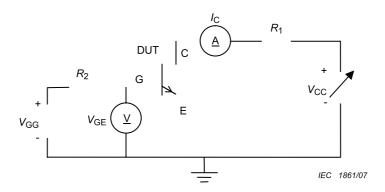

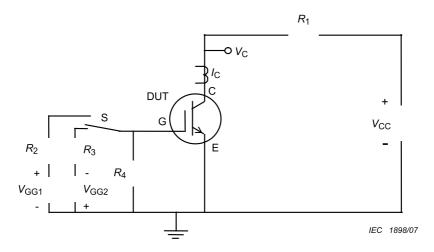

## 6.2.3.2 Circuit diagram (see Figure 3)

Figure 3 - Circuit for measuring collector current

## 6.2.3.3 Circuit description

$V_{\rm CC}$  and  $V_{\rm GG}$  are the voltage supply.  $R_1$  is a circuit protection resistor.

## 6.2.3.4 Test procedure

The temperature ( $T_a$  or  $T_c$ ) and the gate-emitter voltage are set and kept to the specified values. The supply voltage ( $V_{CC}$ ) is increased until  $I_C$  reaches the specified value. The thermal equilibrium might be reached.

## 6.2.3.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$

- Collector current I<sub>C</sub>

- Gate-emitter voltage V<sub>GE</sub>

## 6.2.4 Maximum peak collector current $(I_{CM})$

## 6.2.4.1 **Purpose**

To verify that the peak collector current capability of an IGBT is not less than the maximum rated value  $I_{\text{CM}}$  under specified conditions.

## 6.2.4.2 Circuit diagram (see Figure 4)

Figure 4 - Circuit for measuring peak collector current

## 6.2.4.3 Circuit description

$V_{\rm CC}$  is the voltage supply and  $V_{\rm GG}$  is the gate pulse generator.  $R_{\rm 1}$  is a circuit protection resistor.

## 6.2.4.4 Test procedure

The temperature  $(T_a \text{ or } T_c \text{ or } T_{vj})$  and the gate-emitter voltage are set and kept at the specified values. The supply voltage  $(V_{cc})$  is increased until  $I_C$  reaches the specified value.

## 6.2.4.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_{\rm a}$  or  $T_{\rm c}$  or  $T_{

m vi}$

- Collector current I<sub>CM</sub>

- Gate emitter voltage, pulse width and duty cycle

## 6.2.5 Maximum reverse biased safe operating area (RBSOA)

## 6.2.5.1 **Purpose**

To verify that the IGBT operates reliably without failure in RBSOA.

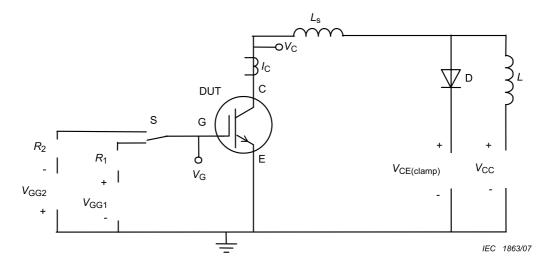

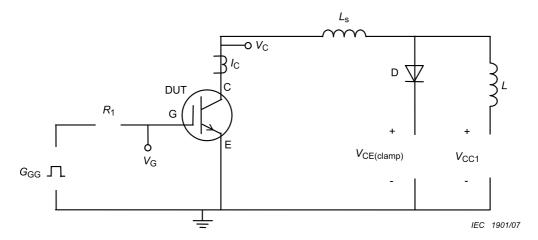

## **6.2.5.2** Circuit diagram and waveforms (see Figure 5 and Figure 6)

Figure 5 – Test circuit of reverse safe operating area (RBSOA)

Figure 6 – Waveforms of gate-emitter voltage  $V_{\rm GE}$  and collector current  $I_{\rm C}$  during turn-off

## 6.2.5.3 Circuit description and requirements

The value of load inductance L shall be high enough to maintain the specified  $I_{\rm C}$  and  $V_{\rm CE(clamp)}$  to the DUT for least the whole duration of the fall and tail time.  $V_{\rm CC}$  is a low voltage to supply the on-state collector current  $I_{\rm C}$ .  $V_{\rm CE(clamp)}$  must be capable of carrying a reverse current equal to  $I_{\rm C}$ , while maintaining the specified voltage. Alternatively, a single voltage source capable of supplying the special  $I_{\rm C}$  at the specified  $V_{\rm CE}$  and with diode D in parallel with inductor L may be used.  $R_1$  and  $R_2$  are circuit protection resistors.  $L_{\rm S}$  is an inductor representing the maximum permitted unclamped stray inductance.

## 6.2.5.4 Test procedure

DUT is turned off at specified  $I_{\rm C}$ .

$V_{CE}$  and  $I_{C}$  are monitored. The DUT has to turn off  $I_{C}$  and withstand  $V_{CE} = V_{CE(clamp)}$ .

NOTE Collector-emitter peak voltage  $V_{CEM} < V_{(BR)CE^*}$ .

## 6.2.5.5 Specified conditions

- Collector current I<sub>C</sub>

- Gate emitter voltage V<sub>GE1</sub> and V<sub>GE2</sub>

- Collector-emitter voltage V<sub>CE(clamp)</sub>

- Single-pulse or repetition rate

- Inductance L

- Value of unclamped stray inductance L<sub>s</sub>

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

- Gate resistor R<sub>1</sub>, R<sub>2</sub>

## 6.2.6 Maximum short-circuit safe operating area (SCSOA)

#### **6.2.6.1** Purpose

To verify that the IGBT operates reliably without failure during a load short-circuit condition. Two types of load short circuit can occur. The first one is to switch the IGBT on to an existing load short circuit. Another one is when the IGBT is already in the on-state  $V_{\text{CE}} = V_{\text{CEsat}}$ , and then the load short circuit occurs. Both methods must be applied.

## 6.2.6.2 Maximum short-circuit safe operating area 1 (SCSOA1)

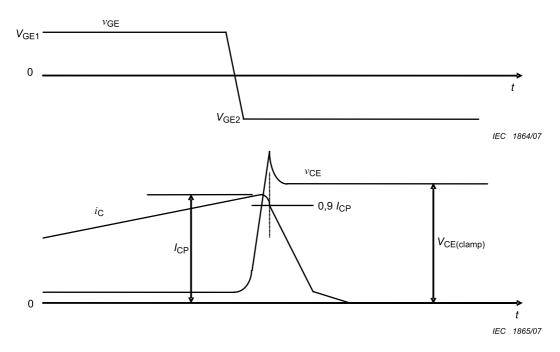

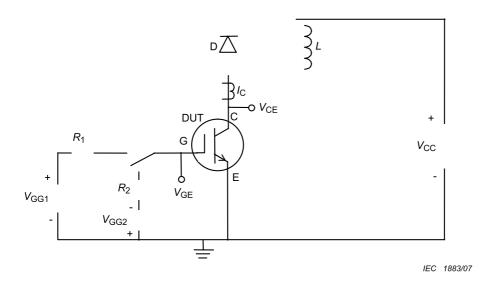

## **6.2.6.2.1** Circuit diagram and waveforms (see Figure 7 and Figure 8)

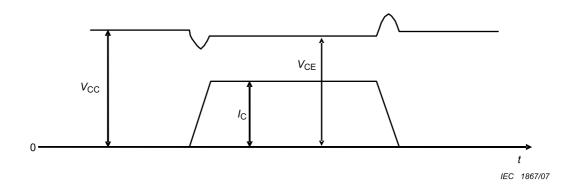

Figure 7 - Circuit for testing safe operating pulse width at load short circuit (SCSOA1)

Figure 8 – Waveforms of gate-emitter voltage  $V_{\rm GE}$ , collector current  $I_{\rm C}$  and voltage  $V_{\rm CE}$  during load short-circuit condition SCSOA1

## 6.2.6.2.2 Circuit description

$L_{\rm s}$  represents the maximum permitted stray inductance, it must be low enough to ensure that maximum short-circuit current is reached within the first 25 % of the gate pulse width  $t_{\rm psc.}$

## 6.2.6.2.3 Test procedure

Set the temperature to the specified value. Apply the specified off-state gate-emitter voltage. Set the collector-emitter voltage to the specified value. Apply the specified gate-emitter on-state pulse.  $I_{\rm C}$ ,  $V_{\rm CE}$  and  $V_{\rm GE}$  are monitored in order to see whether the IGBT turns on and off correctly.

## 6.2.6.2.4 Specified conditions

- Collector-emitter voltage  $V_{CE} = V_{CC}$

- On and off-state gate-emitter voltage V<sub>GE</sub>

- Gate pulse width  $t_{psc}$

- Gate resistors R<sub>1</sub>, R<sub>2</sub>

- Value of stray inductance L<sub>s</sub>

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

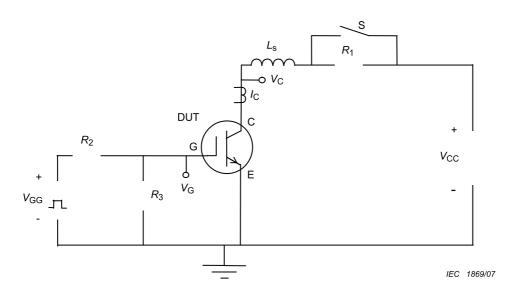

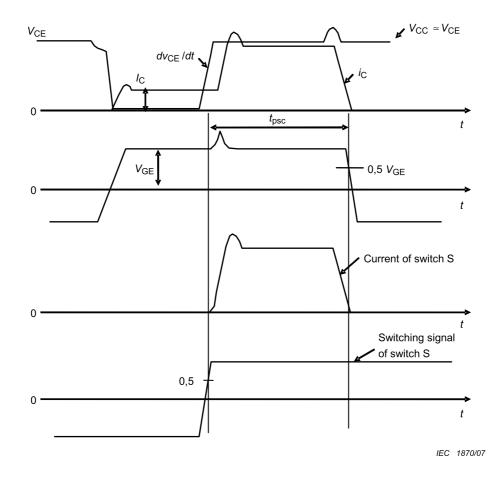

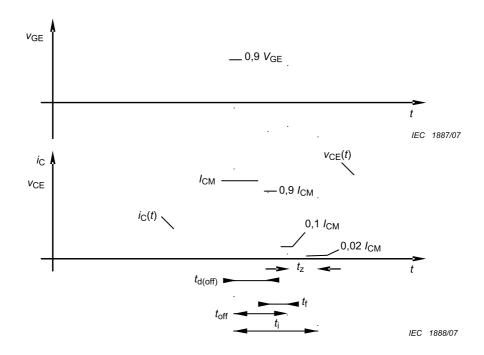

## 6.2.6.3 Maximum short-circuit safe operating area 2 (SCSOA2)

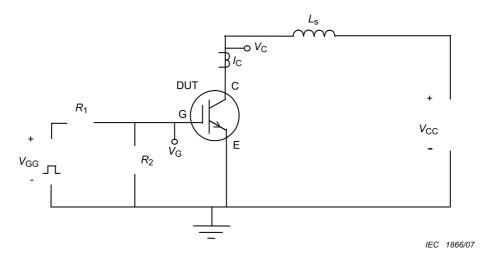

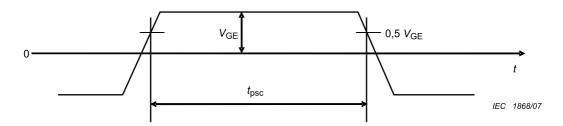

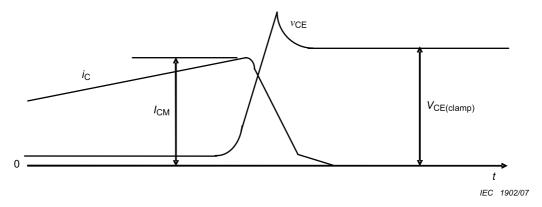

## 6.2.6.3.1 Features of the operation

The gate voltage increases from the gate-emitter voltage  $V_{\rm GE}$  by the  $dv_{\rm CE}/dt$  of the collector-emitter voltage  $V_{\rm CE}$ . It induces the fast increase of the collector current and high peak energy, as shown in Figure 10.

## **6.2.6.3.2** Circuit diagram and operating waveforms (see Figure 9 and Figure 10)

Figure 9 – Short-circuit safe operating area 2 (SCSOA2)

Figure 10 – Waveforms during SCSOA2

## 6.2.6.3.3 Circuit description

$L_{\rm S}$  is an inductor representing the maximum permitted unclamped stray inductance. Switch S in the circuit should have much lower impedance compared to the device under test (DUT). The type name or characteristics of switch S should be specified.

#### 6.2.6.3.4 Test procedure

Set the temperature to the specified value. Apply the specified off-state gate-emitter voltage. Set the collector-emitter voltage to the specified value. Apply the specified gate-emitter on-state pulse. The current capability of switch S should be substantially larger than the expected short-circuit current of the DUT.  $I_{\rm C}$ ,  $V_{\rm CE}$ ,  $V_{\rm GE}$  and the switching signal of the switch S are monitored in order to see whether the IGBT turns on and off correctly.

#### 6.2.6.3.5 Specified conditions

- Collector current prior to short circuit I<sub>C</sub> (= Vcc / R<sub>1</sub>)

- Collector-emitter voltage V<sub>CE</sub> ≈ V<sub>CC</sub>

- On and off-state gate-emitter voltage V<sub>GE</sub>

- Gate pulse width tpsc

- Gate resistors R<sub>2</sub>, R<sub>3</sub>

- Value of unclamped stray inductance L<sub>s</sub>

- Type name or characteristics of switch S, if restrictive

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

#### 6.3 Methods of measurement

## 6.3.1 Collector-emitter sustaining voltage ( $V_{CE*sus}$ )

## 6.3.1.1 **Purpose**

The purpose is to ensure that the collector-emitter sustaining voltage of an IGBT is not less than the maximum specified value  $V_{CE^*sus}$  under specified conditions.

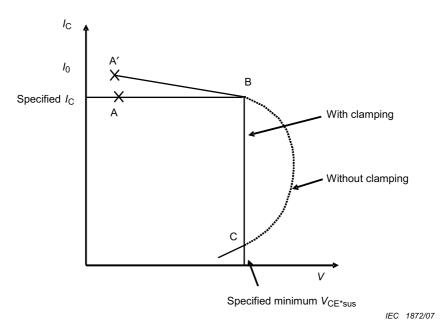

## **6.3.1.2** Circuit diagram (see Figure 11)

Figure 11 – Circuit for measuring the collector-emitter sustaining voltage V<sub>CE\*sus</sub>

## 6.3.1.3 Circuit description and requirements

The IGBT is operated in a saturated condition under pulse operation.

Due to the inductance L, switching off the gate voltage causes the IGBT to be swept through a current-voltage cycle.

The voltage source  $V_{\text{CC1}}$  is adjustable; it enables the collector current to be set to the specified value.

A voltage clamping unit, indicated in Figure 11 as a variable voltage source  $V_{\rm CC2}$  in series with a diode, limits the voltage  $V_{\rm CE}$ .  $V_{\rm CC2}$  is set to the expected value of  $V_{\rm CE^*sus}$ .

The minimum value of load inductance L may be given in the detail specification; otherwise, it may be calculated from

$$L_{\min} = (V_{\text{CC2}} - V_{\text{CC1}}) * t_{\text{off}} / 0.1 I_{\text{C}}$$

This ensures that  $I_{\rm C}$  does not drop by more than 10 % during  $t_{\rm off}$ .

## 6.3.1.4 Test procedure

The clamping unit is adjusted to operate at the specified minimum value  $V_{\text{CE*sus}}$ . With voltage  $V_{\text{CC1}}$  set at zero,  $V_{\text{GE}}$  is adjusted so that the specified current  $I_{\text{C}}$  can be reached with a  $V_{\text{CE}}$  value in the saturated condition (point A in Figure 12).

The value  $V_{\rm CC1}$  is progressively increased until the specified current  $I_{\rm C}$  is reached for the expected  $V_{\rm CE^*sus}$  (point B in Figure 12). As a result, the current at which the cycle starts may reach a value  $I_0$  slightly higher than the specified current  $I_{\rm C}$  (point A' of Figure 12).

Figure 12 – Operating locus of the collector current

## 6.3.1.5 Precautions to be observed

In a preliminary test, the action of the clamping unit should be verified by decreasing its adjustable voltage  $V_2$ ; then the clamping unit should be adjusted to the desired value of  $V_{CE}$  that corresponds to the specified current  $I_C$  (point B of Figure 12).

#### 6.3.1.6 Requirements

- The IGBT is satisfactory when the trace moving from point B to point C does not pass to the left of the line BC.

- When the clamping unit is not used, the IGBT is satisfactory if the trace effectively turns around point B, as shown in Figure 12.

## 6.3.1.7 Specified conditions

- Case or ambient or virtual junction temperature  $T_c$  or  $T_a$  or  $T_{vj}$

- Collector current I<sub>C</sub>

- Minimum sustaining voltage V<sub>CERsus</sub>, V<sub>CESsus</sub>

- Value of load inductance L, where appropriate

- Value of unclamped stray inductance L<sub>s</sub>

- Frequency of the gate voltage pulse generator V<sub>G</sub>, if different from 50 Hz

- Gate resistor R<sub>1</sub>, R<sub>2</sub>, if available

- Gate voltage V<sub>GG1</sub> and V<sub>GG2</sub> (shall be specified)

## 6.3.2 Collector-emitter saturation voltage ( $V_{CEsat}$ )

## 6.3.2.1 **Purpose**

To measure the collector-emitter saturation voltage of an IGBT under specified conditions.

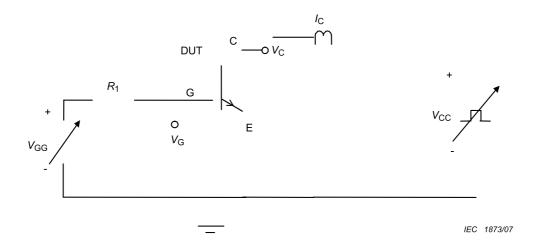

## **6.3.2.2** Circuit diagram (see Figure 13)

Figure 13 - Circuit for measuring the collector-emitter saturation voltage V<sub>CEsat</sub>

## 6.3.2.3 Circuit description

$V_{\rm GG}$  is the voltage supply. The source  $V_{\rm CC}$  provides short collector current pulses, without any significant heat specified.

#### 6.3.2.4 Precautions

No significant heat dissipation shall occur in the IGBT during the measurement.

## 6.3.2.5 Measurement procedure

The temperature is set to the specified value, adapted to the specified values in the gate-emitter voltage and the collector current. The collector-emitter saturation voltage  $V_{\text{CE}} = V_{\text{CEsat}}$  is measured.

## 6.3.2.6 Specified conditions

- Ambient or case or virtual junction temperature  $T_{vi}$

- Gate-emitter voltage V<sub>GE</sub>

- Collector current I<sub>C</sub>

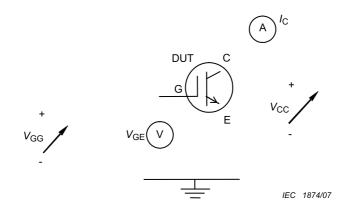

## 6.3.3 Gate-emitter threshold voltage ( $V_{GE(th)}$ )

#### 6.3.3.1 **Purpose**

To measure the gate-emitter threshold voltage of an IGBT under specified conditions.

## **6.3.3.2** Circuit diagram (see Figure 14)

Figure 14 - Basic circuit for measuring the gate-emitter threshold voltage

## 6.3.3.3 Circuit description

$V_{\rm CC}$  and  $V_{\rm GG}$  are the voltage supply.

## 6.3.3.4 Measurement procedure

The device temperature and the collector-emitter voltage are set to the specified value. The gate-emitter voltage  $V_{\rm GE}$  is increased until the specified collector current  $I_{\rm C}$  is reached. The gate-emitter voltage at this current is measured.

## 6.3.3.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

- Collector-emitter voltage V<sub>CE</sub>

- Collector current I<sub>C</sub>

## 6.3.4 Collector cut-off current ( $I_{CES}$ , $I_{CER}$ , $I_{CEX}$ )

## 6.3.4.1 **Purpose**

To measure the collector cut-off current of an IGBT under specified conditions.

## 6.3.4.2 Circuit diagram (see Figure 15)

Figure 15 - Circuit for measuring the collector cut-off current

## 6.3.4.3 Circuit description

$V_{\rm CC}$  and  $V_{\rm GG}$  are the voltage supply.  $R_1$  is a circuit protection resistor.

## 6.3.4.4 Measurement procedure

There are two methods, i.e. the d.c. method and the a.c. method, as shown in Figure 15. The temperature is set to the specified value. The voltage  $V_{\rm CE}$  is increased until it reaches the specified value. The cut-off currents  $I_{\rm CEX}$ ,  $I_{\rm CER}$ ,  $I_{\rm CES}$  are read on the ampere meter or the current probe.

## 6.3.4.5 Specified conditions

- V<sub>CC</sub> in a.c. method with a frequency of 50 Hz or 60 Hz unless otherwise specified

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

- Collector-emitter voltage V<sub>CE</sub>

- I<sub>CER</sub>: resistor R<sub>2</sub> connected between gate and emitter

- I<sub>CES</sub>: short circuit between gate and emitter

- I<sub>CEX</sub>: gate emitter voltage

## 6.3.5 Gate leakage current ( $I_{GES}$ )

## **6.3.5.1** Purpose

To measure the gate-emitter leakage current of an IGBT with the collector emitter short circuited.

## **6.3.5.2 Circuit diagram** (see Figure 16)

Figure 16 - Circuit for measuring the gate leakage current

## 6.3.5.3 Circuit description

$V_{\rm GG}$  is the voltage supply.

## 6.3.5.4 Measurement procedure

Collector and emitter terminals are shorted. The gate-emitter voltage is set to the specified value. The gate-emitter leakage current is measured.

## 6.3.5.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vj}$

- Gate-emitter voltage V<sub>GE</sub>

## 6.3.6 Input capacitance ( $C_{ies}$ )

## 6.3.6.1 Purpose

To measure the input capacitance of an IGBT under specified conditions.

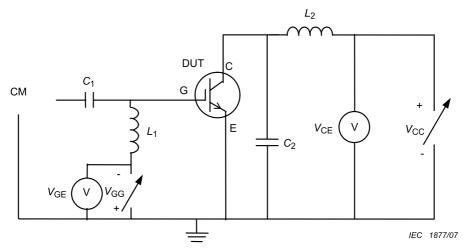

## 6.3.6.2 Circuit diagram (see Figure 17)

Figure 17 - Circuit for measuring the input capacitance

## 6.3.6.3 Circuit description and requirements

CM is a capacitance meter.  $V_{CC}$  and  $V_{GG}$  are adjustable d.c. supplies. Capacitances  $C_1$  and  $C_2$  should present short circuit at the measurement frequency, inductance  $L_1$  and  $L_2$  are to decouple the measurement signal from the d.c. supplies, satisfying the following conditions:

$$1/\omega L_1 \ll |y_{ie}|$$

and  $\omega C_1 \gg |y_{ie}|$

$1/\omega L_2 \ll |y_{0e}|$  and  $\omega C_2 \gg |y_{0e}|$

#### 6.3.6.4 Measurement procedure

CM is set to the specified frequency without the IGBT. The IGBT is inserted into the test socket. The temperature is set to the specified value. The gate-emitter voltage  $V_{\rm GE}$  and the collector-emitter voltage  $V_{\rm CE}$  are set to their specified values. Capacitance  $C_{\rm ies}$  can be read on CM.

## 6.3.6.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vj}$

- Collector-emitter voltage V<sub>CE</sub>

- Gate-emitter voltage V<sub>GE</sub>

- Measurement frequency

## 6.3.7 Output capacitance ( $C_{oes}$ )

## 6.3.7.1 **Purpose**

To measure the output capacitance of an IGBT under specified conditions.

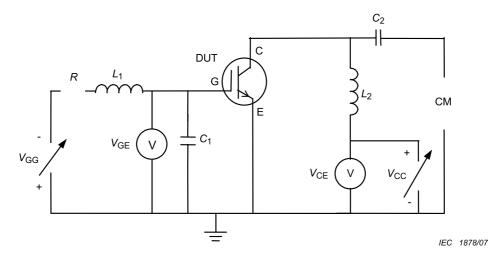

## **6.3.7.2** Circuit diagram (see Figure 18)

Figure 18 - Circuit for measuring the output capacitance

## 6.3.7.3 Circuit description and requirement

CM is a capacitance meter.  $V_{CC}$  and  $V_{GG}$  are adjustable d.c. supplies. Capacitances  $C_1$  and  $C_2$  should present short circuit at the measurement frequency, inductance  $L_1$  and  $L_2$  are to decouple the measurement signal from the d.c. supplies, satisfying the following conditions:

$$1/\omega L_1 \ll |y_{ie}|$$

and  $\omega C_1 \gg |y_{ie}|$

$1/\omega L_2 \ll |y_{0e}|$  and  $\omega C_2 \gg |y_{0e}|$

#### 6.3.7.4 Measurement procedure

CM is set to the specified frequency without the IGBT. The IGBT is inserted into the test socket. The temperature is set to the specified value. The gate-emitter voltage  $V_{\rm GE}$  and the collector-emitter voltage  $V_{\rm CE}$  are set to their specified values respectively. Capacitance  $C_{\rm oes}$  can be read on CM.

## 6.3.7.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

- Collector-emitter voltage V<sub>CF</sub>

- Gate-emitter voltage V<sub>GE</sub>

- Measurement frequency

## 6.3.8 Reverse transfer capacitance ( $C_{res}$ )

## 6.3.8.1 **Purpose**

To measure the reverse transfer capacitance of an IGBT under specified conditions.

## **6.3.8.2** Circuit diagram (see Figure 19)

Figure 19 - Circuit for measuring the reverse transfer capacitance

## 6.3.8.3 Circuit description and requirement

CM is a capacitance meter. Capacitances  $C_1$  and  $C_2$  must form an adequate short circuit for the test frequency. R shall not be too high. Inductance  $L_1$  and  $L_2$  are to decouple the measurement signal from the d.c. supplies.  $V_{\rm GG}$  and  $V_{\rm CC}$  are adjustable d.c. supplies.

## 6.3.8.4 Measurement procedure

CM is set to the specified frequency without the IGBT. The IGBT is inserted into the test socket. The temperature is set to the specified value. The gate-emitter voltage  $V_{\rm GE}$  and the collector-emitter voltage  $V_{\rm CE}$  are set to their specified value. Capacitance  $C_{\rm res}$  can be read on CM.

#### 6.3.8.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

- Collector-emitter voltage V<sub>CE</sub>

- Gate-emitter voltage V<sub>GE</sub>

- Measurement frequency

#### 6.3.9 Gate charge $(Q_G)$

## 6.3.9.1 **Purpose**

To measure gate charge of an IGBT under specified conditions.

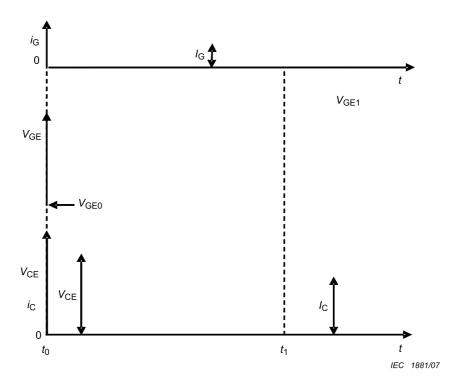

## 6.3.9.2 Circuit diagram and waveforms (see Figure 20 and Figure 21)

Figure 20 - Circuit for measuring the gate charge

Figure 21 – Basic gate charge waveform

## 6.3.9.3 Circuit description

$V_{\rm CC}$  is the voltage supply.  $R_1$  is a circuit protection resistor.

#### 6.3.9.4 Test procedure

The gate is fed with a constant current  $I_{GG}$  until the specified gate emitter voltage is reached.  $V_{CE}$  and  $V_{GE}$  are monitored from zero  $t_0$  to  $t_1$ . Then, the total gate charge can be calculated as follows:

$$Q_{G} = \int_{t_0}^{t_1} i_{G}(t) dt = I_{G} * (t_1 - t_0)$$

#### 6.3.9.5 Specified conditions

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{vi}$

- Collector current I<sub>C</sub>

- Collector emitter voltage V<sub>CE</sub>

- $V_{\text{GE0}}$  at  $t_0$  and  $V_{\text{GE1}}$  at  $t_1$

## 6.3.10 Internal gate resistance $(r_q)$

## 6.3.10.1 Purpose

To measure the internal gate resistance of an IGBT, under specified conditions.

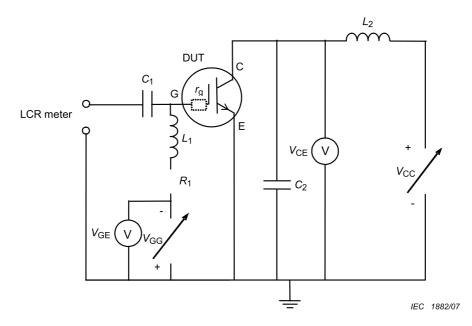

## 6.3.10.2 Circuit diagram (see Figure 22)

Figure 22 - Circuit for measuring the short-circuit internal gate resistance

## 6.3.10.3 Circuit description and requirements

A LCR meter is used, thus making it possible to apply a null method.  $C_2$  should be much larger than  $C_{oes}$  and  $\omega C_1$ , much larger than  $|y_{ie}|$  at the measurement frequency. The impedance of  $L_1$ ,  $L_2$  should be sufficiently high, so that it is possible to compensate it by the bridge adjustments.

$$1/\omega L_1 \ll |y_{ie}|$$

and  $|y_{ie}| \gg \omega C_1$

$$1/\omega L_2 \ll |y_{OS}|$$

and  $|y_{OS}| \gg \omega C_2$

#### 6.3.10.4 Measurement procedure

Collector-emitter voltage  $V_{\text{CE}}$  and gate-emitter voltage  $V_{\text{GE}}$  of DUT are set to specified values and then internal gate resistance  $r_{\text{g}}$  is measured by the LCR meter in series capacitance / resistance mode.

#### 6.3.10.5 Specified conditions

- Collector-emitter voltage V<sub>CE</sub>

- Gate-emitter voltage V<sub>GF</sub>

- Measuring frequency f

- Ambient or case or virtual junction temperature  $T_a$  or  $T_c$  or  $T_{V_i}$

## 6.3.11 Turn-on times $(t_{d(on)}, t_r, t_{on})$ and turn-on energy $(E_{on})$

#### 6.3.11.1 Purpose

To measure the turn-on times  $t_{d(on)}$ ,  $t_r$ ,  $t_{on}$  and turn-on energy  $E_{on}$  of an IGBT under specified conditions with inductive load.

#### 6.3.11.2 Circuit diagram and waveforms (see Figure 23 and Figure 24)

Figure 23 - Circuit for measuring turn-on times and energy

### 6.3.11.3 Circuit description and requirement

D is a freewheeling diode for the current in the inductance *L*.

Figure 24 - Waveforms during turn-on times

#### 6.3.11.4 Measurement procedure

The gate voltage level  $V_{\rm GG1}$  and  $V_{\rm GG2}$  and the supply voltage  $V_{\rm CC}$  are set to the specified values. The IGBT is turned on and turned off twice and then the second turn-on is observed. During the first pulse the current is increased to the specified level. The inductance L has to be large enough to keep the current constant during the free wheeling interval. The collector current  $I_{\rm C}$ , the gate voltage  $V_{\rm GE}$  and collector-emitter voltage  $V_{\rm CE}$  are monitored simultaneously.

$E_{\rm on}$  is the integral of  $V_{\rm CE} \times I_{\rm C} \times dt$ . Integral time  $t_{\rm i}$  starts from the 10 % rise point of  $V_{\rm GE}$  and ends at the specified low  $V_{\rm CE}$  point, the 2 % point of  $V_{\rm CC}$ . The turn-on power dissipation is the product of the switching frequency and the turn-on energy per pulse as determined by the integration.

#### 6.3.11.5 Specified conditions

- Case or ambient or virtual junction temperature of the IGBT and the diode

- Voltage of intermediate circuit V<sub>CC</sub>

- Collector current I<sub>C</sub> just before 1<sup>st</sup> turn-off (I<sub>CM</sub>)

- Gate voltage –V<sub>GE</sub> before and +V<sub>GE</sub> after turn-on

- Gate resistor R<sub>1</sub> (R<sub>G(on)</sub>)

- Characteristics of freewheeling diode

NOTE If there is a free wheeling diode in the same package with the IGBT, this type of diode should be used for the measurement.

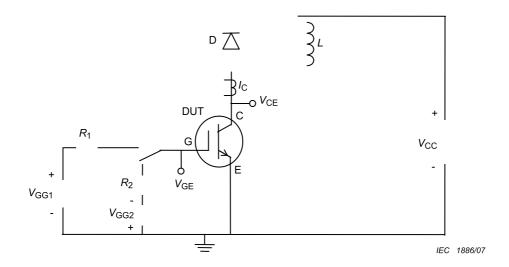

## 6.3.12 Turn-off times ( $t_{d(off)}$ , $t_f$ , $t_{off}$ , $t_z$ ) and turn-off energy ( $E_{off}$ )

#### 6.3.12.1 Purpose

To measure the turn-off times  $t_{\rm d(off)}$ ,  $t_{\rm f}$ ,  $t_{\rm off}$ ,  $t_{\rm z}$  and turn-off energy  $E_{\rm off}$  of an IGBT under specified conditions with inductive load.

## 6.3.12.2 Circuit diagram and waveforms (see Figure 25 and Figure 26)

Figure 25 - Circuit for measuring turn-off times and energy

Figure 26 - Waveforms during turn-off times

## 6.3.12.3 Circuit description and requirement

D is a freewheeling diode for the current in the inductance L.

#### 6.3.12.4 Measurement procedure

The gate voltage level  $V_{\rm GG1}$  and  $V_{\rm GG2}$  and the supply voltage  $V_{\rm CC}$  are set to the specified values. The minimum turn-on pulse duration must ensure a complete saturation of the IGBT. The collector current  $I_{\rm C}$ , the gate emitter voltage  $V_{\rm GE}$  and the collector emitter voltage  $V_{\rm CE}$  are monitored simultaneously.

$E_{\rm off}$  is the integral of  $V_{\rm CE} \times I_{\rm C} \times dt$ . Integral time  $t_{\rm i}$  starts from the 90 % fall point of  $V_{\rm GE}$  and ends at the specified low  $I_{\rm C}$  point, the 2 % point of  $I_{\rm C}$  before turn-off. The turn-off power dissipation is the product of the switching frequency and the turn-off energy per pulse as determined by the integration.

#### 6.3.12.5 Specified conditions

- Case or ambient or virtual junction temperature of the IGBT and the diode

- Voltage of intermediate circuit V<sub>CC</sub>

- Collector current before turn-off (I<sub>CM</sub>)

- Gate voltage +V<sub>GE</sub> before and -V<sub>GE</sub> after turn-off

- Gate resistor R<sub>2</sub> (R<sub>G(off)</sub>)

## 6.3.13 Thermal resistance junction to case $(R_{th(j-c)})$ and transient thermal impedance junction to case $(Z_{th(i-c)})$

## 6.3.13.1 Method 1 (using collector emitter voltage at low current as a temperature sensitive parameter)

#### 6.3.13.1.1 Purpose

To measure the thermal resistance junction to case and/or the transient thermal impedance junction to case of an IGBT.

The measurement is made in two steps:

- a) determination of the temperature coefficient of the collector-emitter voltage at the low measuring current;

- b) measurement of the response of the IGBT to a step change in the internal power dissipation.

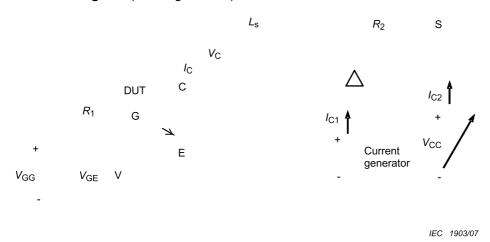

### 6.3.13.1.2 Circuit diagram (see Figure 27)

Figure 27 – Circuit for measuring the variation with temperature of the collectoremitter voltage  $V_{\rm CE}$  at a low measuring current  $I_{\rm C1}$  and for heating up the IGBT by a high current  $I_{\rm C2}$

#### 6.3.13.1.3 Circuit description and requirements

A current source supplies a low continuous direct collector current  $I_{C1}$  which is just sufficient to raise the collector-emitter voltage  $V_{CE}$  above the saturation value. An electronic power switch S supplies on top of  $I_{C1}$  a high collector current  $I_{C2}$ . After switching  $I_{C2}$  off, the IGBT returns to the  $I_{C1}$  conduction.  $R_2$  is a current measuring resistor. In its place, any other appropriate current probe may be used.

#### 6.3.13.1.4 Measurement procedure

a) Determination of the temperature coefficient  $\alpha_{VCE}$  of the collector-emitter voltage  $V_{CE}$  at the low measuring current  $I_{C1}$  (see Figure 28).

The IGBT to be measured is heated subsequently to the temperatures  $T_1$  and  $T_2$  by immersing it in a heated chamber or inert fluid. Thermal equilibrium must be achieved before measurements are taken. At temperature  $T_1$  the collector-emitter voltage at the measuring current  $I_{C1}$  is  $V_{CE1}$ . At a higher temperature  $T_2$  it is  $V_{CE2}$ . Then the temperature coefficient  $\alpha_{VCE}$  is:

$$\alpha_{\text{VCE}} = \frac{V_{\text{CE1}} - V_{\text{CE2}}}{T_2 - T_1}$$

Figure 28 – Typical variation of the collector-emitter voltage  $V_{CE}$  at a low measuring current  $I_{C1}$  with the case temperature  $T_{c}$  (when heated from outside, i.e.  $T_{c} = T_{vi}$ )

b) Measurement of the response to a step change in the internal power dissipation

The IGBT to be measured is fixed on a suitable heatsink. The case temperature  $T_{\rm c1}$  is measured. At that temperature, the measuring current produces the collector-emitter voltage  $V_{\rm CE3}$ . The power switch S is switched on. The high collector current  $I_{\rm C2}$  flows. When thermal equilibrium is established,  $T_{\rm c}$  = const. =  $T_{\rm c2}$  and  $V_{\rm CE}$  =  $V_{\rm CE4}$  are measured. Now  $I_{\rm C2}$  is switched off. Immediately after switch-off, the collector-emitter voltage at  $I_{\rm C1}$  is measured to be  $V_{\rm CE5}$ . Then at that instant

$$T_{vj} = T_{c1} + \frac{V_{CE3} - V_{CE5}}{\alpha_{VCE}}$$

and

$$R_{\text{th(j-c)}} = \frac{T_{\text{vj}} - T_{\text{c2}}}{V_{\text{CE4}} * I_{\text{C2}}}$$

If the transient thermal impedance  $Z_{\text{th(j-c)}}$  is to be determined, the variations with time of  $V_{\text{CE}}$  at  $I_{\text{C1}}$  and of  $T_{\text{c}}$  during the cooling period after switching off  $I_{\text{C2}}$  are plotted, and the  $Z_{\text{th(j-c)}}$  values are calculated point by point using the above equations.

#### 6.3.13.1.4.1 Specified conditions

Reference point for measuring the case temperature

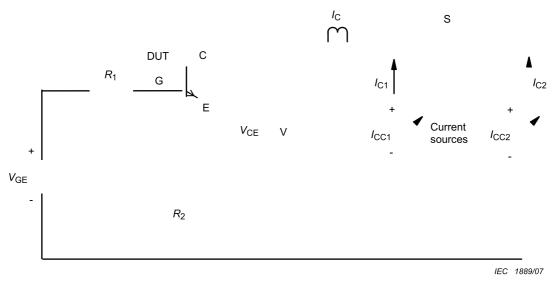

## 6.3.13.2 Method 2 (using the gate-emitter threshold voltage as a temperature-sensitive parameter)

#### 6.3.13.2.1 Purpose

To measure the thermal resistance junction to case and/or the transient thermal impedance junction to case of an IGBT (method 2)

The measurement is made in two steps:

- a) determination of the temperature coefficient of the gate-emitter voltage at the low measuring current;

- b) measurement of the response of the IGBT to a step change in the internal power dissipation.

### 6.3.13.2.2 Circuit diagram (see Figure 29)

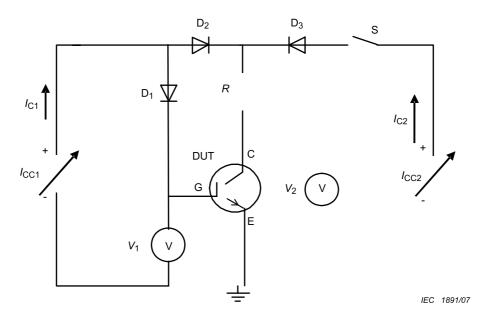

Figure 29 – Circuit for measuring thermal resistance and transient thermal impedance: method 2

### 6.3.13.2.3 Circuit description and requirements

S is an electronic power switch.  $I_{\text{CC1}}$  is an adjustable current source which provides a low continuous direct collector current  $I_{\text{C1}}$  which can make the gate-emitter voltage reach the threshold voltage  $V_{\text{GE(th)}}$  when switch S is opened.  $I_{\text{CC2}}$  is an adjustable current source which provides a high collector current  $I_{\text{C2}}$  when switch S is closed. The  $I_{\text{C2}}$  current shall be high enough to make  $I_{\text{C}}$  ( $I_{\text{C1}} + I_{\text{C2}}$ ) reach its rating.  $I_{\text{C1}}$  and  $I_{\text{C2}}$  are d.c. voltage meters.  $I_{\text{C2}}$  is the current-measuring resistor. Any other appropriate current probe may be used.

#### 6.3.13.2.4 Measurement procedure

a) Determination of the temperature coefficient  $c_{\rm T}$  of the gate-emitter voltage  $V_{\rm GE(th)}$  at the low measuring current  $I_{\rm C1}$  (see Figure 30). The IGBT to be measured is heated subsequently to the temperatures  $T_1$  and  $T_2$  ( $T_2 > T_1$ ) by immersing it in a heated chamber or inert fluid. Thermal equilibrium must be achieved before measurements are taken. At temperature  $T_1$ , the gate-emitter threshold voltage at the measuring current  $I_{\rm C1}$  is  $V_{\rm GE(th)1}$ . At temperature  $T_2$ , it is  $V_{\rm GE(th)2}$ . Then the temperature coefficient  $c_{\rm T}$  is

$$c_{T} = | (V_{GE(th)1} - V_{GE(th)2}) / (T_{2} - T_{1}) | (V/K)$$

Figure 30 – Typical variation of the gate-emitter threshold voltage  $V_{\rm GE(th)}$  at a low measuring current  $I_{\rm C2}$  with the case temperature  $T_{\rm c}$  (when heated from the outside, i.e.  $T_{\rm c}$  =  $T_{\rm vi}$ )

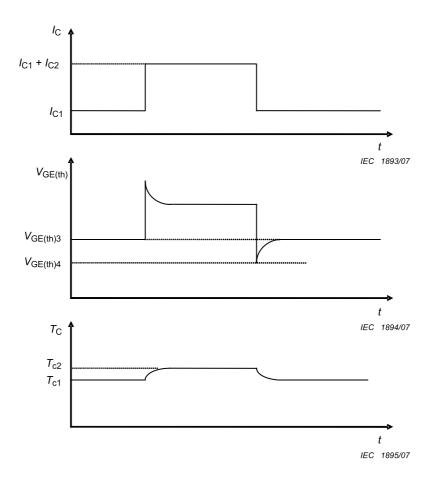

b) Measurement of the response to a step change in the internal power dissipation (see Figure 31)

The IGBT to be measured is fixed on a suitable heat sink. The case temperature  $T_{\rm c1}$  is measured. At that temperature, the measuring current  $I_{\rm C1}$  produces the gate-emitter threshold voltage  $V_{\rm GE(th)3}$ . Switch S is switched on, the high collector current  $I_{\rm C2}$  flows. When thermal equilibrium is established,  $T_{\rm c}$  = const. =  $T_{\rm c2}$  and  $V_{\rm CE}$  are measured.  $I_{\rm C2}$  is then switched off. Immediately after switch-off, the gate-emitter threshold voltage at  $I_{\rm C1}$  is measured to be  $V_{\rm GE(th)4}$ .

Then,

$$T_{\text{vi}} = T_{\text{c1}} + (V_{\text{GE(th)3}} - V_{\text{GE(th)4}}) / cT$$

and

$$R_{\text{th(j-c)}} = (T_{\text{vj}} - T_{\text{c2}}) / (V_{\text{CE}} * I_{\text{C2}})$$

If the transient thermal impedance  $Z_{\text{th(j-c)}}$  is to be determined, the variations with time of  $V_{\text{GE(th)}}$  at  $I_{\text{C1}}$  and of  $T_{\text{c}}$  during the cooling period after switching off  $I_{\text{C2}}$  are plotted, and the  $Z_{\text{th(j-c)}}$  values are calculated point by point using the above equations.

Figure 31 –  $I_C$ ,  $V_{GE}$  and  $T_c$  with time

## 6.3.13.2.5 Specified conditions

Reference point for measuring the case temperature

#### 7 Acceptance and reliability

#### 7.1 General requirements

Subclause 7.2 of IEC 60747-1 is valid.

The testing times of the endurance tests should be introduced in the data sheet.

#### 7.2 Specific requirements

## 7.2.1 List of endurance and reliability tests

A choice of endurance tests is given in Figures 32, 33 and 34.

## 7.2.2 Conditions for endurance and reliability tests

Test conditions and test circuits are described in Figures 32, 33 and 34. The data sheet will state which tests will apply.

## 7.2.3 Acceptance-defining characteristics and criteria for endurance and reliability tests

Acceptance-defining characteristics, their criteria and measurement conditions are listed in Table 2.

NOTE Characteristics should be measured in the sequence in which they are listed in Table 1, because the changes in characteristics caused by some failure mechanisms may be wholly or partially masked by the influence of other measurements. These characteristics are those given in published data sheets. They may be outside the initial production test limits.

Table 2 – Acceptance-defining characteristics for endurance and reliability tests

| Characteristics                                                    | Criteria<br>(see note) | Measurement conditions                 |  |  |

|--------------------------------------------------------------------|------------------------|----------------------------------------|--|--|

| I <sub>CES</sub>                                                   | < USL                  | Specified V <sub>CE</sub>              |  |  |

| I <sub>GES</sub>                                                   | < USL                  | Specified $V_{GE}$                     |  |  |

| V <sub>GE(th)</sub>                                                | > LSL<br>< USL         | Specified $V_{\rm CE}$ and $I_{\rm C}$ |  |  |

| V <sub>CEsat</sub>                                                 | < USL                  | Specified $I_{\mathbb{C}}$             |  |  |

| R <sub>th</sub>                                                    | < USL                  | Specified $I_{\mathbb{C}}$             |  |  |

| NOTE USL: upper specification limit LSL: lower specification limit |                        |                                        |  |  |

#### 7.2.4 Procedure in case of a testing error

The results of tests carried out using inaccurate or faulty test equipment shall not be included for the purpose of device assessment.

#### 7.2.5 Endurance and reliability tests and test methods

## 7.2.5.1 High-temperature blocking (HTRB)

#### 7.2.5.1.1 Operating conditions

- Voltage: preferably 80 % of  $V_{\text{CESmax}}$  or  $V_{\text{CEXmax}}$

- Temperature: preferably maximum virtual junction temperature  $T_{vj(max)}$  or  $T_c = T_{stg(max)} 5$  °C as specified

#### **7.2.5.1.2 Test circuit** (see Figure 32)

Figure 32 - Circuit for high-temperature blockings