### BS IEC 60747-8:2010

# **BSI Standards Publication**

# Semiconductor devices – Discrete devices

Part 8: Field-effect transistors

BS IEC 60747-8:2010 BRITISH STANDARD

#### **National foreword**

This British Standard is the UK implementation of IEC 60747-8:2010. It supersedes BS IEC 60747-8:2000 which is withdrawn.

The UK participation in its preparation was entrusted to Technical Committee EPL/47, Semiconductors.

A list of organizations represented on this committee can be obtained on request to its secretary.

This publication does not purport to include all the necessary provisions of a contract. Users are responsible for its correct application.

© BSI 2011

ISBN 978 0 580 58370 4

ICS 31.080.30

Compliance with a British Standard cannot confer immunity from legal obligations.

This British Standard was published under the authority of the Standards Policy and Strategy Committee on 30 June 2011.

Amendments issued since publication

Amd. No. Date Text affected

IEC 60747-8

Edition 3.0 2010-12

# INTERNATIONAL STANDARD

# NORME INTERNATIONALE

Semiconductor devices – Discrete devices – Part 8: Field-effect transistors

Dispositifs à semiconducteurs – Dispositifs descrets – Partie 8: Transistors à effet de champ

INTERNATIONAL ELECTROTECHNICAL COMMISSION

COMMISSION ELECTROTECHNIQUE INTERNATIONALE

PRICE CODE CODE PRIX

ICS 31.080.30 ISBN 978-2-88912-279-0

### CONTENTS

| 1 Scope                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FO | REWO  | DRD       |                                       | 6  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|-----------|---------------------------------------|----|

| 3.1       Types of field-effect transistors.       9         3.2       General terms.       10         3.2.1       Physical regions (of a field-effect transistor).       10         3.2.2       Functional regions.       11         3.3       Terms related to ratings and characteristics.       12         3.4       Conventional used terms.       17         4.1       General.       17         4.2       Additional general subscripts.       17         4.3       List of letter symbols.       17         4.3.1       Voltage.       17         4.3.2       Currents.       18         4.3.3       Power dissipation.       18         4.3.5 </td <td>1</td> <td>Scop</td> <td>e</td> <td></td> <td>8</td>                                                                      | 1  | Scop  | e         |                                       | 8  |

| 3.1       Types of field-effect transistors       9         3.2       General terms       10         3.2.1       Physical regions (of a field-effect transistor)       10         3.2.2       Functional regions       11         3.3       Terms related to ratings and characteristics       12         3.4       Conventional used terms       17         4       Letter symbols       17         4.1       General       17         4.2       Additional general subscripts       17         4.3       List of letter symbols       17         4.3       List of letter symbols       17         4.3       List of letter symbols       17         4.3       Voltage       17         4.3       Surrents       18         4.3.1       Voltage       17         4.3.2       Currents       18         4.3.3       Power dissipation       18         4.3.4       Small-signal parameters       18         4.3.5       Other parameters       20         4.3.6       Matched-pair field-effect transistors       21         5       Essential ratings and characteristics       22         5.1       General                                                                                                                                                       | 2  | Norm  | native re | eferences                             | 8  |

| 3.2 General terms.       10         3.2.1 Physical regions (of a field-effect transistor)       10         3.2.2 Functional regions.       11         3.3 Terms related to ratings and characteristics.       12         3.4 Conventional used terms.       17         4.1 General.       17         4.1 General.       17         4.2 Additional general subscripts.       17         4.3 List of letter symbols.       17         4.3.1 Voltage.       17         4.3.2 Currents.       18         4.3.3 Power dissipation.       18         4.3.4 Small-signal parameters.       18         4.3.5 Other parameters.       20         4.3.6 Matched-pair field-effect transistors.       21         4.3.7 Inverse diodes integrated in MOSFETs.       21         5 Essential ratings and characteristics.       22         5.1 General.       22         5.1.1 Device categories.       22         5.1.2 Multiple-gate devices.       22         5.2.3 Handling precautions.       22         5.2.1 Temperatures.       22         5.2.2 Power dissipation (P <sub>[0]</sub> ).       22         5.2.3 Safe operating area (SOA) for MOSFET only.       22         5.3.1 Characteristics for low-frequency amplifier.                                              | 3  | Term  | s and d   | efinitions                            | 9  |

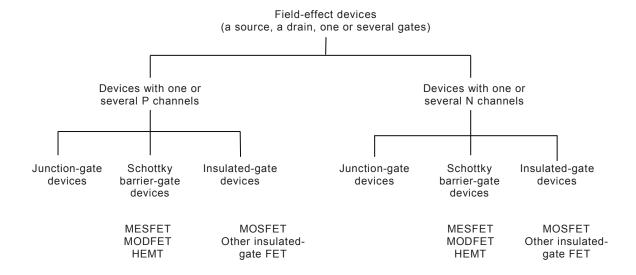

| 3.2 General terms.       10         3.2.1 Physical regions (of a field-effect transistor)       10         3.2.2 Functional regions.       11         3.3 Terms related to ratings and characteristics.       12         3.4 Conventional used terms.       17         4.1 General.       17         4.1 General.       17         4.2 Additional general subscripts.       17         4.3 List of letter symbols.       17         4.3.1 Voltage.       17         4.3.2 Currents.       18         4.3.3 Power dissipation.       18         4.3.4 Small-signal parameters.       18         4.3.5 Other parameters.       20         4.3.6 Matched-pair field-effect transistors.       21         4.3.7 Inverse diodes integrated in MOSFETs.       21         5 Essential ratings and characteristics.       22         5.1 General.       22         5.1.1 Device categories.       22         5.1.2 Multiple-gate devices.       22         5.2.3 Handling precautions.       22         5.2.1 Temperatures.       22         5.2.2 Power dissipation (P <sub>[0]</sub> ).       22         5.2.3 Safe operating area (SOA) for MOSFET only.       22         5.3.1 Characteristics for low-frequency amplifier.                                              |    | 3.1   | Types     | of field-effect transistors.          | 9  |

| 3.2.1 Physical regions (of a field-effect transistor)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |           |                                       |    |

| 3.2.2 Functional regions.       11         3.3 Terms related to ratings and characteristics.       12         3.4 Conventional used terms.       17         4 Letter symbols.       17         4.1 General.       17         4.2 Additional general subscripts.       17         4.3 List of letter symbols.       17         4.3.1 Voltage.       17         4.3.2 Currents.       18         4.3.3 Power dissipation.       18         4.3.4 Small-signal parameters.       18         4.3.5 Other parameters.       20         4.3.6 Matched-pair field-effect transistors.       21         4.3.7 Inverse diodes integrated in MOSFETs.       21         5 Essential ratings and characteristics.       22         5.1 General.       22         5.1.1 Device categories.       22         5.1.2 Multiple-gate devices.       22         5.1.3 Handling precautions.       22         5.2.1 Temperatures.       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only.       22         5.3.1 Characteristics for high-frequency amplifier.       23         5.3.2 Characteristics for high-frequency amplifier.       23         5.3.3 Characteristics for lo                                              |    |       |           |                                       |    |

| 3.3       Terms related to ratings and characteristics       12         3.4       Conventional used terms       17         4       Letter symbols       17         4.1       General       17         4.2       Additional general subscripts       17         4.3       List of letter symbols       17         4.3       List of letter symbols       17         4.3.1       Voltage       17         4.3.2       Currents       18         4.3.3       Power dissipation       18         4.3.4       Small-signal parameters       18         4.3.5       Other parameters       20         4.3.6       Matched-pair field-effect transistors       21         4.3.7       Inverse diodes integrated in MOSFETs       21         5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple-gate devices       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Pt                                                                                                                                           |    |       | 3.2.2     |                                       |    |

| 4       Letter symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 3.3   |           |                                       |    |

| 4.1 General       17         4.2 Additional general subscripts       17         4.3 List of letter symbols       17         4.3.1 Voltage       17         4.3.2 Currents       18         4.3.3 Power dissipation       18         4.3.4 Small-signal parameters       18         4.3.5 Other parameters       20         4.3.6 Matched-pair field-effect transistors       21         4.3.7 Inverse diodes integrated in MOSFETs       21         5 Essential ratings and characteristics       22         5.1.1 Device categories       22         5.1.2 Multiple-gate devices       22         5.1.3 Handling precautions       22         5.2 Ratings (limiting values)       22         5.2.1 Temperatures       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only       22         5.2.4 Voltages and currents       23         5.3 Characteristics for low-frequency amplifier       23         5.3.1 Characteristics for low-frequency amplifier       23         5.3.2 Characteristics for low-level amplifier       30         5.3.5 Characteristics for lotage-controlled resistor       32         5.3.6 Specific characteristics of matched-pair field-effect transistors for low-f           |    | 3.4   | Conve     | ntional used terms                    | 17 |

| 4.2       Additional general subscripts.       17         4.3       List of letter symbols       17         4.3.1       Voltage       17         4.3.2       Currents       18         4.3.3       Power dissipation       18         4.3.4       Small-signal parameters       18         4.3.5       Other parameters       20         4.3.6       Matched-pair field-effect transistors       21         4.3.7       Inverse diodes integrated in MOSFETs       21         5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple square devices       22         5.1.2       Multiple square devices       22         5.1.2       Multiple square devices       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4                                                                                                                                  | 4  | Lette | r symbo   | ols                                   | 17 |

| 4.3       List of letter symbols       17         4.3.1       Voltage       17         4.3.2       Currents       18         4.3.3       Power dissipation       18         4.3.4       Small-signal parameters       18         4.3.5       Other parameters       20         4.3.6       Matched-pair field-effect transistors       21         4.3.7       Inverse diodes integrated in MOSFETs       21         5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple-gate devices       22         5.1.2       Multiple-gate devices       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Pictorial Comperature)       22         5.2.1       Temperat                                                                                                                                           |    | 4.1   | Gener     | al                                    | 17 |

| 4.3.1       Voltage       17         4.3.2       Currents       18         4.3.3       Power dissipation       18         4.3.4       Small-signal parameters       18         4.3.5       Other parameters       20         4.3.6       Matched-pair field-effect transistors       21         4.3.7       Inverse diodes integrated in MOSFETs       21         5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.3       Handling precautions       22         5.2       Ratings (limiting values)       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics for low-frequency amplifier       23         5.3.1       Characteristics for high-frequency amplifier       25 <td></td> <td>4.2</td> <td>Additio</td> <td>onal general subscripts</td> <td> 17</td>                                |    | 4.2   | Additio   | onal general subscripts               | 17 |

| 4.3.2 Currents       18         4.3.3 Power dissipation       18         4.3.4 Small-signal parameters       18         4.3.5 Other parameters       20         4.3.6 Matched-pair field-effect transistors       21         4.3.7 Inverse diodes integrated in MOSFETS       21         5 Essential ratings and characteristics       22         5.1 General       22         5.1.1 Device categories       22         5.1.2 Multiple-gate devices       22         5.1.3 Handling precautions       22         5.2 Ratings (limiting values)       22         5.2.1 Temperatures       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only       22         5.2.4 Voltages and currents       23         5.3 Characteristics       23         5.3.1 Characteristics for low-frequency amplifier       23         5.3.2 Characteristics for high-frequency amplifier       25         5.3.3 Characteristics for high-frequency amplifier       25         5.3.4 Characteristics for high-frequency amplifier       25         5.3.5 Characteristics for low-level amplifier       30         5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33 |    | 4.3   | List of   | letter symbols                        | 17 |

| 4.3.3 Power dissipation       18         4.3.4 Small-signal parameters       18         4.3.5 Other parameters       20         4.3.6 Matched-pair field-effect transistors       21         4.3.7 Inverse diodes integrated in MOSFETs       21         5 Essential ratings and characteristics       22         5.1 General       22         5.1.1 Device categories       22         5.1.2 Multiple-gate devices       22         5.1.3 Handling precautions       22         5.2 Ratings (limiting values)       22         5.2.1 Temperatures       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only       22         5.2.4 Voltages and currents       23         5.3.1 Characteristics       23         5.3.2 Characteristics for low-frequency amplifier       23         5.3.3 Characteristics for high-frequency amplifier       25         5.3.4 Characteristics for high-frequency amplifier       25         5.3.5 Characteristics for high and low power switching and chopper       27         5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6 Measuring methods       34         6.1 General       34            |    |       | 4.3.1     | Voltage                               | 17 |

| 4.3.4       Small-signal parameters       18         4.3.5       Other parameters       20         4.3.6       Matched-pair field-effect transistors       21         4.3.7       Inverse diodes integrated in MOSFETs       21         5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.3       Handling precautions       22         5.2       Ratings (limiting values)       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics       23         5.3.1       Characteristics for low-frequency amplifier       25         5.3.2       Characteristics for high and low power switching and chopper       27         5.3.4       Characteristics for low-level amplifier       30         5.3.5       Characteristics for low-level amplifier       30         5.3.6       Specific characteristics of matched-pair field-effect transistors                                                   |    |       | 4.3.2     | Currents                              | 18 |

| 4.3.5       Other parameters       20         4.3.6       Matched-pair field-effect transistors       21         4.3.7       Inverse diodes integrated in MOSFETs       21         5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.3       Handling precautions       22         5.2       Ratings (limiting values)       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics       23         5.3.1       Characteristics for low-frequency amplifier       23         5.3.2       Characteristics for high-frequency amplifier       25         5.3.3       Characteristics for low-level amplifier       30         5.3.4       Characteristics for low-level amplifier       30         5.3.5       Characteristics for olow-level amplifier       30         5.3.6       Specific characteristics for matched-pair field-effect transisto                                                   |    |       | 4.3.3     | Power dissipation                     | 18 |

| 4.3.6       Matched-pair field-effect transistors       21         4.3.7       Inverse diodes integrated in MOSFETs       21         5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.3       Handling precautions       22         5.2       Ratings (limiting values)       22         5.2.1       Temperatures       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics       23         5.3.1       Characteristics for low-frequency amplifier       23         5.3.2       Characteristics for high-frequency amplifier       25         5.3.3       Characteristics for high-frequency amplifier       25         5.3.4       Characteristics for low-level amplifier       30         5.3.5       Characteristics for low-level amplifier       30         5.3.6       Specific characteristics of matched-pair field-effect transistor                                                   |    |       | 4.3.4     | Small-signal parameters               | 18 |

| 4.3.7 Inverse diodes integrated in MOSFETs       21         5 Essential ratings and characteristics       22         5.1 General       22         5.1.1 Device categories       22         5.1.2 Multiple-gate devices       22         5.1.3 Handling precautions       22         5.2 Ratings (limiting values)       22         5.2.1 Temperatures       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only       22         5.2.4 Voltages and currents       23         5.3 Characteristics       23         5.3.1 Characteristics for low-frequency amplifier       23         5.3.2 Characteristics for high and low power switching and chopper       27         5.3.4 Characteristics for low-level amplifier       30         5.3.5 Characteristics for low-level amplifier       30         5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6 Measuring methods       34         6.1 General       34         6.2 Verification of ratings (limiting values)       34         6.2.1 Voltages and currents       34         6.2.2 Safe operating area       40         6.2.3 Avalanche energy       44                      |    |       | 4.3.5     | Other parameters                      | 20 |

| 5       Essential ratings and characteristics       22         5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.3       Handling precautions       22         5.2       Ratings (limiting values)       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics       23         5.3.1       Characteristics for low-frequency amplifier       23         5.3.2       Characteristics for high-frequency amplifier       25         5.3.4       Characteristics for low-level amplifier       25         5.3.4       Characteristics for low-level amplifier       30         5.3.5       Characteristics for low-level amplifier       30         5.3.6       Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6       Measuring methods       34         6.1       General       34         6.2       Verification of ratings (limiting values)<                                                   |    |       | 4.3.6     | Matched-pair field-effect transistors | 21 |

| 5.1       General       22         5.1.1       Device categories       22         5.1.2       Multiple-gate devices       22         5.1.3       Handling precautions       22         5.2       Ratings (limiting values)       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics       23         5.3.1       Characteristics for low-frequency amplifier       23         5.3.2       Characteristics for high-frequency amplifier       25         5.3.3       Characteristics for low-level amplifier       30         5.3.4       Characteristics for low-level amplifier       30         5.3.5       Characteristics for voltage-controlled resistor       32         5.3.6       Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6       Measuring methods       34         6.1       General       34         6.2       Verification of ratings (limiting values)       34         6.2.1       Voltages and currents                                                        |    |       | 4.3.7     | Inverse diodes integrated in MOSFETs  | 21 |

| 5.1.1 Device categories.       22         5.1.2 Multiple-gate devices       22         5.1.3 Handling precautions       22         5.2 Ratings (limiting values).       22         5.2.1 Temperatures       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only.       22         5.2.4 Voltages and currents.       23         5.3 Characteristics       23         5.3.1 Characteristics for low-frequency amplifier       23         5.3.2 Characteristics for high-frequency amplifier       25         5.3.3 Characteristics for high and low power switching and chopper       27         5.3.4 Characteristics for low-level amplifier       30         5.3.5 Characteristics for voltage-controlled resistor       32         5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6 Measuring methods       34         6.1 General       34         6.2 Verification of ratings (limiting values)       34         6.2.1 Voltages and currents       34         6.2.2 Safe operating area       40         6.2.3 Avalanche energy       44                                                                                        | 5  | Esse  | ntial rat | ings and characteristics              | 22 |

| 5.1.2       Multiple-gate devices.       22         5.1.3       Handling precautions.       22         5.2       Ratings (limiting values).       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot).       22         5.2.3       Safe operating area (SOA) for MOSFET only.       22         5.2.4       Voltages and currents.       23         5.3       Characteristics.       23         5.3.1       Characteristics for low-frequency amplifier.       23         5.3.2       Characteristics for high-frequency amplifier.       25         5.3.3       Characteristics for low-level amplifier.       30         5.3.4       Characteristics for low-level amplifier.       30         5.3.5       Characteristics for voltage-controlled resistor.       32         5.3.6       Specific characteristics of matched-pair field-effect transistors for low-frequency differential.       33         6       Measuring methods.       34         6.1       General.       34         6.2       Verification of ratings (limiting values)       34         6.2.1       Voltages and currents.       34         6.2.2       Safe operating area.       40         6.2.3                                                 |    | 5.1   | Gener     | al                                    | 22 |

| 5.1.3 Handling precautions       22         5.2 Ratings (limiting values)       22         5.2.1 Temperatures       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only       22         5.2.4 Voltages and currents       23         5.3 Characteristics       23         5.3.1 Characteristics for low-frequency amplifier       23         5.3.2 Characteristics for high-frequency amplifier       25         5.3.3 Characteristics for high and low power switching and chopper       27         5.3.4 Characteristics for low-level amplifier       30         5.3.5 Characteristics for voltage-controlled resistor       32         5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6 Measuring methods       34         6.1 General       34         6.2 Verification of ratings (limiting values)       34         6.2.1 Voltages and currents       34         6.2.2 Safe operating area       40         6.2.3 Avalanche energy       44                                                                                                                                                                                  |    |       | 5.1.1     | Device categories                     | 22 |

| 5.2       Ratings (limiting values)       22         5.2.1       Temperatures       22         5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics       23         5.3.1       Characteristics for low-frequency amplifier       23         5.3.2       Characteristics for high and low power switching and chopper       27         5.3.3       Characteristics for low-level amplifier       30         5.3.4       Characteristics for voltage-controlled resistor       32         5.3.5       Characteristics for voltage-controlled resistor       32         5.3.6       Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6       Measuring methods       34         6.1       General       34         6.2       Verification of ratings (limiting values)       34         6.2.1       Voltages and currents       34         6.2.2       Safe operating area       40         6.2.3       Avalanche energy       44                                                                                                               |    |       | 5.1.2     | Multiple-gate devices                 | 22 |

| 5.2.1 Temperatures       22         5.2.2 Power dissipation (Ptot)       22         5.2.3 Safe operating area (SOA) for MOSFET only       22         5.2.4 Voltages and currents       23         5.3 Characteristics       23         5.3.1 Characteristics for low-frequency amplifier       23         5.3.2 Characteristics for high-frequency amplifier       25         5.3.3 Characteristics for high and low power switching and chopper       27         5.3.4 Characteristics for low-level amplifier       30         5.3.5 Characteristics for voltage-controlled resistor       32         5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6 Measuring methods       34         6.1 General       34         6.2 Verification of ratings (limiting values)       34         6.2.1 Voltages and currents       34         6.2.2 Safe operating area       40         6.2.3 Avalanche energy       44                                                                                                                                                                                                                                                                             |    |       | 5.1.3     | Handling precautions                  | 22 |

| 5.2.2       Power dissipation (Ptot)       22         5.2.3       Safe operating area (SOA) for MOSFET only       22         5.2.4       Voltages and currents       23         5.3       Characteristics       23         5.3.1       Characteristics for low-frequency amplifier       23         5.3.2       Characteristics for high-frequency amplifier       25         5.3.3       Characteristics for high and low power switching and chopper       27         5.3.4       Characteristics for low-level amplifier       30         5.3.5       Characteristics for voltage-controlled resistor       32         5.3.6       Specific characteristics of matched-pair field-effect transistors for low-frequency differential       33         6       Measuring methods       34         6.1       General       34         6.2       Verification of ratings (limiting values)       34         6.2.1       Voltages and currents       34         6.2.2       Safe operating area       40         6.2.3       Avalanche energy       44                                                                                                                                                                                                                 |    | 5.2   | Rating    | ,                                     |    |

| 5.2.3 Safe operating area (SOA) for MOSFET only.  5.2.4 Voltages and currents.  5.3 Characteristics.  5.3.1 Characteristics for low-frequency amplifier.  5.3.2 Characteristics for high-frequency amplifier.  5.3.3 Characteristics for high and low power switching and chopper.  5.3.4 Characteristics for low-level amplifier.  5.3.5 Characteristics for voltage-controlled resistor.  5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential.  33  6 Measuring methods.  6.1 General.  6.2 Verification of ratings (limiting values).  6.2.1 Voltages and currents.  34  6.2.2 Safe operating area.  40  6.2.3 Avalanche energy.  44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       | 5.2.1     | ·                                     |    |

| 5.2.4 Voltages and currents.235.3 Characteristics.235.3.1 Characteristics for low-frequency amplifier.235.3.2 Characteristics for high-frequency amplifier255.3.3 Characteristics for high and low power switching and chopper275.3.4 Characteristics for low-level amplifier305.3.5 Characteristics for voltage-controlled resistor325.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential336 Measuring methods346.1 General346.2 Verification of ratings (limiting values)346.2.1 Voltages and currents346.2.2 Safe operating area406.2.3 Avalanche energy44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |       |           | 101                                   |    |

| 5.3 Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       | 5.2.3     |                                       |    |

| 5.3.1 Characteristics for low-frequency amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |       |           |                                       |    |

| 5.3.2 Characteristics for high-frequency amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 5.3   |           |                                       |    |

| 5.3.3 Characteristics for high and low power switching and chopper 27 5.3.4 Characteristics for low-level amplifier 30 5.3.5 Characteristics for voltage-controlled resistor 32 5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential 33 6 Measuring methods 34 6.1 General 34 6.2 Verification of ratings (limiting values) 34 6.2.1 Voltages and currents 34 6.2.2 Safe operating area 40 6.2.3 Avalanche energy 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       | 0.0       | . , ,                                 |    |

| 5.3.4 Characteristics for low-level amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       |           |                                       |    |

| 5.3.5 Characteristics for voltage-controlled resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |           |                                       |    |

| 5.3.6 Specific characteristics of matched-pair field-effect transistors for low-frequency differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       |           | ·                                     |    |

| Iow-frequency differential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |       |           | _                                     | 32 |

| 6       Measuring methods       34         6.1       General       34         6.2       Verification of ratings (limiting values)       34         6.2.1       Voltages and currents       34         6.2.2       Safe operating area       40         6.2.3       Avalanche energy       44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |       | 5.3.6     |                                       | 33 |

| 6.1 General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6  | Meas  | surina m  | ·                                     |    |

| 6.2Verification of ratings (limiting values)346.2.1Voltages and currents346.2.2Safe operating area406.2.3Avalanche energy44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |       | Ū         |                                       |    |

| 6.2.1 Voltages and currents346.2.2 Safe operating area406.2.3 Avalanche energy44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | _     |           |                                       |    |

| 6.2.2 Safe operating area                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | J     |           |                                       |    |

| 6.2.3 Avalanche energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |       |           | -                                     |    |

| 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |           |                                       |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 6.3   |           |                                       |    |

|     |         | 6.3.1                      | Breakdown voltage, drain to source $(V_{(BR)DS^*})$                                                                                        | 46 |

|-----|---------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|     |         | 6.3.2                      | Gate-source off-state voltage ( $V_{\rm GS(off)}$ ) (type A and B), gate source threshold voltage ( $V_{\rm GS(th)}$ ) (type C)            |    |

|     |         | 6.3.3                      | Drain leakage current (d.c.) ( $I_{DS^*}$ )(type C), Drain cut-off current (d.c.) ( $I_{DSX}$ ) (type A and B)                             |    |

|     |         | 6.3.4                      | Gate cut-off current ( $I_{GS^*}$ )(type A), Gate-leakage current ( $I_{GS^*}$ )(type B and C)                                             |    |

|     |         | 6.3.5                      | (Static) drain-source on-state resistance $(r_{\rm DS(on)})$ or drain-source on-state voltage $(V_{\rm DS(on)})$                           | 49 |

|     |         | 6.3.6                      | Switching times $(t_{d(on)}, t_r, t_{d(off)}, and t_f)$                                                                                    | 51 |

|     |         | 6.3.7                      | Turn-on power dissipation ( $P_{on}$ ), turn-on energy (per pulse) ( $E_{on}$ )                                                            | 52 |

|     |         | 6.3.8                      | Turn-off power dissipation ( $P_{\text{off}}$ ), turn-off energy (per pulse) ( $E_{\text{off}}$ )                                          |    |

|     |         | 6.3.9                      | Gate charges (Q <sub>G</sub> , Q <sub>GD</sub> , Q <sub>GS(th)</sub> , Q <sub>GS(pl)</sub> )                                               |    |

|     |         | 6.3.10                     | Common source short-circuit input capacitance $(C_{iss})$                                                                                  |    |

|     |         |                            | Common source short-circuit output capacitance $(C_{oss})$                                                                                 |    |

|     |         |                            | Common source short-circuit reverse transfer capacitance $(C_{rss})$                                                                       |    |

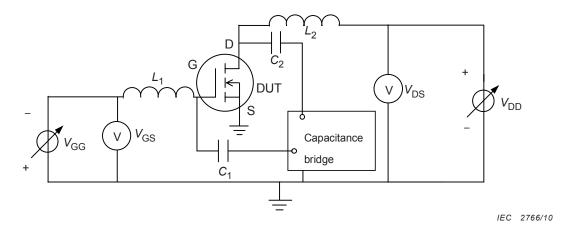

|     |         |                            | Internal gate resistance $(r_q)$                                                                                                           |    |

|     |         |                            | MOSFET forward recovery time ( $t_{\rm fr}$ ) and MOSFET forward recovered charge ( $Q_{\rm f}$ )                                          |    |

|     |         | 6.3.15                     | Drain-source reverse voltage (V <sub>DSR</sub> )                                                                                           |    |

|     |         |                            | Small-signal short-circuit output conductance (type A, B and C) $(g_{oss})$                                                                |    |

|     |         |                            | Small-signal short-circuit forward transconductance (types A, B and C)                                                                     |    |

|     |         | 6.3.18                     | Noise (types A, B and C) (F, Vn)                                                                                                           |    |

|     |         |                            | On-state drain-source resistance (under small-signal conditions) (r <sub>ds(on)</sub> )                                                    |    |

|     |         | 6.3.20                     | Channel-case transient thermal impedance $(Z_{\text{th(j-c)}})$ and thermal resistance $(R_{\text{th(j-c)}})$ of a field-effect transistor |    |

| 7   | Acce    | ptance a                   | and reliability                                                                                                                            |    |

|     | 7.1     |                            | al requirements                                                                                                                            |    |

|     | 7.2     |                            | ance-defining characteristics                                                                                                              |    |

|     | 7.3     |                            | ance and reliability tests                                                                                                                 |    |

|     |         |                            | High-temperature blocking (HTRB)                                                                                                           |    |

|     |         | 7.3.2                      | High-temperature gate bias                                                                                                                 |    |

|     |         | 7.3.3                      | Intermittent operating life (load cycles)                                                                                                  |    |

|     | 7.4     |                            | ests and routine tests                                                                                                                     |    |

|     |         | 7.4.1                      | Type tests                                                                                                                                 |    |

|     |         | 7.4.2                      | Routine tests                                                                                                                              |    |

| Bib | oliogra |                            |                                                                                                                                            |    |

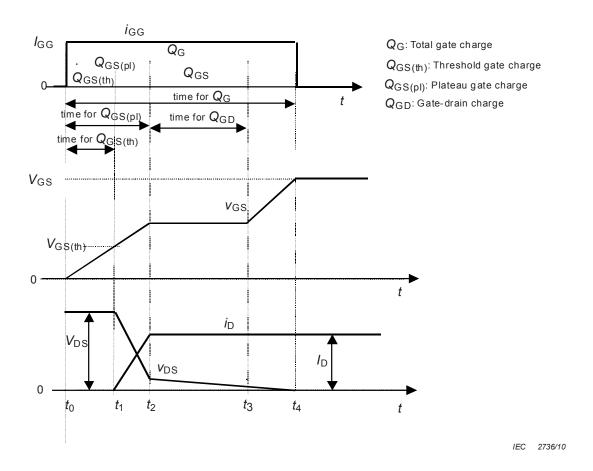

| Fig | gure 1  | – Basic                    | waveforms to specify the gate charges                                                                                                      | 14 |

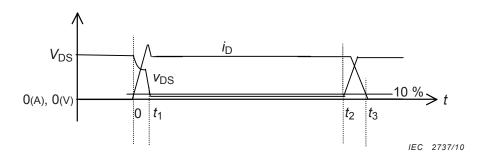

| Fig | gure 2  | <ul><li>Integral</li></ul> | al times for the turn-on energy $E_{on}$ and turn-off energy $E_{off}$                                                                     | 16 |

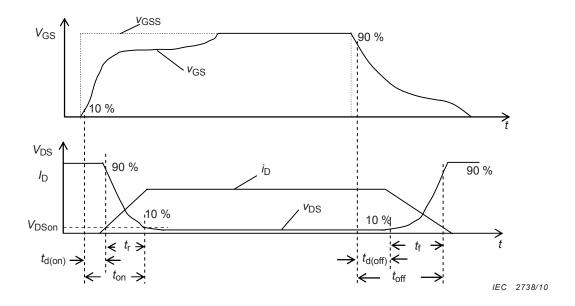

| Fig | gure 3  | <ul><li>Switch</li></ul>   | ning times                                                                                                                                 | 21 |

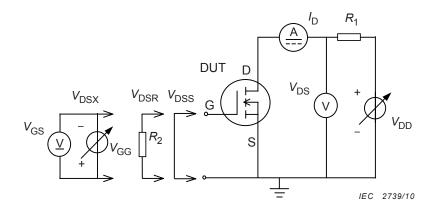

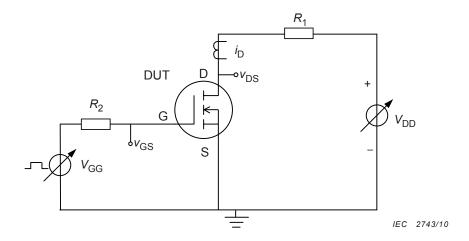

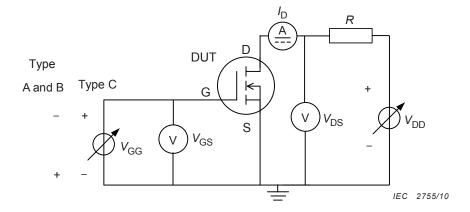

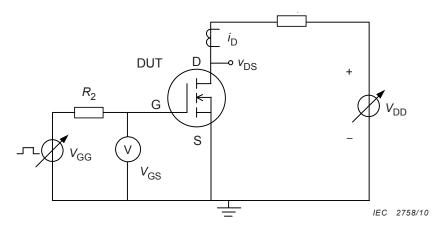

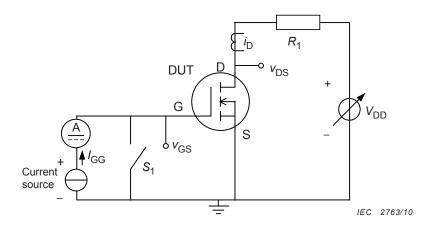

|     |         |                            | t diagram for testing of drain-source voltage                                                                                              |    |

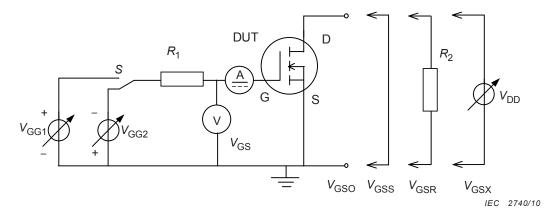

|     |         |                            | t diagram for testing of gate-source voltage                                                                                               |    |

|     |         |                            |                                                                                                                                            |    |

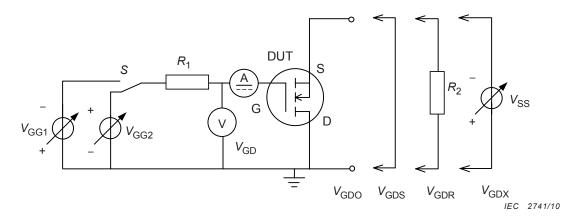

|     |         |                            | t diagram for testing of gate-drain voltage                                                                                                |    |

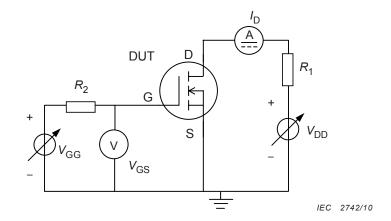

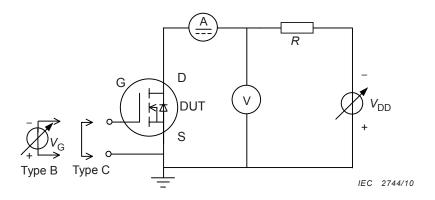

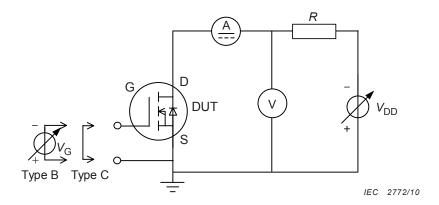

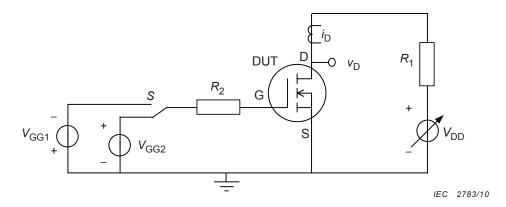

|     |         |                            | circuit for the testing of drain current                                                                                                   |    |

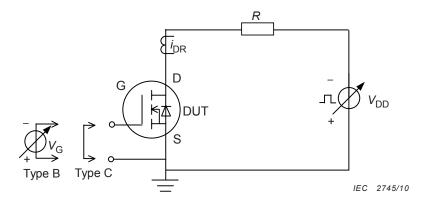

| Fig | gure 8  | – Circui                   | t diagram for testing of peak drain current                                                                                                | 38 |

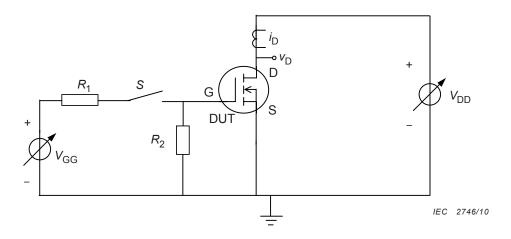

| Fic | gure 9  | – Basic                    | circuit for the testing of reverse drain current of MOSFETs                                                                                | 38 |

| Figure 10 – Basic circuit for the testing of peak reverse drain current of MOSFETs                                                                       | 39 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 11 – Circuit diagram for verifing FBSOA                                                                                                           | 40 |

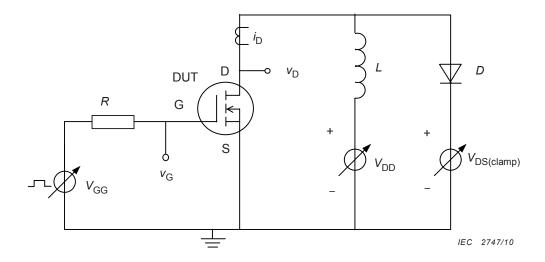

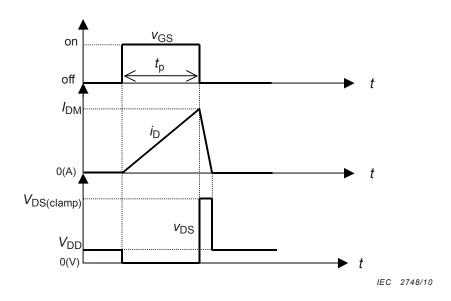

| Figure 12 – Circuit diagram for verifying RBSOA                                                                                                          | 41 |

| Figure 13 – Test waveforms for verifying RBSOA                                                                                                           | 41 |

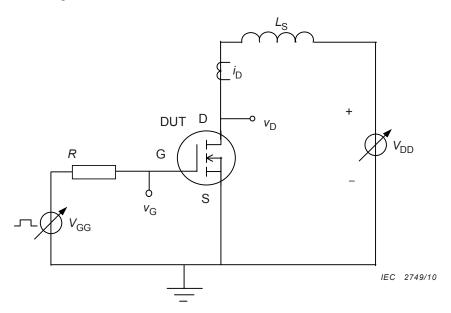

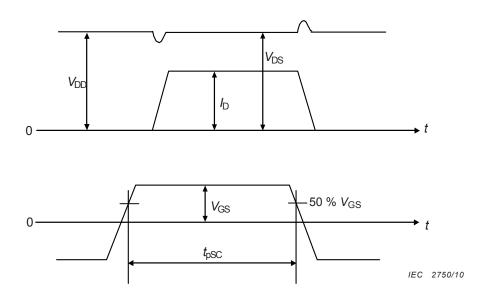

| Figure 14 – Circuit for testing safe operating pulse duration at load short circuit                                                                      | 42 |

| Figure 15 – Waveforms of gate-source voltage $V_{\rm GS}$ , drain current $I_{\rm D}$ and voltage $V_{\rm DS}$ during load short circuit condition SCSOA | 43 |

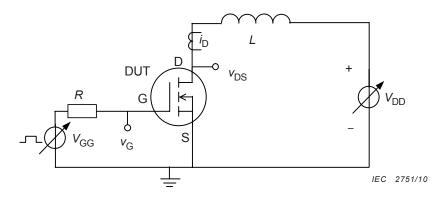

| Figure 16 – Circuit for the inductive avalanche switching                                                                                                | 44 |

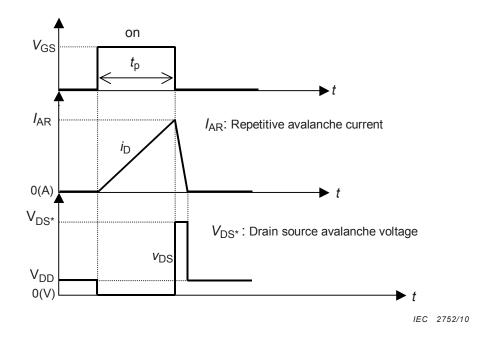

| Figure 17 – Waveforms of $I_{\rm D}$ , $V_{\rm DS}$ and $V_{\rm GS}$ during unclamped inductive switching                                                | 44 |

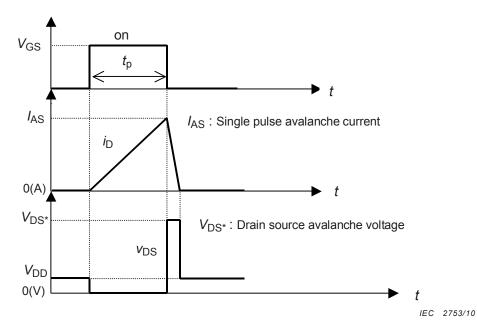

| Figure 18 – Waveforms of $I_{\rm D}$ , $V_{\rm DS}$ and $V_{\rm GS}$ for the non-repetitive avalanche switching                                          | 45 |

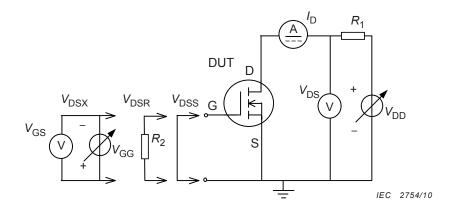

| Figure 19 – Circuit diagrams for the measurement drain-source breakdown voltage                                                                          | 46 |

| Figure 20 – Circuit diagram for measurement of gate-source off-state voltage and gate-source threshold voltage                                           | 47 |

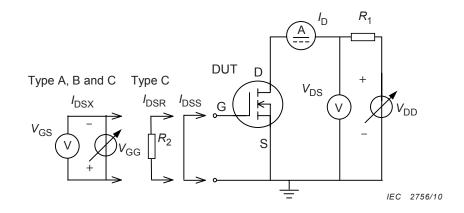

| Figure 21 – Circuit diagram for drain leakage (or off-state) current or drain cut-off current measurement                                                | 48 |

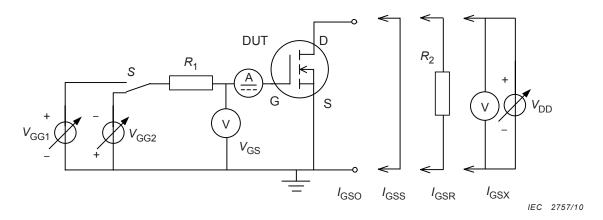

| Figure 22 – Circuit diagram for measuring of gate cut-off current or gate leakage current                                                                | 49 |

| Figure 23 – Basic circuit of measurement for on-state resistance                                                                                         | 50 |

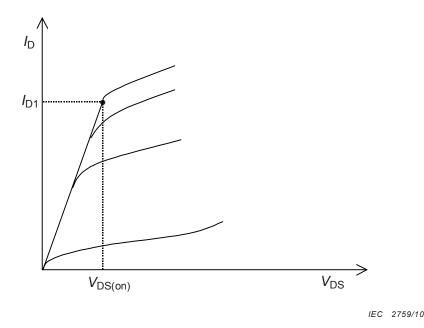

| Figure 24 – On-state resistance                                                                                                                          | 50 |

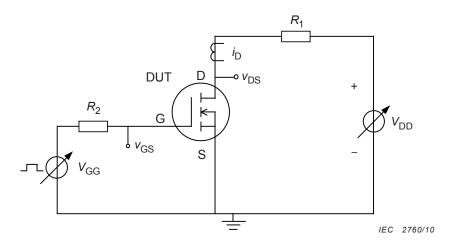

| Figure 25 – Circuit diagram for switching time                                                                                                           |    |

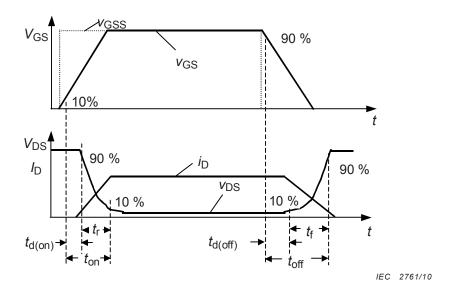

| Figure 26 – Schematic switching waveforms and times                                                                                                      | 51 |

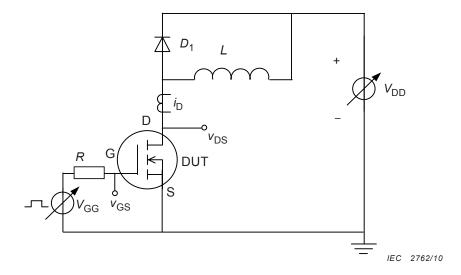

| Figure 27 – Circuit for determining the turn-on and turn-off power dissipation and/or energy                                                             | 52 |

| Figure 28 – Circuit diagrams for the measurement gate charges                                                                                            | 54 |

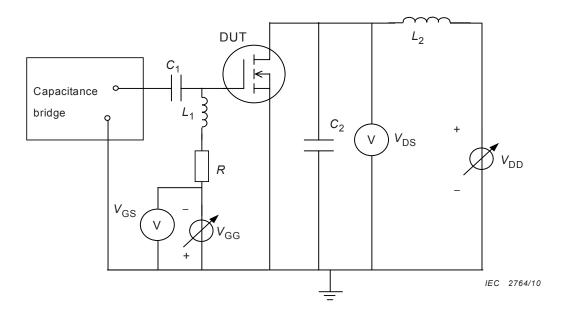

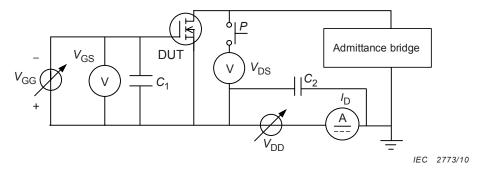

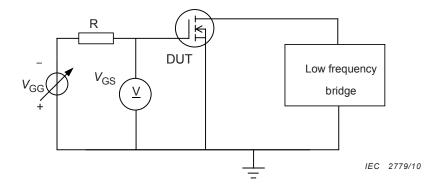

| Figure 29 – Basic for the measurement of short-circuit input capacitance                                                                                 | 55 |

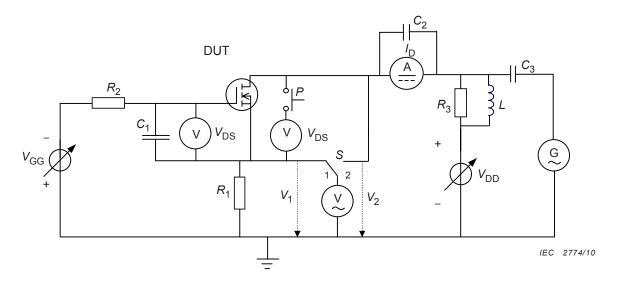

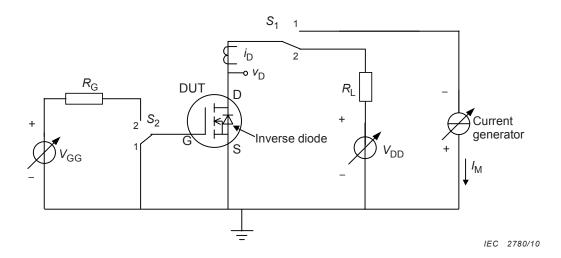

| Figure 30 – Basic circuit for measurement of short-circuit output capacitance $(C_{oss})$                                                                |    |

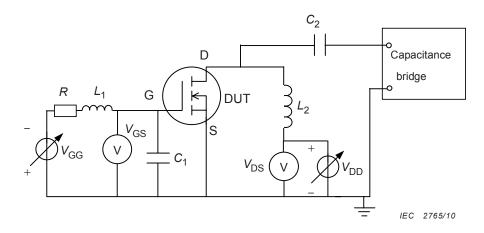

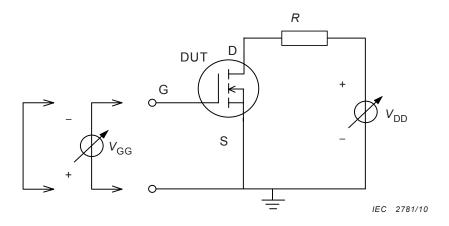

| Figure 31 – Circuit for measurement of reverse transfer capacitance $C_{\rm rss}$                                                                        | 57 |

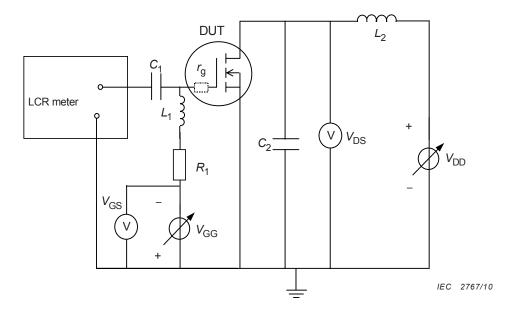

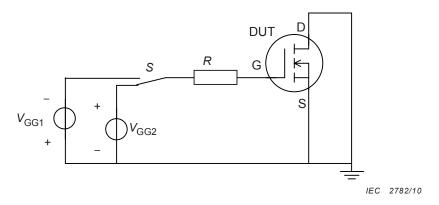

| Figure 32 – Circuit for measurement of internal gate resistance                                                                                          | 58 |

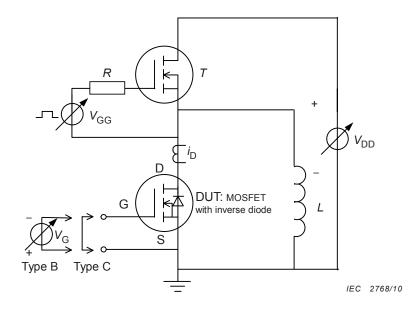

| Figure 33 – Circuit diagram for MOSFET forward recovery time and recovered charge (Method 1)                                                             | 59 |

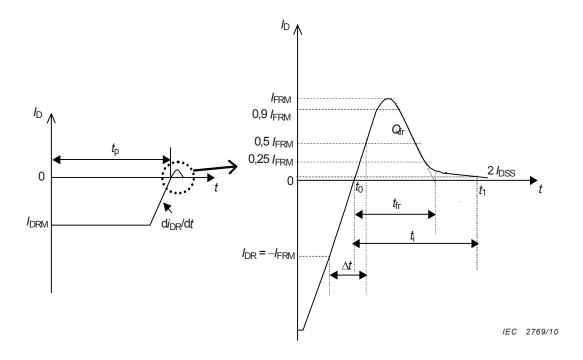

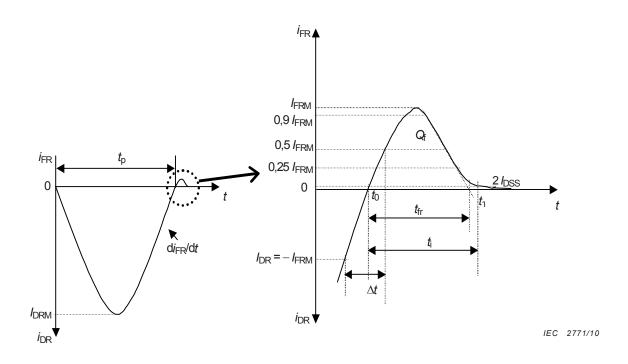

| Figure 34 - Current waveform through MOSFET (Method 1)                                                                                                   | 59 |

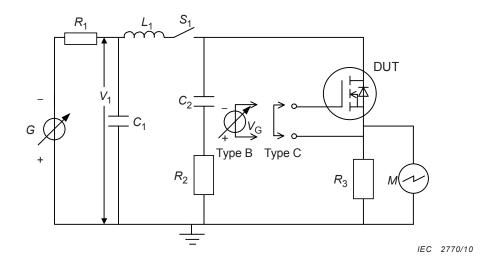

| Figure 35 – Circuit diagram for MOSFET forward recovery time and recovered charge (Method 2)                                                             | 60 |

| Figure 36 - Current waveform through MOSFET (Method 2)                                                                                                   | 61 |

| Figure 37 – Circuit diagram for the measurement of drain-source reverse voltage                                                                          | 62 |

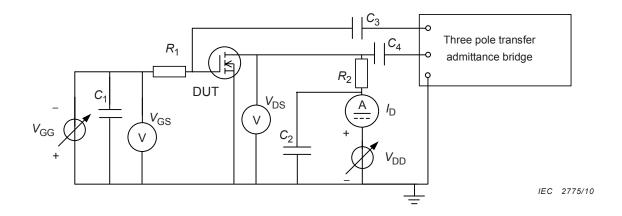

| Figure 38 – Basic circuit for the measurement of the output conductance $g_{\rm oss}$ (method 1: null method)                                            | 63 |

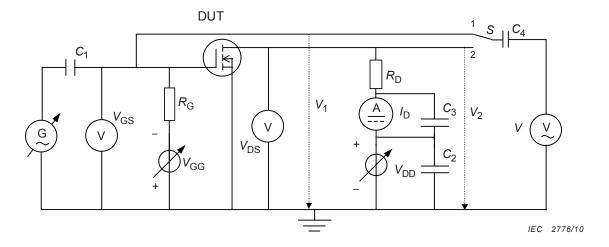

| Figure 39 – Basic circuit for the measurement of the output conductance $g_{\rm oss}$ (method 2: two-voltmeter method)                                   | 64 |

| Figure 40 – Circuit for the measurement of short-circuit forward transconductance $g_{\rm fs}$ (Method 1: Null method)                                   | 65 |

| Figure 41 – Circuit for the measurement of forward transconductance $g_{\rm fs}$ (method 2: two-voltmeter method)                                        | 66 |

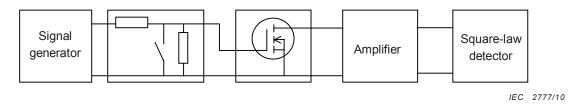

| Figure 42 – Block diagram for the measurement of equivalent input noise voltage                                                                          | 67 |

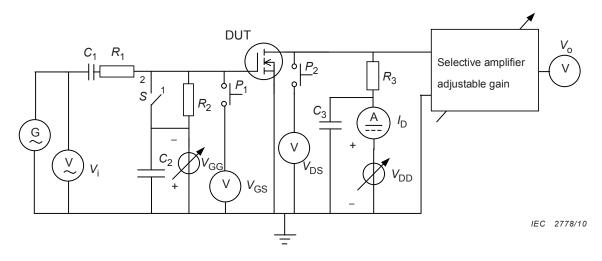

| Figure 43 – Circuit for the measurement of equivalent input noise voltage                                                                                | 67 |

| Figure 44 – Circuit diagram for the measurement of on-state drain-source resistance                                                                      | 68 |

| Figure 45 – Circuit diagram                                                                                                | 69 |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figure 46 – Circuit for high-temperature blockings                                                                         | 72 |

| Figure 47 – Circuit for high-temperature gate bias                                                                         | 72 |

| Figure 48 – Circuit for intermittent operating life                                                                        | 73 |

|                                                                                                                            |    |

| Table 1 – Terms for MOSFET in this standard and the conventional used terms for the inverse diode integrated in the MOSFET | 17 |

| Table 2 – Acceptance defining characteristics                                                                              | 34 |

| Table 3 – Acceptance-defining characteristics for endurance and reliability tests                                          | 71 |

| Table 4 – Minimum type and routine tests for FETs when applicable                                                          | 74 |

#### INTERNATIONAL ELECTROTECHNICAL COMMISSION

# SEMICONDUCTOR DEVICES – DISCRETE DEVICES –

Part 8: Field-effect transistors

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.