# BS EN 62566:2014

# **BSI Standards Publication**

Nuclear power plants — Instrumentation and control important to safety — Development of HDL-programmed integrated circuits for systems performing category A functions

BS EN 62566:2014 BRITISH STANDARD

#### **National foreword**

This British Standard is the UK implementation of EN 62566:2014. It is identical to IEC 62566:2012. It supersedes BS IEC 62566:2012, which is withdrawn.

The UK participation in its preparation was entrusted to Technical Committee NCE/8, Reactor instrumentation.

A list of organizations represented on this committee can be obtained on request to its secretary.

This publication does not purport to include all the necessary provisions of a contract. Users are responsible for its correct application.

© The British Standards Institution 2014. Published by BSI Standards Limited 2014

ISBN 978 0 580 84483 6

ICS 27.120.20

# Compliance with a British Standard cannot confer immunity from legal obligations.

This British Standard was published under the authority of the Standards Policy and Strategy Committee on 31 January 2013.

# Amendments/corrigenda issued since publication

| Date            | Text affected                                   |

|-----------------|-------------------------------------------------|

| 31 October 2014 | This corrigendum renumbers BS IEC 62566:2012 as |

|                 | BS FN 62566:2014 Annex 7A inserted              |

# EUROPEAN STANDARD NORME EUROPÉENNE EUROPÄISCHE NORM

EN 62566

August 2014

ICS 27.120.20

# **English Version**

Nuclear power plants - Instrumentation and control important to safety - Development of HDL-programmed integrated circuits for systems performing category A functions (IEC 62566:2012)

Centrales nucléaires de puissance - Instrumentation et contrôle-commande importants pour la sûreté -Développement des circuits intégrés programmés en HDL pour les systèmes réalisant des fonctions de catégorie A (CEI 62566:2012) Kernkraftwerke - Leittechnik für Systeme mit sicherheitstechnischer Bedeutung - Entwicklung HDLprogrammierter integrierter Schaltkreise für Systeme, die Funktionen der Kategorie A ausführen (IEC 62566:2012)

This European Standard was approved by CENELEC on 2014-08-04. CENELEC members are bound to comply with the CEN/CENELEC Internal Regulations which stipulate the conditions for giving this European Standard the status of a national standard without any alteration.

Up-to-date lists and bibliographical references concerning such national standards may be obtained on application to the CEN-CENELEC Management Centre or to any CENELEC member.

This European Standard exists in three official versions (English, French, German). A version in any other language made by translation under the responsibility of a CENELEC member into its own language and notified to the CEN-CENELEC Management Centre has the same status as the official versions.

CENELEC members are the national electrotechnical committees of Austria, Belgium, Bulgaria, Croatia, Cyprus, the Czech Republic, Denmark, Estonia, Finland, Former Yugoslav Republic of Macedonia, France, Germany, Greece, Hungary, Iceland, Ireland, Italy, Latvia, Lithuania, Luxembourg, Malta, the Netherlands, Norway, Poland, Portugal, Romania, Slovakia, Slovenia, Spain, Sweden, Switzerland, Turkey and the United Kingdom.

European Committee for Electrotechnical Standardization Comité Européen de Normalisation Electrotechnique Europäisches Komitee für Elektrotechnische Normung

CEN-CENELEC Management Centre: Avenue Marnix 17, B-1000 Brussels

# **Foreword**

This document (EN 62566:2014) consists of the text of IEC 62566:2012 prepared by SC 45A "Instrumentation, control and electrical systems of nuclear facilities" of IEC/TC 45 "Nuclear instrumentation".

The following dates are fixed:

- latest date by which this document has to be implemented (dop) 2015-08-04 at national level by publication of an identical national standard or by endorsement

- latest date by which the national standards conflicting (dow) 2017-08-04 with this document have to be withdrawn

As stated in the nuclear safety directive 2009/71/EURATOM, Chapter 1, Article 2, item 2, Member States are not prevented from taking more stringent safety measures in the subject-matter covered by the Directive, in compliance with Community law. In a similar manner, this European standard does not prevent Member States from taking more stringent nuclear safety measures in the subject-matter covered by this standard.

# **Endorsement notice**

The text of the International Standard IEC 62566:2012 was approved by CENELEC as a European Standard without any modification.

# **Annex ZA**

(normative)

# Normative references to international publications with their corresponding European publications

The following documents, in whole or in part, are normatively referenced in this document and are indispensable for its application. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

NOTE 1 When an international publication has been modified by common modifications, indicated by (mod), the relevant EN/HD applies.

NOTE 2 Up-to-date information on the latest versions of the European Standards listed in this annex is available here: <a href="https://www.cenelec.eu">www.cenelec.eu</a>.

| Publication         | <u>Year</u> | <u>Title</u>                                                                                                                                                 | EN/HD    | <u>Year</u> |

|---------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|

| IEC 60671           | -           | Nuclear power plants - Instrumentation and control systems important to safety - Surveillance testing                                                        | EN 60671 | -           |

| IEC 60880           | 2006        | Nuclear power plants - Instrumentation and control systems important to safety - Software aspects for computer-based systems performing category A functions | EN 60880 | 2009        |

| IEC 60987           | 2007        | Nuclear power plants - Instrumentation and control important to safety - Hardware design requirements for computer-based systems                             | EN 60987 | 2009        |

| IEC 61513           | 2011        | Nuclear power plants - Instrumentation and control important to safety - General requirement for systems                                                     | EN 61513 | 2013        |

| IEC 62138           | -           | Nuclear power plants - Instrumentation and control important for safety - Software aspects for computer-based systems performing category B or C functions   | EN 62138 | -           |

| IEC 62340           | -           | Nuclear power plants - Instrumentation and control systems important to safety - Requirements for coping with common cause failure (CCF)                     | EN 62340 | -           |

| IAEA guide NS-G-1.3 | 2002        | Instrumentation and control systems important to safety in nuclear power plants                                                                              | -        | -           |

# CONTENTS

| FO  | REWC  | )RD                                                                         | . 9  |

|-----|-------|-----------------------------------------------------------------------------|------|

| INT | RODU  | JCTION                                                                      | . 11 |

| 1   | Scop  | e and object                                                                | . 14 |

|     | 1.1   | General                                                                     | . 14 |

|     | 1.2   | Use of this Standard                                                        | . 14 |

| 2   | Norm  | ative references                                                            | . 15 |

| 3   | Term  | s and definitions                                                           | . 15 |

| 4   | Symb  | ools and abbreviations                                                      | . 17 |

| 5   | Gene  | eral requirements for HPD projects                                          | . 19 |

|     | 5.1   | General                                                                     | . 19 |

|     | 5.2   | Life-cycle                                                                  | . 19 |

|     | 5.3   | HPD project management                                                      | . 21 |

|     |       | 5.3.1 General                                                               | . 21 |

|     |       | 5.3.2 Additional requirements                                               |      |

|     | 5.4   | HPD quality assurance plan                                                  |      |

|     | 5.5   | Configuration management                                                    |      |

| 6   | HPD   | requirements specification                                                  |      |

|     | 6.1   | General                                                                     | . 22 |

|     | 6.2   | Functional aspects of the requirement specification                         |      |

|     | 6.3   | Deterministic design                                                        |      |

|     | 6.4   | Fault detection and fault tolerance                                         |      |

|     | 6.5   | Requirements capture using Electronic System Level tools                    |      |

|     |       | 6.5.1 General                                                               |      |

|     |       | 6.5.2 Requirements on the formalism of tools used at ESL level              |      |

|     | 6.6   | Requirements analysis and review                                            |      |

| 7   |       | ptance process for programmable integrated circuits, native blocks and pre- | . 24 |

| '   | devel | loped blocks                                                                | . 25 |

|     | 7.1   | General                                                                     |      |

|     | 7.2   | Component requirement specification                                         |      |

|     |       | 7.2.1 General                                                               | . 25 |

|     |       | 7.2.2 Requirements                                                          |      |

|     |       | 7.2.3 Requirements analysis and review                                      | . 25 |

|     | 7.3   | Rules of use                                                                | . 26 |

|     | 7.4   | Selection                                                                   | . 26 |

|     |       | 7.4.1 General                                                               | . 26 |

|     |       | 7.4.2 Documentation review                                                  | . 26 |

|     |       | 7.4.3 Operating experience review                                           |      |

|     |       | 7.4.4 Specific requirements related to the blank integrated circuits        |      |

|     | 7.5   | Acceptance justification                                                    |      |

|     | 7.6   | Modification for acceptance                                                 |      |

|     | 7.7   | Modification after acceptance                                               |      |

| 0   | 7.8   | Acceptance documentation                                                    |      |

| 8   |       | design and implementation                                                   | _    |

|     | 8.1   | General                                                                     |      |

|     | 8.2   | Hardware Description Languages (HDL) and related tools                      | . 28 |

|    | 8.3  | Design   |                                                     | 29 |

|----|------|----------|-----------------------------------------------------|----|

|    |      | 8.3.1    | General                                             | 29 |

|    |      | 8.3.2    | Defensive design                                    | 29 |

|    |      | 8.3.3    | Structure                                           | 29 |

|    |      | 8.3.4    | Language and coding rules                           | 30 |

|    |      | 8.3.5    | Synchronous vs asynchronous design                  | 31 |

|    |      | 8.3.6    | Power management                                    | 31 |

|    |      | 8.3.7    | Initialization                                      | 32 |

|    |      | 8.3.8    | Non-functional configurations                       | 32 |

|    |      | 8.3.9    | Testability                                         | 32 |

|    |      | 8.3.10   | Design documentation                                | 32 |

|    | 8.4  | Implem   | nentation                                           | 33 |

|    |      | 8.4.1    | General                                             | 33 |

|    |      | 8.4.2    | Products                                            | 33 |

|    |      | 8.4.3    | Files of parameters and constraints                 | 33 |

|    |      | 8.4.4    | Post-route analyses                                 |    |

|    |      | 8.4.5    | Redundancies introduced or removed by the tools     | 34 |

|    |      | 8.4.6    | Finite state machines                               | 35 |

|    |      | 8.4.7    | Static timing analysis                              | 35 |

|    |      | 8.4.8    | Implementation documentation                        |    |

|    | 8.5  | System   | n level tools and automated code generation         | 36 |

|    | 8.6  | -        | entation                                            |    |

|    | 8.7  | Design   | and implementation review                           | 37 |

| 9  | HPD  | verifica | tion                                                | 37 |

|    | 9.1  | Genera   | al                                                  | 37 |

|    | 9.2  |          | ation plan                                          |    |

|    | 9.3  |          | ation of the use of the pre-developed items         |    |

|    | 9.4  |          | ation of the design and implementation              |    |

|    | 9.5  | Test-be  | enches                                              | 40 |

|    | 9.6  | Test co  | overage                                             | 40 |

|    | 9.7  | Test ex  | recution                                            | 41 |

|    | 9.8  | Static v | verification                                        | 41 |

| 10 | HPD  | aspects  | of system integration                               | 41 |

|    | 10.1 | Genera   | al                                                  | 41 |

|    |      |          | spects of the system integration plan               |    |

|    |      |          | c aspects of system integration                     |    |

|    |      |          | ation of the integrated system                      |    |

|    |      |          | esolution procedures                                |    |

|    |      |          | spects of the integrated system test report         |    |

| 11 |      |          | of system validation                                |    |

|    |      | •        | al                                                  |    |

|    |      |          | spects of the system validation plan                |    |

|    |      |          | validation                                          |    |

|    |      | -        | spects of the system validation report              |    |

|    |      |          | esolution procedures                                |    |

| 12 |      |          | sociation procedures                                |    |

| -  |      |          | ation of the requirements, design or implementation |    |

|    |      |          | eation of the micro-electronic technology           |    |

|    | 14.4 | widdiiid | addit of the finere diediteme technology            |    |

| 13 F   | HPD production                                                                 | . 45 |

|--------|--------------------------------------------------------------------------------|------|

| 1      | 13.1 General                                                                   | . 45 |

| 1      | 13.2 Production tests                                                          | . 45 |

| 1      | 13.3 Programming files and programming activities                              | . 46 |

| 14 H   | HPD aspects of installation, commissioning and operation                       | . 46 |

| 15 S   | Software tools for the development of HPDs                                     | . 46 |

| 1      | 15.1 General                                                                   | . 46 |

| 1      | 15.2 Additional requirements for design, implementation and simulation tools   | . 46 |

| 16 E   | Design segmentation or partitioning                                            | . 47 |

| 1      | 16.1 Background                                                                | . 47 |

| 1      | 16.2 Auxiliary or support functions                                            | . 47 |

|        | 16.2.1 General                                                                 | . 47 |

|        | 16.2.2 Partitioning of auxiliary or support functions of category other than A | . 47 |

| 17 C   | Defences against HPD Common Cause Failure                                      | . 48 |

| 1      | 17.1 Background                                                                | . 48 |

| 1      | 17.2 Requirements                                                              | . 48 |

| Anne   | x A (informative) Documentation                                                | . 49 |

| Anne   | ex B (informative) Development of HPDs                                         | . 51 |

| Biblio | ography                                                                        | . 56 |

|        |                                                                                |      |

| Figur  | re 1 – System life-cycle (informative, as defined by IEC 61513)                | . 19 |

| Figur  | re 2 – Development life-cycle of HPD                                           | 20   |

# INTERNATIONAL ELECTROTECHNICAL COMMISSION

# NUCLEAR POWER PLANTS – INSTRUMENTATION AND CONTROL IMPORTANT TO SAFETY – DEVELOPMENT OF HDL-PROGRAMMED INTEGRATED CIRCUITS FOR SYSTEMS PERFORMING CATEGORY A FUNCTIONS

#### **FOREWORD**

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-operation on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, Publicly Available Specifications (PAS) and Guides (hereafter referred to as "IEC Publication(s)"). Their preparation is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaising with the IEC also participate in this preparation. IEC collaborates closely with the International Organization for Standardization (ISO) in accordance with conditions determined by agreement between the two organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter

- 5) IEC itself does not provide any attestation of conformity. Independent certification bodies provide conformity assessment services and, in some areas, access to IEC marks of conformity. IEC is not responsible for any services carried out by independent certification bodies.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

International Standard IEC 62566 has been prepared by subcommittee 45A: Instrumentation and control of nuclear facilities, of IEC technical committee 45: Nuclear instrumentation.

The text of this Standard is based on the following documents:

| FDIS         | Report on voting |

|--------------|------------------|

| 45A/859/FDIS | 45A/865/RVD      |

Full information on the voting for the approval of this Standard can be found in the report on voting indicated in the above table.

This publication has been drafted in accordance with the ISO/IEC Directives, Part 2.

The committee has decided that the contents of this publication will remain unchanged until the stability date indicated on the IEC web site under "http://webstore.iec.ch" in the data related to the specific publication. At this date, the publication will be

- · reconfirmed,

- withdrawn,

- · replaced by a revised edition, or

- amended.

# INTRODUCTION

# a) Technical background, main issues and organisation of the Standard

The electronic systems of class 1 (according to IEC 61513) used in Nuclear Power Plants (NPP) which are required in emergency situations, need to be fully validated and qualified before being used in operation.

In traditional systems that are computer-based, a separation can be drawn between the hardware and software portions. The hardware is mainly designed with standardised components having pre-defined electronic functions such as microprocessors, timers or network controllers, whereas software is used to coordinate the different parts of the hardware and to implement the application functions.

Nowadays, I&C designers may build application functions directly in one integrated circuit using devices such as FPGAs or similar technologies. The function of such an integrated circuit is not defined by the supplier of the physical component or micro-electronic technology but by the I&C designer.

The specific integrated circuits addressed by this Standard are:

- 1) based on pre-developed micro-electronic resources,

- 2) developed within an I&C project,

- developed with Hardware Description Languages (HDL) and related tools used to implement the requirements in a proper assembly of the pre-developed micro-electronic resources.

Therefore these circuits are named "HDL-Programmed Devices", (HPD). The HDL statements which describe a HPD can include the instantiation of Pre-Developed Blocks (PDB) which are typically provided as libraries, macros, or Intellectual Property cores.

HPDs can be effective solutions to implement functions required by an I&C project. However, the verification and validation may be limited by issues such as high number of internal paths and limited observability, if the HPD has not been developed with verifiability in mind.

In order to achieve the reliability required for safety I&C systems, the development of HPDs shall comply with strict process and technical requirements such as those provided by this Standard, including the specification of requirements, the selection of blank integrated circuits and PDBs, the design and implementation, the verification, and the procedures for operation and maintenance.

It is intended that this Standard be used by hardware designers, operators of NPPs (utilities), and by regulators. Regulatory bodies will find guidance to assess important aspects such as design, implementation, verification and validation of HPDs.

# b) Situation of the current Standard in the structure of the IEC SC 45A Standard series

IEC 61513 is a first level IEC SC 45A document and gives guidance applicable to I&C at system level. It is supplemented by guidance at hardware level (IEC 60987) and software level (IEC 60880 and IEC 62138). IEC 62340 gives requirements in order to reduce and overcome the possibility of common cause failure of category A functions.

IEC 62566 is a second level IEC SC 45A document which focuses on the activities when HPDs are developed. It complements IEC 60987 which deals with the generic issues of hardware design of computer based systems. It refers to IEC 60880 when issues identical to that of software development are addressed.

For more details on the structure of the IEC SC 45A Standard series, see item d) of this introduction.

# c) Recommendations and limitations regarding the application of the Standard

It is important to note that this Standard establishes no additional functional requirements for safety systems.

Aspects for which special requirements and recommendations have been produced are:

- 1) an approach to specify the requirements of, to design, to implement and to verify "HDL-Programmed Devices" (HPD, 3.7), and to handle the corresponding aspects of system integration and validation;

- 2) an approach to analyse and select the blank integrated circuits, micro-electronic technologies and Pre-Developed Blocks (PDB, 3.11) used to develop HPDs;

- 3) procedures for the modification and configuration control of HPDs;

- 4) requirements for selection and use of software tools used to develop HPDs.

It is recognized that digital technology is continuing to develop at a rapid pace and that it is not possible for a Standard such as this one to include references to all modern design technologies and techniques.

To ensure that the Standard will continue to be relevant in future years the emphasis has been placed on issues of principle, rather than specific technologies. If new techniques are developed then it should be possible to assess the suitability of such techniques by applying the safety principles contained within this Standard.

# d) Description of the structure of the IEC SC 45A Standard series and relationships with other IEC documents and other bodies documents (IAEA, ISO)

The top-level document of the IEC SC 45A Standard series is IEC 61513. It provides general requirements for I&C systems and equipment that are used to perform functions important to safety in NPPs. IEC 61513 structures the IEC SC 45A Standard series.

IEC 61513 refers directly to other IEC SC 45A Standards for general topics related to categorization of functions and classification of systems, qualification, separation of systems, defence against common cause failure, software aspects of computer-based systems, hardware aspects of computer-based systems, and control room design. The Standards referenced directly at this second level should be considered together with IEC 61513 as a consistent document set.

At a third level, IEC SC 45A Standards not directly referenced by IEC 61513 are Standards related to specific equipment, technical methods, or specific activities. Usually these documents, which make reference to second-level documents for general topics, can be used on their own.

A fourth level extending the IEC SC 45 Standard series, corresponds to the Technical Reports which are not normative.

IEC 61513 has adopted a presentation format similar to the basic safety publication IEC 61508 with an overall safety life-cycle framework and a system life-cycle framework and provides an interpretation of the general requirements of IEC 61508-1, IEC 61508-2 and IEC 61508-4, for the nuclear application sector. Compliance with IEC 61513 will facilitate consistency with the requirements of IEC 61508 as they have been interpreted for the nuclear industry. In this framework IEC 60880 and IEC 62138 correspond to IEC 61508-3 for the nuclear application sector.

IEC 61513 refers to ISO as well as to IAEA GS-R-3 and IAEA GS-G-3.1 for topics related to quality assurance.

The IEC SC 45A Standards series consistently implements and details the principles and basic safety aspects provided in the IAEA code on the safety of NPPs and in the IAEA safety series, in particular the Requirements NS-R-1, establishing safety requirements related to the design of Nuclear Power Plants, and the Safety Guide NS-G-1.3 dealing with instrumentation and control systems important to safety in Nuclear Power Plants. The terminology and definitions used by SC 45A Standards are consistent with those used by the IAEA.

# NUCLEAR POWER PLANTS – INSTRUMENTATION AND CONTROL IMPORTANT TO SAFETY – DEVELOPMENT OF HDL-PROGRAMMED INTEGRATED CIRCUITS FOR SYSTEMS PERFORMING CATEGORY A FUNCTIONS

# 1 Scope and object

#### 1.1 General

This International Standard provides requirements for achieving highly reliable "HDL-Programmed Devices" (HPD), for use in I&C systems of nuclear power plants performing functions of safety category A as defined by IEC 61226.

The programming of HPDs relies on Hardware Description Languages (HDL) and related software tools. They are typically based on blank FPGAs or similar micro-electronic technologies. General purpose integrated circuits such as microprocessors are not HPDs.

This Standard provides requirements on:

- a) a dedicated development life-cycle addressing each phase of the development of HPDs, including specification of requirements, design, implementation, verification, integration and validation,

- b) planning and complementary activities such as modification and production,

- c) selection of pre-developed components. This includes micro-electronic resources (such as a blank FPGA or CPLD) and HDL statements representing Pre-Developed Blocks (PDB),

- d) use of simplicity and deterministic principles, recognized to be of primary importance to achieve "fault free" implementation of category A functions,

- e) tools used to design, implement and verify HPDs.

This Standard does not put requirements on the development of the micro-electronic resources, which are usually available as "commercial off-the-shelf" items and are not developed under nuclear quality assurance Standards. It addresses the developments made with these micro-electronic resources in an I&C project with HDLs and related tools.

This Standard provides guidance to avoid as far as possible latent faults remaining in HPDs, and to reduce the susceptibility to single failures as well as to potential Common Cause Failures (CCF). The requirements within this Standard for clear and comprehensive documentation should facilitate the effective application of IEC 62340.

Reliability aspects related to environmental qualification and failures due to ageing or physical degradation are not handled in this Standard. Other Standards, especially IEC 60987, IEC 60780 and IEC 62342, address these topics.

Subclause 5.7 of IEC 60880:2006 provides security requirements that apply to the development of HPDs as applicable.

#### 1.2 Use of this Standard

This Standard provides guidance and requirements to produce verifiable designs and implementations where justification is necessary due for example to the function performed or to the importance to safety of its behaviour. Class 1 I&C systems may use HPDs for which full demonstration of compliance with the requirements of this Standard is not mandatory, e.g.

when they do not implement the logic of a safety function. However, deviations from this Standard should be justified.

This Standard describes the activities to develop HPDs, organized in the framework of a dedicated life-cycle. It also describes activities and guidelines to be used in addition to the requirements of IEC 61513 for system integration and validation when HPDs are included.

Those requirements of IEC 60987 that relate to programmable logic device development are applicable, in addition to those of this Standard, where HPDs are part of class 1 I&C systems.

NOTE In case of conflicting requirements, this Standard supersedes those in IEC 60987 about class 1 HPDs.

#### 2 Normative references

The following documents, in whole or in part, are normatively referenced in this document and are indispensable for its application. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60671, Nuclear power plants – Instrumentation and control systems important to safety – Surveillance testing

IEC 60880:2006, Nuclear power plants – Instrumentation and control systems important to safety – Software aspects for computer-based systems performing category A functions

IEC 60987:2007, Nuclear power plants – Instrumentation and control important to safety – Hardware design requirements for computer-based systems

IEC 61513:2011, Nuclear power plants – Instrumentation and control important to safety – General requirements for systems

IEC 62138, Nuclear power plants – Instrumentation and control important for safety – Software aspects for computer-based systems performing category B or C functions

IEC 62340, Nuclear power plants – Instrumentation and control systems important to safety – Requirements for coping with common cause failure (CCF)

IAEA guide NS-G-1.3:2002, Instrumentation and Control Systems Important to Safety in Nuclear Power Plants

#### 3 Terms and definitions

For the purposes of this document, the following terms and definitions apply.

#### 3.1

#### Application Specific Integrated Circuit, ASIC

integrated circuit designed for specific applications

[IEC 60050-521:2002, 521-11-18]

NOTE Specialized integrated circuit designed for the purpose of one company. It embeds bespoke functions defined by this company.

#### 3.2

# block

one of the parts that make up a design; a block may be subdivided into other blocks

NOTE A block is either a Pre-Developed Block or a Native Block or a block developed during the considered project.

#### 3.3

#### Common Cause Failure, CCF

failure of two or more structures, systems or components due to a single specific event or cause

[IAEA Safety Glossary 2007 Edition]

NOTE Common causes may be internal or external to an I&C system.

[IEC 61513]

#### 3.4

# Electronic System Level, ESL

high-level description of an electronic system, based on a set of processes representing functionalities of components such as microprocessors, memories, specialized computing units, or communication channels

NOTE This description allows the designer to partition the system into components, to assess its performance under different mapping of functions to the components, and to establish the requirements for the components.

It is typically performed with languages such as SystemC (IEEE 1666), SystemVerilog (IEEE 1800), or Matlab (R).

#### 3.5

#### Field Programmable Gate Array, FPGA

integrated circuit that can be programmed in the field by the I&C producer. It includes programmable logic blocks (combinatorial and sequential), programmable interconnections between them and programmable blocks for input and/or outputs. The function is then defined by the I&C designer, not by the integrated circuit supplier.

NOTE While FPGAs are essentially digital devices, some of them may integrate analog input/outputs and analog to digital converters. FPGAs may include advanced digital functions such as hardware multipliers, dedicated memory and embedded processor cores.

#### 3.6

#### Hardware Description Language, HDL

language used to formally describe the functions and/or the structure of an electronic component for documentation, simulation or synthesis

NOTE The most widely used HDLs are VHDL (IEEE 1076) and Verilog (IEEE 1364).

# 3.7

#### **HDL-Programmed Device, HPD**

integrated circuit configured (for NPP I&C systems), with Hardware Description Languages and related software tools

NOTE 1 HDLs and related tools (e.g. simulator, synthesizer) are used to implement the requirements in a proper assembly of pre-developed micro-electronic resources.

NOTE 2 The development of HPDs can use Pre-Developed Blocks.

NOTE 3 HPDs are typically based on blank FPGAs, PLDs or similar micro-electronic technologies.

#### 3.8

#### module

one of the parts that make up a design; a module may be subdivided into other modules

NOTE Module" is a synonym of "Block"; "Block" is often used in the context of electronic design. "Module" is the term used by IEC 60880 and is needed in this Standard for references to IEC 60880.

#### 3.9

#### native block

a Block which represents a pre-existing resource in the integrated circuit, e.g. an OR gate or a more complex block such as a multiplier or a serial transmission controller. By programming the HPD, the Native Blocks are configured and connected to provide the required function.

#### 3.10

#### netlist

description of an electronic component in terms of interconnections between its terminal elements (e.g. Native Blocks)

#### 3 11

#### Pre-Developed Block, PDB

pre-developed functional block usable in a HDL description

NOTE 1 PDBs are typically provided as libraries, macros, or Intellectual Property cores. They are used in the development of a HPD and incorporated in this HPD.

NOTE 2 A PDB may need significant work before incorporation in a HPD, e.g. synthesizing an electronic circuit from the HDL statements, mapping the notional components of this circuit on the hardware structures of the physical integrated circuit and routing the interconnections.

#### 3.12

#### Pre-Developed Software, PDS

software part that already exists, is available as a commercial or proprietary product, and is being considered for use

[IEC 60880]

#### 3.13

#### Programmable Logic Device, PLD

integrated circuit that consists of logic elements with an interconnection pattern, parts of which are user programmable.

[IEC 60050-521:2002, 521-11-01]

NOTE 1 Different kinds of PLD exist, e.g. Erasable PLD or Complex PLD (CPLD).

NOTE 2 The differences between "FPGA" and "PLD" are not well defined, but "PLD" usually refers to a simpler device than "FPGA".

# 3.14

# Register Transfer Level, RTL

synchronous parallel model of an electronic circuit, describing its behaviour by means of signals processed according to a combinatorial logic and transferred between registers on clock pulses. The RTL model is typically written in HDL or generated out of HDL source code.

# 4 Symbols and abbreviations

ASIC: Application Specific Integrated Circuit

CCF: Common Cause Failure

CPLD: Complex Programmable Logic Device

DRC: Design Rule Check

ESL: Electronic System Level

FPGA: Field Programmable Gate Array

HDL: Hardware Description Language

HPD: HDL-Programmed Device

IP: Intellectual Property

I&C: Instrumentation and ControlPAL: Programmable Array Logic

PDB: Pre-Developed Block

PDS: Pre-Developed Software

PLD: Programmable Logic Device

RAM: Random Access Memory

RTL: Register Transfer Level

SEU: Single Event Upset

SRAM: Static RAM

STA: Static Timing Analysis

VHDL: Very High Speed Integrated Circuit Hardware Description Language

V&V: Verification and Validation

# 5 General requirements for HPD projects

#### 5.1 General

This clause first locates the HPD within the I&C system described by IEC 61513. Then it describes the HPD development life-cycle which structures the HPD project.

Finally it provides requirements for HPD projects, for quality assurance and for configuration management. As these issues are common with those of software development processes, the requirements are defined by reference to relevant sections of IEC 60880, supplemented by HPD specific requirements if needed.

With reference to Clause 1, the scope of this Standard excludes the development of microelectronic technologies or blank integrated circuits. Therefore wordings such as "HPD development", "HPD life-cycle", "HPD design" or "HPD verification" refer to what is done within the I&C project, starting from these technologies or these blank integrated circuits, to produce the specific integrated circuit for use in the I&C system.

# 5.2 Life-cycle

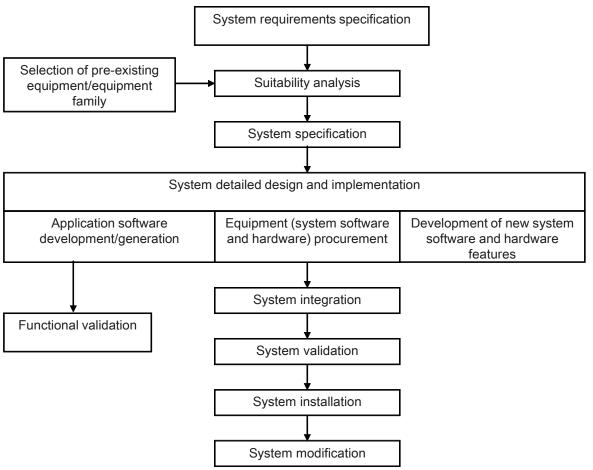

The process of producing I&C systems for use in nuclear power plants is given in IEC 61513 that introduces the concept of system life-cycle. This is a vehicle by which the development process can be controlled and whose adoption should also result in the evidence necessary to justify the correct operation of safety systems. It includes and places requirements on, but does not dictate the project arrangements to be used for, production of systems (see Figure 1).

IEC 82/12

Figure 1 - System life-cycle (informative, as defined by IEC 61513)

The system life-cycle of IEC 61513 is complemented in IEC 60880 (for category A functions) and IEC 62138 (for category B and C functions) for software development and in IEC 60987 for hardware development of computer-based systems. The requirements of this Standard apply to the development of HPDs in class 1 systems, in addition to the requirements of IEC 60987.

NOTE In case of conflicting requirements, this Standard supersedes those in IEC 60987 about class 1 HPDs.

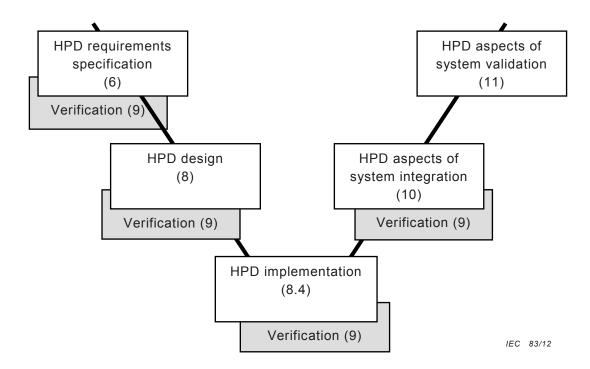

HPDs are developed by means of computer tools which tend to structure the development according to a cycle that includes activities dedicated to requirement capture, design and implementation, integration and validation, together with verification and test activities.

The system design and implementation phases of IEC 61513 shown in Figure 1 (particularly the "Equipment (system software and hardware) procurement" and "Development of new system software and hardware features") are essential parts of the system life-cycle of IEC 61513. These phases are expanded in Figure 2 to illustrate in more detail the phases between the specification of requirements and the validation for the system components which are HPDs.

Figure 2 - Development life-cycle of HPD

Designers generally use pre-developed items such as programmable blank integrated circuits or Pre-Developed Blocks (PDB) to build integrated circuits specifically tailored to the needs of the project. The activities dedicated to the selection of these pre-developed items are addressed in Clause 7; they may be performed in parallel with the first phases of the life-cycle described in Figure 2, provided all dependencies are formally managed and documented.

The life-cycle described in Figure 2 shows the development life-cycle of one HPD that may be undertaken in parallel with the development of other components (software or hardware) of the system as shown in Figure 1, but coming together at the integration and validation phases of the system life-cycle.

The approach proposed to development is based on the traditional "V cycle" model as this approach has been reflected in other Standards and is also recommended in IAEA NS-G 1.3, but allowing necessary adjustments recognizing that some phases of the development can be done automatically by tools and that development may be iterative.

There is often no clear separation and well-identified boundary between the integration of a given component and the system integration. Therefore, in this Standard, the integration of a HPD is considered to be part of the system integration. Similarly, the validation of the HPD is considered to be part of the system validation.

Depending on the function achieved by the HPD, the system or subsystem to consider during integration may range:

- 1) from the I&C system when the HPD implements a safety function logic,

- 2) to an electronic board or cabinet when it implements a function (internal to the board or cabinet) that has been demonstrated, by suitable analysis, to be incapable of affecting the outputs of any safety function in the wider system.

The situation usually most critical from a safety standpoint is when the HPD directly implements the safety function logic.

The following activities support the development process of HPDs:

a) project management (5.3),

- b) quality assurance and quality control (5.4),

- c) configuration management (5.5),

- d) verification (Clause 9).

There are also activities involving selection of tools to support the development (Clause 15), the production of documentation (Annex A) and modification (Clause 12).

# 5.3 HPD project management

#### 5.3.1 General

- **5.3.1.1** Each HPD shall be developed within a dedicated HPD project.

- **5.3.1.2** The HPD project shall comply with the requirements of 5.4 of IEC 60880:2006 (by replacing "software" with "HPD").

- NOTE 1 A typical list of the documents required through the life-cycle is given in Annex A of this Standard.

- NOTE 2 The documented inputs addressed by 5.4.6 of IEC 60880:2006 include parameters for the automated activities of the software tools (e.g.: optimize timing, optimize density, etc.).

- 5.3.1.3 The development process may be iterative; a phase may start before the activities of the preceding phase are complete; however, a phase shall only be terminated if the preceding phases have been completed and if its outputs are consistent with the inputs provided by these preceding activities.

- **5.3.1.4** The phases of the HPD project shall include the specification of requirements, the design and the implementation of the HPD.

#### 5.3.2 Additional requirements

- **5.3.2.1** The selection of the pre-developed items used by the project shall be performed according to the requirements of Clause 7 of this Standard.

- **5.3.2.2** Transition criteria between phases shall be defined.

- **5.3.2.3** The criteria for phase termination shall have methodological and technical content, involving enough detail such that their evaluation requires an in-depth analysis of the phase outputs.

- **5.3.2.4** The documentation (5.4.11 of IEC 60880:2006) shall include the description of the functions performed by the HPD and its interface.

# 5.4 HPD quality assurance plan

A quality assurance plan for the HPD shall exist and shall comply with the requirements of 5.5 of IEC 60880:2006 (by replacing "software" with "HPD").

NOTE In this context, "language" means "computer language".

# 5.5 Configuration management

**5.5.1** Configuration management of the HPD shall be performed according to the requirements of 5.6 of IEC 60880:2006 (by replacing "software" with "HPD").

NOTE The segregation required by 5.6.6 of IEC 60880:2006 applies to the documentation and computer files used or produced by the HPD project.

- **5.5.2** The configuration management shall record the following items:

- a) documentation of modules (blocks) developed within the project and of PDBs,

- b) identification marking of integrated circuits,

- c) computer files used for simulation, verification and production,

- d) parameters used for the automated activities of the software tools (see Clause 15), such as "optimize timing, optimize density" for the Place and Route activity,

- e) identification of the versions of all software tools (see Clause 15), including any "software patch" applied, as well as general purpose libraries and technology dependent libraries.

# 6 HPD requirements specification

#### 6.1 General

- **6.1.1** A requirement specification shall document the requirements of the HPD, either in the document itself or by referencing sets of requirements stated at system or subsystem level (e.g. the functional behaviour to be implemented).

- 6.1.2 The requirement specification shall be understandable for all participants, including hardware engineers and people mentioned in 6.6.

- **6.1.3** The requirements specification shall be unequivocal, verifiable and achievable, including for temporal aspects.

- 6.1.4 When the HPD implements a safety function, its requirement specification shall be derived from the requirements of the I&C system implementing this safety function and shall be part of the specification of the subsystem which uses the HPD.

- **6.1.5** The requirement specification shall describe what is to be done and not how it is to be done.

- **6.1.6** A documented, formal and auditable process shall be defined and implemented for the establishment of the requirements specification.

- 6.1.7 The requirement specification shall be such that compliance with the requirement specification of the I&C system can be verified. If the HPD is used by a subsystem of the I&C system, it shall also be possible to verify the compliance with the system design specifications.

- 6.1.8 The requirement specification shall consider all plant operating conditions down to the HPD level for the functions that are impacted.

- 6.1.9 Interface requirements with other systems or components shall be addressed according to IEC 61513.

- **6.1.10** Interface requirements with other systems or components shall be documented.

- **6.1.11** When they are not part of the HPD requirements but result from HPD design decisions, the following interface requirements shall be documented:

- a) electrical and temporal performance (e.g. input load, setup and hold time of inputs, operating frequency, fan-out, propagation time from any input to the associated outputs),

- b) profiles of interfaced signal and power supplies,

- c) power dissipation, operating temperature and cooling requirements.

#### 6.2 Functional aspects of the requirement specification

This subclause describes the content of the requirements specification directly related to the functional needs. Subclauses 6.3 and 6.4 address additional aspects to be included in the Requirements Specification.

The requirement specification shall specify:

- a) the functions to be provided by the HPD,

- b) the HPD's different modes, and the corresponding conditions of transition, including power-on and initialization,

- c) the HPD's interfaces and interactions with its environment (operators and other I&C components), including the roles, protocols, types, data formats, bit numbering, ranges and constraints of inputs and outputs,

- d) any HPD parameters which can be modified manually during operation, and their roles,

- e) the HPD's performance, in particular response time,

- f) what the HPD must not do or must avoid, when appropriate,

- g) any assumptions regarding the HPD's environment (e.g. electrical and temporal characteristics of inputs-outputs, power supplies, specific profiles during power-on, cooling).

# 6.3 Deterministic design

The requirement specification shall specify that the function of the HPD is deterministic by design. This means that any given input sequence fulfilling the electrical and temporal specification always produces the same outputs.

NOTE Modern FPGA and other integrated circuits covered by this Standard can contain analogue functional blocks (e.g. analogue to digital converter) that are subject to electronic noise, digitisation error, etc. Variations in the response of these analogue functional blocks due to these causes, as well as their impacts on the response of the HPD, are not breaches in the deterministic design.

#### 6.4 Fault detection and fault tolerance

The requirements of IEC 60987 subclauses 5.3 and 5.4 addressing the reliability with respect to random failures and the environmental withstand apply. This includes the faults due to SEU (single event upset) and neutron/alpha radiation when relevant.

Defensive design is typically based on a combination of techniques (e.g. redundancy, vote, parity and cyclic redundancy checks, watch-dog, range and plausibility checks).

- **6.4.1** The requirement specification shall specify requirements for defensive design to address fault detection and fault tolerance.

- 6.4.2 The benefit from defensive design measures should be balanced with their induced additional complexity. The overall objective is to take into account the testability of the HPD during design and implementation, using internal and external detection means to achieve high fault coverage.

- 6.4.3 The requirement specification shall describe the provisions to detect HPD malfunctions, taking into account the provisions already taken at subsystem or system level.

- 6.4.4 These provisions may need the HPD to provide additional outputs, either to be used by an external mechanism such as a watch-dog or to achieve the coverage of the supervision made by an external testing device.

- 6.4.5 The defensive design should allow the detection of erroneous behaviour (such as data corruption or deviation from specified processing algorithm, or deviation from specified operating conditions), erroneous data transmission between processing units, unintended modification of memories or configuration data.

- 6.4.6 The defensive design shall not have adverse influence on the I&C system functions, nor prevent the HPD from meeting its response time specification.

- 6.4.7 The requirement specification shall describe the expected logical and temporal behaviour (such as output values and specific information issued) when a fault is detected.

- 6.4.8 This behaviour shall comply with the system behaviour required by the system specification and with IEC 61513 system design requirements.

**6.4.9** The requirement specification shall specify and justify the target coverage of the fault detection to be achieved by defensive design.

# 6.5 Requirements capture using Electronic System Level tools

#### 6.5.1 General

This Standard does not prescribe a specific method to capture the HPD requirements. If they are captured using tools at Electronic System Level (ESL, see Clause B.1), then the requirements of 6.5.2 and 6.5.3 apply to these tools and to their use.

In the case of ESL, as the requirements specification language may be similar to implementation languages, it may be less practical to fulfil 6.1.5. (separation between what has to be done (the requirement) and how it is done (the design)). Provisions may be needed to fulfil it, e.g. comments to specify inputs, outputs and algorithms.

# 6.5.2 Requirements on the formalism of tools used at ESL level

- **6.5.2.1** When the HPD requirements are captured using an ESL tool:

- a) this tool shall offer a formalism with a rigorous semantics and clarity (standardization of structure and presentation, modularity, sound comments);

- b) the formalism used in the ESL tool shall be understandable for all participants;

- c) if the tool offers flexible mechanisms to redefine functions and operators, then the actual characteristics of any given element should be clear to any participant, including hardware engineers and other personnel mentioned in 6.6.

- 6.5.2.2 The languages used at ESL level should allow taking due account of the system architecture, e.g. enable the assignment of functions to components, and support any fault tolerant design features.

#### 6.5.3 Interface with design tools

The semantics of the languages used to express the requirement specification at ESL level may differ from the semantics of the HDL languages used during design. Examples where discrepancies may occur are in the interpretation of parallelism, the management of overflows, or the encoding of types and finite state machines.

- a) If the semantics of the language used to express the requirement specification at ESL level differs from the semantics of the other languages used in the project, then discrepancies shall be identified for each involved item of the requirement specification;

- b) each occurrence of a discrepancy within the requirement specification shall be documented. A generic list of discrepancies between the involved languages is a useful reference, but is not enough to clarify the Requirement Specification.

# 6.6 Requirements analysis and review

- **6.6.1** A critical analysis of the requirements shall be performed and documented, in order to find potential inconsistencies, omissions and ambiguities.

- 6.6.2 The scope of this analysis shall cover functional requirements and all other types of requirements, including those addressing abnormal behaviour such as unexpected input values or sequences.

- 6.6.3 The requirement specification shall be reviewed to check its completeness and its consistency.

- 6.6.4 For safety functions implemented in the HPD, process and I&C engineers shall participate in the review, as well as specialists of subsystems or components (including software) interfaced to the HPD.

# 7 Acceptance process for programmable integrated circuits, native blocks and pre-developed blocks

#### 7.1 General

When developing the HPD, it is necessary to select and assess pre-developed items such as a blank integrated circuit (including their native blocks) or PDBs incorporated in the final HPD.

As these pre-developed items (or components) may include features not required for the HPD, the elaboration and the enforcement of specific "rules of use" may be recommended in order to restrict their use to what is needed and safe.

## 7.2 Component requirement specification

#### 7.2.1 General

The requirements assigned to the pre-developed items (or components) result from the initial design activities of the HPD. For example the HPD requirements could include a specific pass-band filter, which the designer could implement using a PDB performing a Fast Fourier Transform.

Thus the component requirement specification (here for a Fast Fourier Transform PDB, defined by characteristics such as type of algorithm, radix size, decimation method, silicon area needed, etc.) differs from the HPD requirement specification (here for a Pass-band filter, defined by characteristics such as corner frequencies, gain, slopes, etc.).

- **7.2.1.1** A component requirement specification shall document the requirements applicable to each pre-developed item: blank integrated circuit, micro-electronic resources (seen as native blocks), associated tools when relevant or PDBs.

- **7.2.1.2** The component requirement specification shall state all the requirements, either in the document itself or by referencing sets of requirements stated at system or subsystem level (e.g. functional behaviour to be implemented).

- **7.2.1.3** Being the basis of the selection and use of the pre-developed item, the component requirement specification shall thus be understandable by all participants, including hardware and software designers when relevant, as well as verifiers, reviewers, and regulators.

- **7.2.1.4** The component requirement specification shall be unequivocal, verifiable and achievable, including for temporal aspects.

- 7.2.1.5 The component requirement specification shall be such that compliance with the requirements of IEC 61513 of the I&C system using this component can be demonstrated.

# 7.2.2 Requirements

The component requirement specification shall specify all characteristics required from the pre-developed item, in particular those of the list provided in 6.2.

NOTE The generic names of the characteristics (e.g. "function") are identical to those of 6.2, but the contents differ in general as explained in 7.2.

# 7.2.3 Requirements analysis and review

**7.2.3.1** A critical analysis of the component requirement specification shall be performed and documented, in order to find potential inconsistencies, lack of completeness or ambiguities.

- **7.2.3.2** The scope of this analysis shall cover functional requirements and all other types of requirements, including those addressing non-nominal behaviour such as unexpected input values or sequences.

- **7.2.3.3** The component requirement specification shall be formally reviewed by experts of all relevant domains to check its completeness and its consistency.

#### 7.3 Rules of use

**7.3.1** If the pre-developed item includes functions or operating modes that are not required to be implemented in the HPD, rules should be defined to prohibit the use of such functions and modes.

The use of functions or modes that are required to implement the HPD may be constrained by rules in order to improve design properties such as safety or testability.

- **7.3.2** If rules of use are established:

- a) they shall be documented,

- b) the quality plan shall give assurance that their fulfilment is verified during the project.

#### 7.4 Selection

#### 7.4.1 General

- **7.4.1.1** A documented analysis of each pre-developed item used in the HPD shall demonstrate that it fulfils the requirements of its component requirement specification, possibly with rules of use and modifications (see 7.6).

- **7.4.1.2** A user documentation for safety shall detail how designers are to use the predeveloped item consistently with its specification and design characteristics.

#### 7.4.2 Documentation review

Documentation review is the primary method to demonstrate that the pre-developed item fulfils the component requirement specification.

- **7.4.2.1** This review should be based on the documentation of the pre-developed item including documentation of its design and its verification.

- 7.4.2.2 The documentation shall contain sufficient detail in order to demonstrate the fulfilment of the functional, electrical and temporal requirements of the predeveloped item.

- **7.4.2.3** The analysis of the documentation shall demonstrate that any functions and modes of the pre-developed item not used within the HPD do not impede the used ones.

# 7.4.3 Operating experience review

The operating experience of the pre-developed item may be invoked to compensate for some limited documentation weaknesses regarding its reliability or its design. If the operating experience is invoked then:

- a) the analysis of the operating experience shall demonstrate that:

- 1) its volume is commensurate to the reliability requirements,

- 2) it has been collected in operating conditions equivalent to those in which the predeveloped item will be used,

- 3) the actual use of the pre-developed item has been traced at the level of detail generally required by this Standard for the documentation;

- b) the means and procedures used to collect the operating experience shall ensure that any pre-developed item failure that occurred in the analysed operation is recorded in such detail that a technical analysis can identify its cause as far as possible;

- c) it shall be demonstrated by analysis of the failures recorded during operation that they do not impact the functions or the safety of the HPD;

- d) the operating experience –and, if needed, complementary tests- shall demonstrate that the pre-developed item fulfils its requirements;

- e) a documented technical analysis shall justify that all interactions of the pre-developed item with its environment are included within those covered by the operating experience;

- f) the operating experience taken into consideration shall correspond to precisely identified versions of the pre-developed item and, when this item is specific to equipment, of the equipment in which it operates;

- g) the operating experience should address the specific version of the pre-developed item or its sub-part used in the HPD; otherwise the differences between versions shall be analysed to demonstrate that the operating experience is relevant for the intended version.

# 7.4.4 Specific requirements related to the blank integrated circuits

#### **7.4.4.1** The following aspect shall be addressed:

- a) analysis of the adequacy of the programming mechanisms and circuitry;

- b) demonstration that the programming process is fault-free or that any fault in this process is detected and correctly managed;

- c) demonstration that the integrated circuit retains its programmed configuration for an adequate duration;

- d) analysis of the potential for faults due to the additional internal and external mechanisms or power transients and justification according to the reliability requirements.

# **7.4.4.2** A detailed analysis shall demonstrate that:

- a) the integrated circuit will be able to fulfil its component requirement specification,

- b) the associated tools

- comply with Clause 15, and

- allow all verifications required by Clauses 8 and 9 (such as Static Timing Analysis).

- **7.4.4.3** The data needed to calculate the fault rate (in the sense of random physical faults) shall be available and based on sufficient operating experience.

- **7.4.4.4** The designers who design or implement the HPD shall have appropriate knowledge:

- a) of the blank integrated circuit, including programming particularities, configuration and testing modes, protocols, pins and registers, and any electrical or logical specificity, and

- b) of the associated tools, native blocks and PDBs. In particular, they should be able to predict, understand and (where necessary) control the choices made by the tools during synthesis, place and route.

#### 7.5 Acceptance justification

- **7.5.1** A formal review shall examine the pre-developed item analysis, including the rules of use and the arrangements taken to ensure the compliance of each physical part used in production, to decide whether or not the pre-developed item is accepted for use in the HPD.

- **7.5.2** If the pre-developed item is accepted, any arrangement and rule of use taken into account in the analysis shall be applicable during the whole HPD life-cycle.

7.5.3 The review team shall include experts having skills relevant to the subjects (e.g. hardware technology, software) and engineers from the teams responsible for the components that are interfaced to the pre-developed item.

#### 7.6 Modification for acceptance

- **7.6.1** If modifications of the pre-developed item are necessary to achieve acceptance, they shall be specified, designed, implemented and verified before the review.

- 7.6.2 These modifications shall be performed and documented in accordance with the requirements of this Standard regarding project structure and management, quality, specification of requirements, design, implementation and verification.

#### 7.7 Modification after acceptance

The acceptance activities, including the review, shall be performed again after any modification of the pre-developed item involving its design or its micro-electronic aspects.

# 7.8 Acceptance documentation

The acceptance documentation of the pre-developed item shall be under configuration management.

- **7.8.1** The documentation shall include or shall make a reference to:

- a) the requirement specification of the HPD,

- b) all documents issued or invoked during the analysis of the pre-developed item,

- c) all documents issued during modification of the pre-developed item,

- d) the review report.

The documentation shall include any information necessary to use the pre-developed item correctly, taking into account constraints from its initial specification, from the rules of use, and from the modifications.

# 8 HPD design and implementation

#### 8.1 General

This clause provides requirements and recommendations based on good practice for design and implementation, in order to meet appropriate safety features such as fault-free as possible and amenability to verification.

**8.1.1** The development process shall define a design phase and an implementation phase.

# 8.2 Hardware Description Languages (HDL) and related tools

Even though the use of specific languages and tools cannot be required, the following may be considered as common basic rules for languages and tools used for the design and implementation of HPDs for class 1 systems.

8.2.1 Design and implementation should use Hardware Description Languages (HDL) and tools for simulation, synthesis, place and route.

NOTE When properly chosen and used, these tools improve essential aspects such as understandability of the descriptions, management of electrical and temporal constraints, verification, adequateness of coverage criteria, and documentation.

- **8.2.2** Even if 8.2.1 is not fulfilled, any documentation, analysis, or verification required by this Standard shall be provided.

- **8.2.3** The language in use:

- a) shall follow strict (or well-defined) semantic and syntax rules;

- b) shall have a syntax completely and clearly defined and documented;

- c) should comply with a recognized Standard (e.g. IEEE 1076 for VHDL or IEEE 1364 for Verilog).

- 8.2.4 The use of the language should be restricted to a "safe" subset where appropriate, for example be restricted to features that are needed to implement the required functions and are synthesisable with standardized libraries (e.g. avoid the use of initial values, explicit delays or division).

- **8.2.5** The simulator in use shall produce results strictly compliant with the documented semantic of the language.

The simulator should comply with a recognized Standard (e.g. IEEE 1076 for VHDL or IEEE 1364 for Verilog).

- **8.2.6** Except as addressed in 8.2.7, only tools complying with the requirements of Clause 15 shall be used for analysis, simulation, synthesis, place and route. It is not necessary for users to repeat testing of the tools if this has already been performed and documented by the supplier.

- 8.2.7 If a tool partially compliant with the requirements of Clause 15 is used, additional verification of the results produced by this tool (e.g. netlist produced by a synthesis tool) shall provide evidence that the results are correct. Formal equivalence checking tools are valuable in achieving an error free design.

#### 8.3 Design

#### 8.3.1 General

Starting from the HPD requirement specification, the design initially aims at defining major choices such as the decomposition into modules (application-specific or pre-developed), the operation of the defensive design, as well as the identification of needed micro-electronic technologies (including their native blocks) and PDBs. Then an RTL description is built using HDLs. The following requirements aim at producing a clear and verifiable design.

- **8.3.1.1** The design phase shall produce a) a formalized description of the HPD, e.g. RTL and b) the associated documentation.

- **8.3.1.2** Communication links shall be designed in compliance with the requirements on data communication given in 5.4.2.4 of IEC 61513.

- **8.3.1.3** The design should allow easy verification.

- **8.3.1.4** Non-compliances with design rules should be justified.

#### 8.3.2 Defensive design

- **8.3.2.1** When a selected native block or PDB (see Clause 7) is a processor core, it should support the requirements of IEC 60880 for self-supervision.

- 8.3.2.2 The design shall take into account the arrangements selected in the requirement specification to detect the faults and to elaborate the corresponding information within the HPD.

- **8.3.2.3** On fault detection, the HPD shall behave in accordance with the corresponding specified requirements.

## 8.3.3 Structure

**8.3.3.1** A top down approach to design should be preferred to a bottom up approach.

NOTE Library items are the ultimate targets of the design. Therefore the use of libraries fulfilling the requirements of Clauses 7 and 15 is in line with the top-down approach and is recommended.

- **8.3.3.2** The structure of the design should be based on decomposition into modules. Related modules may be contained in a library.

- **8.3.3.3** Generic modules should be contained in libraries.

- **8.3.3.4** The structure should be simple and easy to understand, both in its overall design and in its details.

- **8.3.3.5** A conceptual model of the architecture should be generated at the beginning of the project.

# 8.3.4 Language and coding rules

- 8.3.4.1 In order to facilitate a stable and reliable design, proven design methodology and general good practice should be used.

- 8.3.4.2 In order to make the design more understandable and to reduce the potential for differences between the simulated and the synthesized behaviours:

- a) a set of strict design rules which reflect the latest knowledge in terms of design safety and reliability shall be required by the quality plan and established;

- b) the compliance with those design rules shall be enforced by appropriate means (e.g. review, tooling, etc.).

- 8.3.4.3 The list given below contains strongly recommended design considerations and techniques. However the list is not considered to be all-encompassing and parts may change with technology. Nevertheless any non-compliance with the rules in the following list shall be justified and taken into account in failure analysis:

- a) only synthesizable features of the language should be used in the design of the HPD. The test and simulation environment (9.5) may use all language features. Any native blocks (see 3.9) which are already synthesized and routed in the pre-developed integrated circuit may be instantiated as they are, if they comply with Clause 7;

- b) dedicated resources or design features (e.g. predefined clock trees and clock conditioning circuits, power rails, reset trees, etc.) should be used where appropriate;

- c) coding rules should cover all relevant aspects, in particular naming of modules and signals, use of the structuring features (such as packages, functions, procedures, project libraries, instantiation), organization of the computations on critical paths, organization of processes, recommended constructs, forbidden constructs;

- d) functions using side effects ("impure") should be forbidden in the design description. (Rationale: such a function can return different values when called several times with the same parameters. It is therefore very difficult to test and verify, as it breaks the basic concept of a function, and in fact of determinism);

- NOTE 1 An impure function may also have side effects such as modifying objects out of their scope.

- e) constructs that could lead to differences between simulated and synthesized behaviours should be forbidden. Depending on the language used, examples of such constructs may be the incomplete or conflicting assignments, use of "don't care" character in comparisons, comparisons (higher or lower) involving enumerated types (Rationale: simulation is an important verification method. If simulated and synthesized behaviours differ, then the verification chain is broken);

- f) signals and variables should not be initialized at their declaration in the RTL description, but by an explicit mechanism such as reset (Rationale: initialization in HDL may lead to differences between simulated and synthesized behaviours);

- g) use of explicit delays should be forbidden in the design description, as such delays lead to differences between simulated and synthesized behaviours;

- NOTE 2 This does not forbid the existence of delays at system level or in the requirements of the HPD. It means that such delays cannot be implemented by a "delay" or "after" instruction in HDL, but e.g. by counters or shift registers.

- h) creation of delays by means of combinatorial gates or by depending upon propagation delays along wires should be forbidden in the design description. If such design cannot be avoided, STA shall be done to justify the usage of such design (Rationale: such delays are not stable over parameters such as temperature, voltage, or from one part to another, or from one area of the die to another);

- the types of the interface signals of the HPD should be defined in a clear and nonambiguous way, preferably standardized, independently of any tool or micro-electronic technology;