### BS EN 61508-2:2010

### **BSI Standards Publication**

# Functional safety of electrical/ electronic/programmable electronic safety-related systems

Part 2: Requirements for electrical/electronic/ programmable electronic safety-related systems

NO COPYING WITHOUT BSI PERMISSION EXCEPT AS PERMITTED BY COPYRIGHT LAW

BS EN 61508-2:2010 BRITISH STANDARD

#### National foreword

This British Standard is the UK implementation of EN 61508-2:2010. It is identical to IEC 61508-2:2010. It supersedes BS EN 61508-2:2002 which is withdrawn.

The UK participation in its preparation was entrusted by Technical Committee GEL/65, Measurement and control, to Subcommittee GEL/65/1, System considerations.

A list of organizations represented on this committee can be obtained on request to its secretary.

This publication does not purport to include all the necessary provisions of a contract. Users are responsible for its correct application.

© BSI 2010

ISBN 978 0 580 56234 1

ICS 13.260; 25.040.40; 29.020

Compliance with a British Standard cannot confer immunity from legal obligations.

This British Standard was published under the authority of the Standards Policy and Strategy Committee on 30 June 2010.

#### Amendments issued since publication

Amd. No.

Date

Text affected

### EUROPEAN STANDARD NORME EUROPÉENNE EUROPÄISCHE NORM

### EN 61508-2

May 2010

ICS 25.040.40

Supersedes EN 61508-2:2001

English version

# Functional safety of electrical/electronic/programmable electronic safety-related systems -

# Part 2: Requirements for electrical/electronic/programmable electronic safety-related systems

(IEC 61508-2:2010)

Sécurité fonctionnelle des systèmes électriques/électroniques/électroniques programmables relatifs à la sécurité - Partie 2: Exigences pour les systèmes électriques/électroniques/électroniques programmables relatifs à la sécurité (CEI 61508-2:2010)

Funktionale Sicherheit sicherheitsbezogener elektrischer/elektronischer/programmierbarer elektronischer Systeme Teil 2: Anforderungen an sicherheitsbezogene elektrische/elektronische/programmierbare elektronische Systeme (IEC 61508-2:2010)

This European Standard was approved by CENELEC on 2010-05-01. CENELEC members are bound to comply with the CEN/CENELEC Internal Regulations which stipulate the conditions for giving this European Standard the status of a national standard without any alteration.

Up-to-date lists and bibliographical references concerning such national standards may be obtained on application to the Central Secretariat or to any CENELEC member.

This European Standard exists in three official versions (English, French, German). A version in any other language made by translation under the responsibility of a CENELEC member into its own language and notified to the Central Secretariat has the same status as the official versions.

CENELEC members are the national electrotechnical committees of Austria, Belgium, Bulgaria, Croatia, Cyprus, the Czech Republic, Denmark, Estonia, Finland, France, Germany, Greece, Hungary, Iceland, Ireland, Italy, Latvia, Lithuania, Luxembourg, Malta, the Netherlands, Norway, Poland, Portugal, Romania, Slovakia, Slovenia, Spain, Sweden, Switzerland and the United Kingdom.

### **CENELEC**

European Committee for Electrotechnical Standardization Comité Européen de Normalisation Electrotechnique Europäisches Komitee für Elektrotechnische Normung

Management Centre: Avenue Marnix 17, B - 1000 Brussels

#### **Foreword**

The text of document 65A/549/FDIS, future edition 2 of IEC 61508-2, prepared by SC 65A, System aspects, of IEC TC 65, Industrial-process measurement, control and automation, was submitted to the IEC-CENELEC parallel vote and was approved by CENELEC as EN 61508-2 on 2010-05-01.

This European Standard supersedes EN 61508-2:2001.

It has the status of a basic safety publication according to IEC Guide 104.

Attention is drawn to the possibility that some of the elements of this document may be the subject of patent rights. CEN and CENELEC shall not be held responsible for identifying any or all such patent rights.

The following dates were fixed:

latest date by which the EN has to be implemented at national level by publication of an identical national standard or by endorsement

(dop) 2011-02-01

latest date by which the national standards conflicting with the EN have to be withdrawn

(dow) 2013-05-01

Annex ZA has been added by CENELEC.

#### **Endorsement notice**

The text of the International Standard IEC 61508-2:2010 was approved by CENELEC as a European Standard without any modification.

In the official version, for Bibliography, the following notes have to be added for the standards indicated:

| [1] IEC 61511 series | NOTE | Harmonized in EN 61511 series (not modified).       |

|----------------------|------|-----------------------------------------------------|

| [2] IEC 62061        | NOTE | Harmonized as EN 62061.                             |

| [3] IEC 61800-5-2    | NOTE | Harmonized as EN 61800-5-2.                         |

| [4] IEC 61508-5:2010 | NOTE | Harmonized as EN 61508-5:2010 (not modified).       |

| [5] IEC 61508-6:2010 | NOTE | Harmonized as EN 61508-6:2010 (not modified).       |

| [6] IEC 60601 series | NOTE | Harmonized in EN 60601 series (partially modified). |

| [7] IEC 61165        | NOTE | Harmonized as EN 61165.                             |

| [8] IEC 61078        | NOTE | Harmonized as EN 61078.                             |

| [9] IEC 61164        | NOTE | Harmonized as EN 61164.                             |

| [10] IEC 62308       | NOTE | Harmonized as EN 62308.                             |

| [11] IEC 61000-6-2   | NOTE | Harmonized as EN 61000-6-2.                         |

| [12] ISO 14224       | NOTE | Harmonized as EN ISO 14224.                         |

| [14] ISO 9000        | NOTE | Harmonized as EN ISO 9000.                          |

| [15] IEC 60300-3-2   | NOTE | Harmonized as EN 60300-3-2.                         |

|                      |      |                                                     |

## Annex ZA (normative)

## Normative references to international publications with their corresponding European publications

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

NOTE When an international publication has been modified by common modifications, indicated by (mod), the relevant EN/HD applies.

| <u>Publication</u> | <u>Year</u> | <u>Title</u>                                                                                                                                                                                                                                                          | EN/HD        | <u>Year</u> |

|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------------|

| -                  | -           | Relays with forcibly guided (mechanically linked) contacts                                                                                                                                                                                                            | EN 50205     | -           |

| IEC 60947-5-1      | -           | Low-voltage switchgear and controlgear -<br>Part 5-1: Control circuit devices<br>and switching elements - Electromechanical<br>control circuit devices                                                                                                                | EN 60947-5-1 | -           |

| IEC/TS 61000-1-2   | -           | Electromagnetic compatibility (EMC) -<br>Part 1-2: General - Methodology for the<br>achievement of functional safety of electrical<br>and electronic systems including equipment<br>with regard to electromagnetic phenomena                                          | -            | -           |

| IEC 61326-3-1      | -           | Electrical equipment for measurement, control and laboratory use - EMC requirements - Part 3-1: Immunity requirements for safety-related systems and for equipment intended to perform safety-related functions (functional safety) - General industrial applications | EN 61326-3-1 | -           |

| IEC 61508-1        | 2010        | Functional safety of electrical/electronic/programmable electronic safety-related systems - Part 1: General requirements                                                                                                                                              | EN 61508-1   | 2010        |

| IEC 61508-3        | 2010        | Functional safety of electrical/electronic/programmable electronic safety-related systems - Part 3: Software requirements                                                                                                                                             | EN 61508-3   | 2010        |

| IEC 61508-4        | 2010        | Functional safety of electrical/electronic/programmable electronic safety-related systems - Part 4: Definitions and abbreviations                                                                                                                                     | EN 61508-4   | 2010        |

| IEC 61508-7        | 2010        | Functional safety of electrical/electronic/programmable electronic safety-related systems - Part 7: Overview of techniques and measures                                                                                                                               | EN 61508-7   | 2010        |

| IEC 61784-3        | -           | Industrial communication networks - Profiles - Part 3: Functional safety fieldbuses - General rules and profile definitions                                                                                                                                           | EN 61784-3   | -           |

EN 61508-2:2010

| <u>Publication</u> | <u>Year</u> | <u>Title</u>                                                                                                                                  | EN/HD | Year |

|--------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| IEC 62280-1        | -           | Railway applications - Communication, signalling and processing systems - Part 1: Safety-related communication in closed transmission systems | -     | -    |

| IEC 62280-2        | -           | Railway applications - Communication, signalling and processing systems - Part 2: Safety-related communication in open transmission systems   | -     | -    |

| IEC Guide 104      | 1997        | The preparation of safety publications and the use of basic safety publications and group safety publications                                 | -     | -    |

| ISO/IEC Guide 51   | 1999        | Safety aspects - Guidelines for their inclusion in standards                                                                                  | -     | -    |

### CONTENTS

| IN. | TROD  | UCTION         |                                                                     | 7  |

|-----|-------|----------------|---------------------------------------------------------------------|----|

| 1   | Scop  | e              |                                                                     | 9  |

| 2   | Norn  | native re      | ferences                                                            | 12 |

| 3   | Defir | nitions ar     | nd abbreviations                                                    | 12 |

| 4   | Conf  | ormance        | e to this standard                                                  | 12 |

| 5   |       |                | on                                                                  |    |

| 6   |       |                | of functional safety                                                |    |

| 7   |       | _              | em safety lifecycle requirements                                    |    |

| ′   |       | •              |                                                                     |    |

|     | 7.1   |                | Objectives and requirements assembly                                |    |

|     |       | 7.1.1          | Objectives and requirements – general Objectives                    |    |

|     |       | 7.1.2<br>7.1.3 | •                                                                   |    |

|     | 7.2   |                | Requirementssystem design requirements specification                |    |

|     | 1.2   | 7.2.1          | Objective                                                           |    |

|     |       | 7.2.1          | General                                                             |    |

|     |       | 7.2.2          | E/E/PE system design requirements specification                     |    |

|     | 7.3   |                | system safety validation planning                                   |    |

|     | 7.5   | 7.3.1          | Objective                                                           |    |

|     |       | 7.3.1          | Requirements                                                        |    |

|     | 7.4   | _              | system design and development                                       |    |

|     | 7.4   | 7.4.1          | Objective                                                           |    |

|     |       | 7.4.2          | General requirements                                                |    |

|     |       | 7.4.3          | Synthesis of elements to achieve the required systematic capability |    |

|     |       | 7.4.4          | Hardware safety integrity architectural constraints                 |    |

|     |       | 7.4.5          | Requirements for quantifying the effect of random hardware failures |    |

|     |       | 7.4.6          | Requirements for the avoidance of systematic faults                 |    |

|     |       | 7.4.7          | Requirements for the control of systematic faults                   |    |

|     |       | 7.4.8          | Requirements for system behaviour on detection of a fault           |    |

|     |       | 7.4.9          | Requirements for E/E/PE system implementation                       |    |

|     |       |                | Requirements for proven in use elements                             |    |

|     |       |                | Additional requirements for data communications                     |    |

|     | 7.5   |                | system integration                                                  |    |

|     |       | 7.5.1          | Objective                                                           |    |

|     |       | 7.5.2          | Requirements                                                        |    |

|     | 7.6   | E/E/PE         | system operation and maintenance procedures                         |    |

|     |       | 7.6.1          | Objective                                                           | 41 |

|     |       | 7.6.2          | Requirements                                                        | 41 |

|     | 7.7   | E/E/PE         | system safety validation                                            | 42 |

|     |       | 7.7.1          | Objective                                                           | 42 |

|     |       | 7.7.2          | Requirements                                                        | 42 |

|     | 7.8   | E/E/PE         | system modification                                                 | 43 |

|     |       | 7.8.1          | Objective                                                           | 43 |

|     |       | 7.8.2          | Requirements                                                        | 43 |

|     | 7.9   | E/E/PE         | system verification                                                 | 44 |

|     |       | 7.9.1          | Objective                                                           | 44 |

| 7.9.2 Requirements                                                                                                                                                          | 44 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 8 Functional safety assessment                                                                                                                                              | 46 |

| Annex A (normative) Techniques and measures for E/E/PE safety-related systems – control of failures during operation                                                        | 47 |

| Annex B (normative) Techniques and measures for E/E/PE safety-related systems – avoidance of systematic failures during the different phases of the lifecycle               | 62 |

| Annex C (normative) Diagnostic coverage and safe failure fraction                                                                                                           | 71 |

| Annex D (normative) Safety manual for compliant items                                                                                                                       | 74 |

| Annex E (normative) Special architecture requirements for integrated circuits (ICs) with on-chip redundancy                                                                 | 76 |

| Annex F (informative) Techniques and measures for ASICs – avoidance of systematic failures                                                                                  | 81 |

| Bibliography                                                                                                                                                                | 89 |

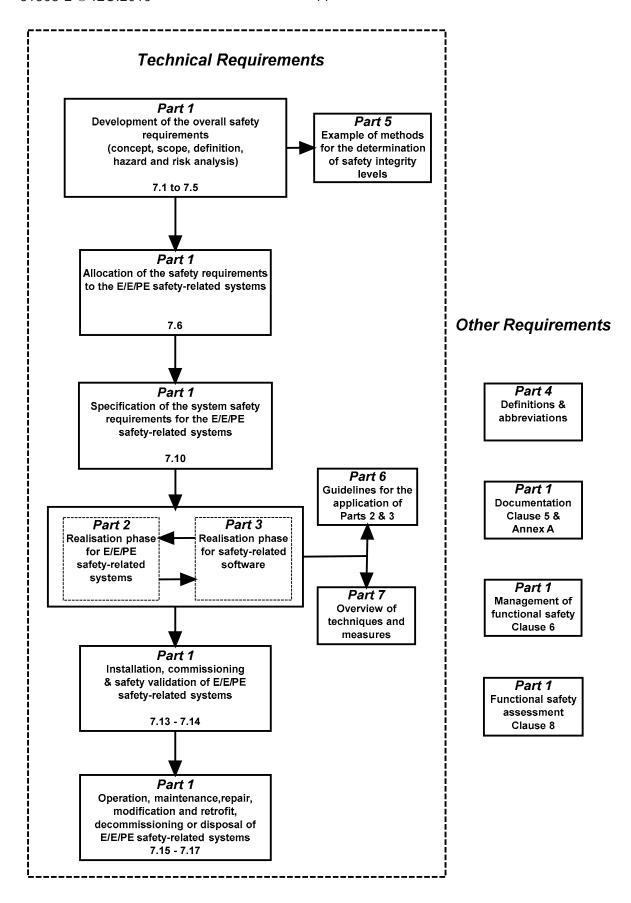

| Figure 1 – Overall framework of the IEC 61508 series                                                                                                                        |    |

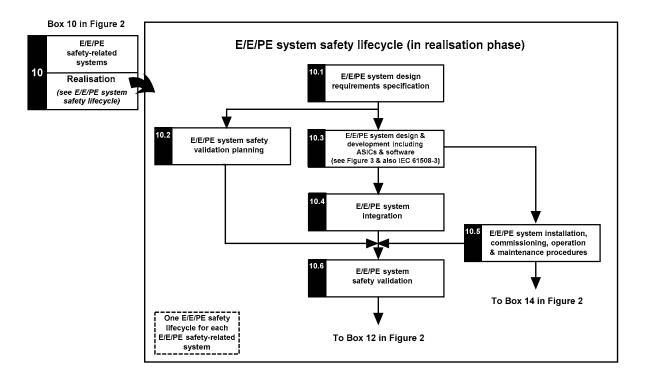

| Figure 2 – E/E/PE system safety lifecycle (in realisation phase)                                                                                                            |    |

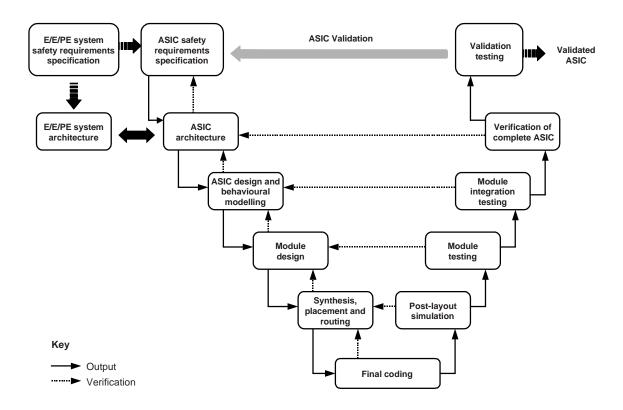

| Figure 3 – ASIC development lifecycle (the V-Model)                                                                                                                         |    |

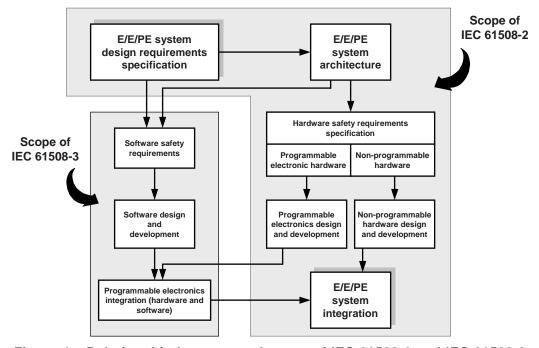

| Figure 4 – Relationship between and scope of IEC 61508-2 and IEC 61508-3                                                                                                    | 15 |

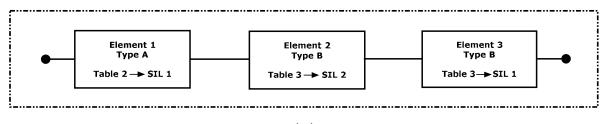

| Figure 5 – Determination of the maximum SIL for specified architecture (E/E/PE safety-related subsystem comprising a number of series elements, see 7.4.4.2.3)              | 28 |

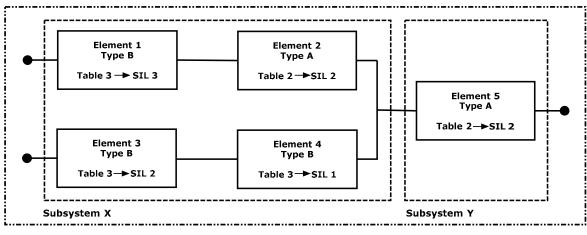

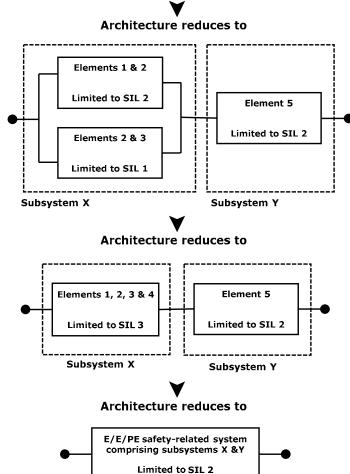

| Figure 6 – Determination of the maximum SIL for specified architecture (E/E/PE safety-related subsystem comprised of two subsystems X & Y, see 7.4.4.2.4)                   | 30 |

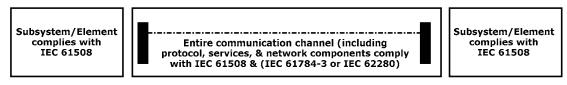

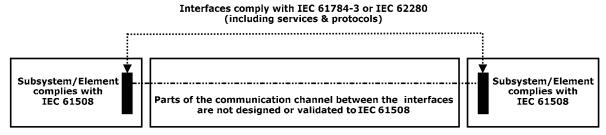

| Figure 7 – Architectures for data communication                                                                                                                             | 40 |

| Table 1 – Overview – realisation phase of the E/E/PE system safety lifecycle                                                                                                | 16 |

| Table 2 – Maximum allowable safety integrity level for a safety function carried out by a type A safety-related element or subsystem                                        | 26 |

| Table 3 – Maximum allowable safety integrity level for a safety function carried out by a type B safety-related element or subsystem                                        | 27 |

| Table A.1 – Faults or failures to be assumed when quantifying the effect of random hardware failures or to be taken into account in the derivation of safe failure fraction | 49 |

| Table A.2 – Electrical components                                                                                                                                           | 51 |

| Table A.3 – Electronic components                                                                                                                                           | 51 |

| Table A.4 – Processing units                                                                                                                                                | 52 |

| Table A.5 – Invariable memory ranges                                                                                                                                        | 52 |

| Table A.6 – Variable memory ranges                                                                                                                                          | 53 |

| Table A.7 – I/O units and interface (external communication)                                                                                                                | 53 |

| Table A.8 – Data paths (internal communication)                                                                                                                             | 54 |

| Table A.9 – Power supply                                                                                                                                                    | 54 |

| Table A.10 – Program sequence (watch-dog)                                                                                                                                   | 55 |

| Table A.11 – Clock                                                                                                                                                          | 55 |

| Table A.12 – Communication and mass-storage                                                                                                                                 | 55 |

| Table A.13 – Sensors                                                                                                                                                        | 56 |

| Table A.14 – Final elements (actuators)                                                                                                                                     | 56 |

| Table A.15 – Techniques and measures to control systematic failures caused by hardware design                                                                               | 58 |

| Table A.16 – Techniques and measures to control systematic failures caused by environmental stress or influences                                        | 59 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table A.17 – Techniques and measures to control systematic operational failures                                                                         | 60 |

| Table A.18 – Effectiveness of techniques and measures to control systematic failures                                                                    | 61 |

| Table B.1 – Techniques and measures to avoid mistakes during specification of E/E/PE system design requirements (see 7.2)                               | 63 |

| Table B.2 – Techniques and measures to avoid introducing faults during E/E/PE system design and development (see 7.4)                                   | 64 |

| Table B.3 – Techniques and measures to avoid faults during E/E/PE system integration (see 7.5)                                                          | 65 |

| Table B.4 – Techniques and measures to avoid faults and failures during E/E/PE system operation and maintenance procedures (see 7.6)                    | 66 |

| Table B.5 – Techniques and measures to avoid faults during E/E/PE system safety validation (see 7.7)                                                    | 67 |

| Table B.6 – Effectiveness of techniques and measures to avoid systematic failures                                                                       | 68 |

| Table E.1 – Techniques and measures that increase β <sub>B-IC</sub>                                                                                     | 79 |

| Table E.2 – Techniques and measures that decrease β <sub>B-IC</sub>                                                                                     | 80 |

| Table F.1 – Techniques and measures to avoid introducing faults during ASIC's design and development – full and semi-custom digital ASICs (see 7.4.6.7) | 83 |

| Table F.2 – Techniques and measures to avoid introducing faults during ASIC design and development: User programmable ICs (FPGA/PLD/CPLD) (see 7.4.6.7) | 86 |

61508-2 © IEC:2010

#### INTRODUCTION

Systems comprised of electrical and/or electronic elements have been used for many years to perform safety functions in most application sectors. Computer-based systems (generically referred to as programmable electronic systems) are being used in all application sectors to perform non-safety functions and, increasingly, to perform safety functions. If computer system technology is to be effectively and safely exploited, it is essential that those responsible for making decisions have sufficient guidance on the safety aspects on which to make these decisions.

This International Standard sets out a generic approach for all safety lifecycle activities for systems comprised of electrical and/or electronic and/or programmable electronic (E/E/PE) elements that are used to perform safety functions. This unified approach has been adopted in order that a rational and consistent technical policy be developed for all electrically-based safety-related systems. A major objective is to facilitate the development of product and application sector international standards based on the IEC 61508 series.

NOTE 1 Examples of product and application sector international standards based on the IEC 61508 series are given in the Bibliography (see references [1], [2] and [3]).

In most situations, safety is achieved by a number of systems which rely on many technologies (for example mechanical, hydraulic, pneumatic, electrical, electronic, programmable electronic). Any safety strategy must therefore consider not only all the elements within an individual system (for example sensors, controlling devices and actuators) but also all the safety-related systems making up the total combination of safety-related systems. Therefore, while this International Standard is concerned with E/E/PE safety-related systems, it may also provide a framework within which safety-related systems based on other technologies may be considered.

It is recognized that there is a great variety of applications using E/E/PE safety-related systems in a variety of application sectors and covering a wide range of complexity, hazard and risk potentials. In any particular application, the required safety measures will be dependent on many factors specific to the application. This International Standard, by being generic, will enable such measures to be formulated in future product and application sector international standards and in revisions of those that already exist.

#### This International Standard

- considers all relevant overall, E/E/PE system and software safety lifecycle phases (for example, from initial concept, though design, implementation, operation and maintenance to decommissioning) when E/E/PE systems are used to perform safety functions;

- has been conceived with a rapidly developing technology in mind; the framework is sufficiently robust and comprehensive to cater for future developments;

- enables product and application sector international standards, dealing with E/E/PE safety-related systems, to be developed; the development of product and application sector international standards, within the framework of this standard, should lead to a high level of consistency (for example, of underlying principles, terminology etc.) both within application sectors and across application sectors; this will have both safety and economic benefits;

- provides a method for the development of the safety requirements specification necessary to achieve the required functional safety for E/E/PE safety-related systems;

- adopts a risk-based approach by which the safety integrity requirements can be determined;

- introduces safety integrity levels for specifying the target level of safety integrity for the safety functions to be implemented by the E/E/PE safety-related systems;

NOTE 2 The standard does not specify the safety integrity level requirements for any safety function, nor does it mandate how the safety integrity level is determined. Instead it provides a risk-based conceptual framework and example techniques.

- sets target failure measures for safety functions carried out by E/E/PE safety-related systems, which are linked to the safety integrity levels;

- a low demand mode of operation, the lower limit is set at an average probability of a dangerous failure on demand of 10<sup>-5</sup>;

- a high demand or a continuous mode of operation, the lower limit is set at an average frequency of a dangerous failure of  $10^{-9}$  [h<sup>-1</sup>];

NOTE 3 A single E/E/PE safety-related system does not necessarily mean a single-channel architecture.

NOTE 4 It may be possible to achieve designs of safety-related systems with lower values for the target safety integrity for non-complex systems, but these limits are considered to represent what can be achieved for relatively complex systems (for example programmable electronic safety-related systems) at the present time.

- sets requirements for the avoidance and control of systematic faults, which are based on experience and judgement from practical experience gained in industry. Even though the probability of occurrence of systematic failures cannot in general be quantified the standard does, however, allow a claim to be made, for a specified safety function, that the target failure measure associated with the safety function can be considered to be achieved if all the requirements in the standard have been met;

- introduces systematic capability which applies to an element with respect to its confidence that the systematic safety integrity meets the requirements of the specified safety integrity level:

- adopts a broad range of principles, techniques and measures to achieve functional safety for E/E/PE safety-related systems, but does not explicitly use the concept of fail safe. However, the concepts of "fail safe" and "inherently safe" principles may be applicable and adoption of such concepts is acceptable providing the requirements of the relevant clauses in the standard are met.

## FUNCTIONAL SAFETY OF ELECTRICAL/ELECTRONIC/ PROGRAMMABLE ELECTRONIC SAFETY-RELATED SYSTEMS –

## Part 2: Requirements for electrical/electronic/programmable electronic safety-related systems

#### 1 Scope

- 1.1 This part of the IEC 61508 series

- a) is intended to be used only after a thorough understanding of IEC 61508-1, which provides the overall framework for the achievement of functional safety;

- b) applies to any safety-related system, as defined by IEC 61508-1, that contains at least one electrical, electronic or programmable electronic element;

- c) applies to all elements within an E/E/PE safety-related system (including sensors, actuators and the operator interface);

- d) specifies how to refine the E/E/PE system safety requirements specification, developed in accordance with IEC 61508-1 (comprising the E/E/PE system safety functions requirements specification and the E/E/PE system safety integrity requirements specification), into the E/E/PE system design requirements specification;

- e) specifies the requirements for activities that are to be applied during the design and manufacture of the E/E/PE safety-related systems (i.e. establishes the E/E/PE system safety lifecycle model) except software, which is dealt with in IEC 61508-3 (see Figures 2 to 4). These requirements include the application of techniques and measures that are graded against the safety integrity level, for the avoidance of, and control of, faults and failures;

- f) specifies the information necessary for carrying out the installation, commissioning and final safety validation of the E/E/PE safety-related systems;

- g) does not apply to the operation and maintenance phase of the E/E/PE safety-related systems this is dealt with in IEC 61508-1 however, IEC 61508-2 does provide requirements for the preparation of information and procedures needed by the user for the operation and maintenance of the E/E/PE safety-related systems;

- h) specifies requirements to be met by the organisation carrying out any modification of the E/E/PE safety-related systems;

- NOTE 1 This part of IEC 61508 is mainly directed at suppliers and/or in-company engineering departments, hence the inclusion of requirements for modification.

- NOTE 2 The relationship between IEC 61508-2 and IEC 61508-3 is illustrated in Figure 4.

- i) does not apply for medical equipment in compliance with the IEC 60601 series.

- **1.2** IEC 61508-1, IEC 61508-2, IEC 61508-3 and IEC 61508-4 are basic safety publications, although this status does not apply in the context of low complexity E/E/PE safety-related systems (see 3.4.3 of IEC 61508-4). As basic safety publications, they are intended for use by technical committees in the preparation of standards in accordance with the principles contained in IEC Guide 104 and ISO/IEC Guide 51. IEC 61508-1, IEC 61508-2, IEC 61508-3 and IEC 61508-4 are also intended for use as stand-alone standards. The horizontal safety function of this international standard does not apply to medical equipment in compliance with the IEC 60601 series.

- 1.3 One of the responsibilities of a technical committee is, wherever applicable, to make use of basic safety publications in the preparation of its publications. In this context, the requirements, test methods or test conditions of this basic safety publication will not apply

unless specifically referred to or included in the publications prepared by those technical committees.

NOTE The functional safety of an E/E/PE safety-related system can only be achieved when all related requirements are met. Therefore, it is important that all related requirements are carefully considered and adequately referenced.

**1.4** Figure 1 shows the overall framework of the IEC 61508 series and indicates the role that IEC 61508-2 plays in the achievement of functional safety for E/E/PE safety-related systems. Annex A of IEC 61508-6 describes the application of IEC 61508-2 and IEC 61508-3.

61508-2 © IEC:2010

Figure 1 - Overall framework of the IEC 61508 series

#### 2 Normative references

The following referenced documents are indispensable for the application of this document. For dated references, only the edition cited applies. For undated references, the latest edition of the referenced document (including any amendments) applies.

IEC 60947-5-1, Low-voltage switchgear and controlgear – Part 5-1: Control circuit devices and switching elements – Electromechanical control circuit devices

IEC/TS 61000-1-2, Electromagnetic compatibility (EMC) – Part 1-2: General – Methodology for the achievement of functional safety of electrical and electronic systems including equipment with regard to electromagnetic phenomena

IEC 61326-3-1, Electrical equipment for measurement, control and laboratory use – EMC requirements – Part 3-1: Immunity requirements for safety-related systems and for equipment intended to perform safety-related functions (functional safety) – General industrial applications

IEC 61508-1: 2010, Functional safety of electrical/electronic/programmable electronic safety-related systems – Part 1: General requirements

IEC 61508-3: 2010, Functional safety of electrical/electronic/programmable electronic safety-related systems – Part 3: Software requirements

IEC 61508-4: 2010, Functional safety of electrical/electronic/programmable electronic safety-related systems – Part 4: Definitions and abbreviations

IEC 61508-7: 2010, Functional safety of electrical/electronic/programmable electronic safety related systems – Part 7: Overview of techniques and measures

IEC 61784-3, Industrial communication networks – Profiles – Part 3: Functional safety fieldbuses – General rules and profile definitions

IEC 62280-1, Railway applications – Communication, signalling and processing systems – Part 1: Safety-related communication in closed transmission systems

IEC 62280-2, Railway applications – Communication, signalling and processing systems – Part 2: Safety-related communication in open transmission systems

IEC Guide 104:1997, The preparation of safety publications and the use of basic safety publications and group safety publications

ISO/IEC Guide 51:1999, Safety aspects - Guidelines for their inclusion in standards

EN 50205, Relays with forcibly guided (mechanically linked) contacts

#### 3 Definitions and abbreviations

For the purposes of this document, the definitions and abbreviations given in IEC 61508-4 apply.

#### 4 Conformance to this standard

The requirements for conformance to this standard are as detailed in Clause 4 of IEC 61508-1.

#### 5 Documentation

The requirements for documentation are as detailed in Clause 5 of IEC 61508-1.

#### 6 Management of functional safety

The requirements for management of functional safety are as detailed in Clause 6 of IEC 61508-1.

#### 7 E/E/PE system safety lifecycle requirements

#### 7.1 General

#### 7.1.1 Objectives and requirements – general

**7.1.1.1** This subclause sets out the objectives and requirements for the E/E/PE system safety lifecycle phases.

NOTE The objectives and requirements for the overall safety lifecycle, together with a general introduction to the structure of the standard, are given in IEC 61508-1.

- 7.1.1.2 For all phases of the E/E/PE system safety lifecycle, Table 1 indicates

- the objectives to be achieved;

- the scope of the phase;

- a reference to the subclause containing the requirements;

- the required inputs to the phase;

- the outputs required to comply with the subclause.

#### 7.1.2 Objectives

- **7.1.2.1** The first objective of the requirements of this subclause is to structure, in a systematic manner, the phases in the E/E/PE system safety lifecycle that shall be considered in order to achieve the required functional safety of the E/E/PE safety-related systems.

- **7.1.2.2** The second objective of the requirements of this subclause is to document all information relevant to the functional safety of the E/E/PE safety-related systems throughout the E/E/PE system safety lifecycle.

#### 7.1.3 Requirements

- **7.1.3.1** The E/E/PE system safety lifecycle that shall be used in claiming conformance with this standard is that specified in Figure 2. A detailed V-model of the ASIC development lifecycle for the design of ASICs (see IEC 61508-4, 3.2.15) is shown in Figure 3. If another E/E/PE system safety lifecycle or ASIC development lifecycle is used, it shall be specified as part of the management of functional safety activities (see Clause 6 of IEC 61508-1), and all the objectives and requirements of each subclause of IEC 61508-2 shall be met.

- NOTE 1 The relationship between and scope for IEC 61508-2 and IEC 61508-3 are shown in Figure 4.

- NOTE 2 There are significant similarities between the ASIC and the software design processes. IEC 61508-3 recommends the V-model for designing safety-related software. The V-model requires a clearly structured design process and a modular software structure for avoiding and controlling systematic faults. The ASIC development lifecycle for the design of ASICs in Figure 3 follows this model. At first the requirements for the ASIC specification are derived from the system requirements. ASIC architecture, ASIC design and module design follow. The results of each step on the left-hand side of the V become the input to the next step, and are also fed back to the preceding step for iteration where appropriate, until the final code is created. This code is verified against the corresponding design through post-layout simulation, module testing, module integration testing and verification of the complete ASIC. The results of any step may necessitate a revision to any of the preceding steps. Finally, the ASIC is validated after its integration into the E/E/PE safety-related system.

- **7.1.3.2** The procedures for management of functional safety (see Clause 6 of IEC 61508-1) shall run in parallel with the E/E/PE system safety lifecycle phases.

- **7.1.3.3** Each phase of the E/E/PE system safety lifecycle shall be divided into elementary activities, with the scope, inputs and outputs specified for each phase (see Table 1).

- **7.1.3.4** Unless justified as part of the management of functional safety activities (see Clause 6 of IEC 61508-1), the outputs of each phase of the E/E/PE system safety lifecycle shall be documented (see Clause 5 of IEC 61508-1).

- **7.1.3.5** The outputs for each E/E/PE system safety lifecycle phase shall meet the objectives and requirements specified for each phase (see 7.2 to 7.9).

NOTE 1 See also IEC 61508-6, A.2 b).

NOTE 2 This figure shows only those phases of the E/E/PE system safety lifecycle that are within the realisation phase of the overall safety lifecycle. The complete E/E/PE system safety lifecycle will also contain instances, specific to the E/E/PE safety-related system, of the subsequent phases of the overall safety lifecycle (Boxes 12 to 16 in Figure 2 of IEC 61508-1).

Figure 2 – E/E/PE system safety lifecycle (in realisation phase)

Figure 3 - ASIC development lifecycle (the V-Model)

Figure 4 - Relationship between and scope of IEC 61508-2 and IEC 61508-3

Table 1 – Overview – realisation phase of the E/E/PE system safety lifecycle

| Safety lifecycle phase or activity  Figure 2 box Title number |                                                                                                    |                                                                                                                                                                      |                                               | Require-                |                                                                                                                                                                         |                                                                                                                                    |

|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|                                                               |                                                                                                    | Objectives                                                                                                                                                           | Scope                                         | ments<br>sub-<br>clause | Inputs                                                                                                                                                                  | Outputs                                                                                                                            |

| 10.1                                                          | E/E/PE system<br>design<br>requirements<br>specification                                           | To specify the design requirements for each E/E/PE safety-related system, in terms of the subsystems and elements (see 7.10.2 of IEC 61508-1)                        | E/E/PE<br>safety-<br>related<br>system        | 7.2.2                   | E/E/PE system safety<br>requirements<br>specification<br>(see IEC 61508-1,<br>7.10)                                                                                     | E/E/PE system design<br>requirements<br>specification, describing<br>the equipment and<br>architectures for the<br>E/E/PE system   |

| 10.2                                                          | E/E/PE system<br>safety<br>validation<br>planning                                                  | To plan the validation of<br>the safety of the E/E/PE<br>safety-related system                                                                                       | E/E/PE<br>safety-<br>related<br>system        | 7.3.2                   | E/E/PE system safety<br>requirements<br>specification and<br>E/E/PE system<br>design requirements<br>specification                                                      | Plan for the safety<br>validation<br>of the E/E/PE safety-<br>related systems                                                      |

| 10.3                                                          | E/E/PE system<br>design &<br>development<br>including<br>ASICs &                                   | appropriate) to meet the E/E/PE system design requirements specification                                                                                             | E/E/PE<br>safety-<br>related<br>system        | 7.4.2<br>to<br>7.4.11   | E/E/PE system<br>design requirements<br>specification                                                                                                                   | Design of the E/E/PE<br>safety related systems<br>in conformance with the<br>E/E/PE system design<br>requirements<br>specification |

|                                                               | software                                                                                           | (with respect to the safety<br>functions requirements<br>and the safety integrity                                                                                    |                                               |                         |                                                                                                                                                                         | Plan for the E/E/PE<br>system integration test                                                                                     |

|                                                               | (see Figure 3<br>& also<br>IEC 61508-3)                                                            | requirements (see 7.2))                                                                                                                                              |                                               |                         |                                                                                                                                                                         | PE system architectural information as an input to the software requirements specification                                         |

| 10.4                                                          | E/E/PE system integration                                                                          | To integrate and test the E/E/PE safety-related system                                                                                                               | E/E/PE<br>safety-<br>related                  | 7.5.2                   | E/E/PE system design                                                                                                                                                    | Fully functioning E/E/PE safety-related systems in conformance with the                                                            |

|                                                               |                                                                                                    | , , , , , , , , , , , , , , , , , , , ,                                                                                                                              | system                                        |                         | E/E/PE system integration test plan                                                                                                                                     | E/E/PE system design                                                                                                               |

|                                                               |                                                                                                    |                                                                                                                                                                      |                                               |                         | Programmable electronics hardware and software                                                                                                                          | Results of E/E/PE<br>system integration tests                                                                                      |

| 10.5                                                          | E/E/PE system<br>installation,<br>commissioning<br>, operation<br>and<br>maintenance<br>procedures | To develop procedures to ensure that the required functional safety of the E/E/PE safety-related system is maintained during operation and maintenance               | E/E/PE<br>safety-<br>related<br>system<br>EUC | 7.6.2                   | E/E/PE system<br>design requirements<br>specification<br>E/E/PE system<br>design                                                                                        | E/E/PE system installation, commissioning, operation and maintenance procedures for each individual E/E/PE system                  |

| 10.6                                                          | E/E/PE system<br>safety<br>validation                                                              | To validate that the E/E/PE safety-related system meets, in all respects, the requirements for safety in terms of the required safety functions and safety integrity | E/E/PE<br>safety-<br>related<br>system        | 7.7.2                   | E/E/PE system safety requirements specification and E/E/PE system design requirements specification Plan for the safety validation of the E/E/PE safety-related systems | Fully safety validated<br>E/E/PE safety-related<br>systems<br>Results of E/E/PE<br>system safety validation                        |

Table 1 (continued)

| Safety lifecycle phase or activity |                                                     |                                                                                                                                                                    |                                        | Require-<br>ments |                                                                                                                                 |                                                                                                                                |  |

|------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|

| Figure<br>2 box<br>number          | Title                                               | Objectives                                                                                                                                                         | Scope                                  | sub-<br>clause    | Inputs                                                                                                                          | Outputs                                                                                                                        |  |

| _                                  | E/E/PE system modification                          | To make corrections, enhancements or adaptations to the E/E/PE safety-related system, ensuring that the required safety integrity is achieved and maintained       | E/E/PE<br>safety-<br>related<br>system | 7.8.2             | E/E/PE system<br>design requirements<br>specification                                                                           | Results of E/E/PE<br>system modification                                                                                       |  |

| _                                  | E/E/PE system verification                          | To test and evaluate the outputs of a given phase to ensure correctness and consistency with respect to the products and standards provided as input to that phase | E/E/PE<br>safety-<br>related<br>system | 7.9.2             | As above – depends<br>on the phase<br>Plan for the<br>verification of the<br>E/E/PE safety-related<br>systems for each<br>phase | As above – depends on<br>the phase<br>Results of the<br>verification of the<br>E/E/PE safety-related<br>systems for each phase |  |

| _                                  | E/E/PE system<br>functional<br>safety<br>assessment | To investigate and arrive at a judgement on the functional safety achieved by the E/E/PE safety-related system                                                     | E/E/PE<br>safety-<br>related<br>system | 8                 | Plan for E/E/PE<br>system functional<br>safety assessment                                                                       | Results of E/E/PE<br>system functional safety<br>assessment                                                                    |  |

#### 7.2 E/E/PE system design requirements specification

NOTE This phase is Box 10.1 of Figure 2.

#### 7.2.1 Objective

The objective of the requirements of this subclause is to specify the design requirements for each E/E/PE safety-related system, in terms of the subsystems and elements.

NOTE The E/E/PE system design requirements specification is normally derived from the E/E/PE system safety requirements specification by decomposing the safety functions and allocating parts of the safety function to subsystems (for example groups of sensors, logic solvers or actuators). The requirements for the subsystems may be included in the E/E/PE system design requirements specification or may be separate and referenced from the E/E/PE system design requirements specification. Subsystems may be further decomposed into elements and architectures to satisfy the design and development requirements of 7.4. The requirements for these elements may be included in the requirements for the subsystems or may be separate and referenced from the subsystem requirements.

#### 7.2.2 General

**7.2.2.1** The specification of the E/E/PE system design requirements shall be derived from the E/E/PE system safety requirements, specified in 7.10 of IEC 61508-1.

NOTE Caution should be exercised if non-safety functions and safety functions are implemented in the same E/E/PE safety-related system. While this is allowed in the standard, it may lead to greater complexity and increase the difficulty in carrying out E/E/PE safety lifecycle activities (for example design, validation, functional safety assessment and maintenance). See also 7.4.2.3.

- **7.2.2.2** The specification of the E/E/PE system design requirements shall be expressed and structured in such a way that they are:

- a) clear, precise, unambiguous, verifiable, testable, maintainable and feasible;

- b) written to aid comprehension by those who are likely to utilise the information at any phase of the E/E/PE safety lifecycle; and

- c) traceable to the E/E/PE system safety requirements specification.

#### 7.2.3 E/E/PE system design requirements specification

- **7.2.3.1** The specification of the E/E/PE system design requirements shall contain design requirements relating to safety functions (see 7.2.3.2) and design requirements relating to safety integrity (see 7.2.3.3).

- **7.2.3.2** The specification of the E/E/PE system design requirements shall contain details of all the hardware and software necessary to implement the required safety functions, as specified by the E/E/PE system safety functions requirements specification (see 7.10.2.6 of IEC 61508-1). The specification shall include, for each safety function:

- a) requirements for the subsystems and requirements for their hardware and software elements as appropriate;

- b) requirements for the integration of the subsystems and their hardware and software elements to meet the E/E/PE system safety functions requirements specification;

- c) throughput performance that enables response time requirements to be met;

- d) accuracy and stability requirements for measurements and controls;

- e) E/E/PE safety-related system and operator interfaces;

- f) interfaces between the E/E/PE safety-related systems and any other systems (either within, or outside, the EUC);

- g) all modes of behaviour of the E/E/PE safety-related systems, in particular, failure behaviour and the required response (for example alarms, automatic shut-down) of the E/E/PE safety-related systems;

- h) the significance of all hardware/software interactions and, where relevant, any required constraints between the hardware and the software;

NOTE Where these interactions are not known before finishing the design, only general constraints can be stated.

- any limiting and constraint conditions for the E/E/PE safety-related systems and their associated elements, for example timing constraints or constraints due to the possibility of common cause failures;

- j) any specific requirements related to the procedures for starting-up and restarting the E/E/PE safety-related systems.

- **7.2.3.3** The specification of the E/E/PE system design requirements shall contain details, relevant to the design, to achieve the safety integrity level and the required target failure measure for the safety function, as specified by the E/E/PE system safety integrity requirements specification (see 7.10.2.7 of IEC 61508-1), including:

- a) the architecture of each subsystem required to meet the architectural constraints on the hardware safety integrity (see 7.4.4);

- b) all relevant reliability modelling parameters such as the required proof testing frequency of all hardware elements necessary to achieve the target failure measure;

- NOTE 1 Information on the specific application cannot be understated (see 7.10.2.1 of IEC 61508-1). This is particularly important for maintenance, where the specified proof test interval should not be less than can be reasonably expected for the particular application. For example, the time between services that can be realistically attained for mass-produced items used by the public is likely to be greater than in a more controlled application.

- c) the actions taken in the event of a dangerous failure being detected by diagnostics;

- d) the requirements, constraints, functions and facilities to enable the proof testing of the E/E/PE hardware to be undertaken:

- e) the capabilities of equipment used to meet the extremes of all environmental conditions (e.g. temperature, humidity, mechanical, electrical) that are specified as required during the E/E/PE system safety lifecycle including manufacture, storage, transport, testing, installation, commissioning, operation and maintenance;

- f) the electromagnetic immunity levels that are required (see IEC/TS 61000-1-2: 2008);

- NOTE 2 The required immunity levels may vary for different elements of the safety-related system, depending on physical location and power supply arrangements.

- NOTE 3 Guidance may be found in EMC product standards, but it is important to recognise that higher immunity levels, or additional immunity requirements, than those specified in such standards may be necessary for particular locations or when the equipment is intended for use in harsher, or different, electromagnetic environments.

- g) the quality assurance/quality control measures necessary to safety management (see 6.2.5 of IEC 61508-1);

- **7.2.3.4** The E/E/PE system design requirements specification shall be completed in detail as the design progresses and updated as necessary after modification.

- **7.2.3.5** For the avoidance of mistakes during the development of the specification for the E/E/PE system design requirements, an appropriate group of techniques and measures according to Table B.1 shall be used.

- **7.2.3.6** The implications imposed on the architecture by the E/E/PE system design requirements shall be considered.

NOTE This should include the consideration of the simplicity of the implementation to achieve the required safety integrity level (including architectural considerations and apportionment of functionality to configuration data or to the embedded system).

#### 7.3 E/E/PE system safety validation planning

NOTE This phase is Box 10.2 of Figure 2. It will normally be carried out in parallel with E/E/PE system design and development (see 7.4).

#### 7.3.1 Objective

The objective of the requirements of this subclause is to plan the validation of the safety of the E/E/PE safety-related system.

#### 7.3.2 Requirements

- **7.3.2.1** Planning shall be carried out to specify the steps (both procedural and technical) that are to be used to demonstrate that the E/E/PE safety-related system satisfies the E/E/PE system safety requirements specification (see 7.10 of IEC 61508-1) and the E/E/PE system design requirements specification (see 7.2).

- **7.3.2.2** Planning for the validation of the E/E/PE safety-related system shall consider the following:

- a) all of the requirements defined in the E/E/PE system safety requirements specification and the E/E/PE system design requirements specification;

- b) the procedures to be applied to validate that each safety function is correctly implemented, and the pass/fail criteria for accomplishing the tests;

- c) the procedures to be applied to validate that each safety function is of the required safety integrity, and the pass/fail criteria for accomplishing the tests;

- d) the required environment in which the testing is to take place including all necessary tools and equipment (also plan which tools and equipment should be calibrated);

- e) test evaluation procedures (with justifications);

- f) the test procedures and performance criteria to be applied to validate the specified electromagnetic immunity limits:

NOTE Guidance on the specification of electromagnetic immunity tests for elements of safety-related systems is given in IEC/TS 61000-1-2.

g) policies for resolving validation failure.

#### 7.4 E/E/PE system design and development

NOTE This phase is Box 10.3 of Figure 2. It will normally be carried out in parallel with E/E/PE system safety validation planning (see 7.3).

#### 7.4.1 Objective

The objective of the requirements of this subclause is to design and develop the E/E/PE safety-related system (including ASICs if appropriate, see IEC 61508-4, 3.2.15) to meet the E/E/PE system design requirements specification (with respect to the safety functions requirements and the safety integrity requirements (see 7.2).

#### 7.4.2 General requirements

- **7.4.2.1** The design of the E/E/PE safety-related system shall be created in accordance with the E/E/PE system design requirements specification (see 7.2.3), taking into account all the requirements of 7.2.3.

- **7.4.2.2** The design of the E/E/PE safety-related system (including the overall hardware and software architecture, sensors, actuators, programmable electronics, ASICs, embedded software, application software, data etc.), shall meet all of the requirements a) to e) as follows:

- a) the requirements for hardware safety integrity comprising;

- the architectural constraints on hardware safety integrity (see 7.4.4), and

- the requirements for quantifying the effect of random failures (see 7.4.5);

- b) the special architecture requirements for ICs with on-chip redundancy (see Annex E), where relevant, unless justification can be given that the same level of independence between different channels is achieved by applying a different set of measures;

- c) the requirements for systematic safety integrity (systematic capability), which can be met by achieving one of the following compliance routes:

- Route  $1_S$ : compliance with the requirements for the avoidance of systematic faults (see 7.4.6 and IEC 61508-3) and the requirements for the control of systematic faults (see 7.4.7 and IEC 61508-3), or

- Route 2<sub>S</sub>: compliance with the requirements for evidence that the equipment is proven in use (see 7.4.10), or

- Route 3<sub>S</sub> (pre-existing software elements only): compliance with the requirements of IEC 61508-3, 7.4.2.12;

- NOTE The "S" subscript in the above routes designates systematic safety integrity to distinguish it from Route  $1_H$ , and Route  $2_H$  for hardware safety integrity.

- d) the requirements for system behaviour on detection of a fault (see 7.4.8);

- e) the requirements for data communication processes (see 7.4.11).

- **7.4.2.3** Where an E/E/PE safety-related system is to implement both safety and non-safety functions, then all the hardware and software shall be treated as safety-related unless it can be shown that the implementation of the safety and non-safety functions is sufficiently independent (i.e. that the failure of any non-safety-related functions does not cause a dangerous failure of the safety-related functions).

- NOTE 1 Sufficient independence of implementation is established by showing that the probability of a dependent failure between the non-safety and safety-related parts is sufficiently low in comparison with the highest safety integrity level associated with the safety functions involved.

- NOTE 2 Caution should be exercised if non-safety functions and safety functions are implemented in the same E/E/PE safety-related system. While this is allowed in the standard, it may lead to greater complexity and increase the difficulty in carrying out E/E/PE system safety lifecycle activities (for example design, validation, functional safety assessment and maintenance).

- **7.4.2.4** The requirements for hardware and software shall be determined by the safety integrity level of the safety function having the highest safety integrity level unless it can be shown that the implementation of the safety functions of the different safety integrity levels is sufficiently independent.

- NOTE 1 Sufficient independence of implementation is established by showing that the probability of a dependent failure between the parts implementing safety functions of different integrity levels is sufficiently low in comparison with the highest safety integrity level associated with the safety functions involved.

- NOTE 2 Where several safety functions are implemented in an E/E/PE safety-related system then it will be necessary to consider the possibility that a single fault could cause a failure of several safety functions. In such a situation, it may be appropriate to determine the requirements for hardware and software on the basis of a higher safety integrity level than is associated with any one of the safety functions, depending on the risk associated with such a failure.

- **7.4.2.5** When independence between safety functions is required (see 7.4.2.3 and 7.4.2.4) then the following shall be documented during the design:

- a) the method of achieving independence;

- b) the justification of the method.

EXAMPLE Addressing foreseeable failure modes, that may undermine independence, and their failure rates, use of FMECA or dependant failure analysis.

- **7.4.2.6** The requirements for safety-related software (see IEC 61508-3) shall be made available to the developer of the E/E/PE safety-related system.

- **7.4.2.7** The developer of the E/E/PE safety-related system shall review the requirements for safety-related software and hardware to ensure that they are adequately specified. In particular, the E/E/PE system developer shall consider the following:

- a) safety functions;

- b) E/E/PE safety-related system safety integrity requirements;

- c) equipment and operator interfaces.

- **7.4.2.8** The E/E/PE safety-related system design documentation shall specify those techniques and measures necessary during the E/E/PE system safety lifecycle phases to achieve the safety integrity level.

- **7.4.2.9** The E/E/PE safety-related system design documentation shall justify the techniques and measures chosen to form an integrated set that satisfies the required safety integrity level.

- NOTE The adoption of an overall approach employing independent type approval of the E/E/PE safety-related systems (including sensors, actuators, etc) for hardware and software, diagnostic tests and programming tools, and using appropriate languages for software wherever possible, has the potential to reduce the complexity of E/E/PE system application engineering.

- **7.4.2.10** During the design and development activities, the significance (where relevant) of all hardware and software interactions shall be identified, evaluated and documented.

- **7.4.2.11** The design shall be based on a decomposition into subsystems with each subsystem having a specified design and set of integration tests (see 7.5.2).

- NOTE 1 A subsystem may be considered to comprise a single element or any group of elements. See IEC 61508-4 for definitions. A complete E/E/PE safety-related system is made up from a number of identifiable and separate subsystems, which when put together implement the safety function under consideration. A subsystem can have more than one channel (see 7.4.9.3 and 7.4.9.4).

- NOTE 2 Wherever practicable, existing verified subsystems should be used in the implementation. This statement is generally valid only if there is almost 100 % mapping of the existing subsystem or element functionality, capacity and performance on to the new requirement or the verified subsystem or element is structured in such a way that the user is able to select only the functions, capacity or performance required for the specific application. Excessive functionality, capacity or performance can be detrimental to system safety if the existing subsystem or element is overly complicated or has unused features and if protection against unintended functions cannot be obtained.

- **7.4.2.12** When the initial design of the E/E/PE safety-related system has been completed, an analysis shall be undertaken to determine whether any reasonably foreseeable failure of the E/E/PE safety-related system could cause a hazardous situation or place a demand on any

other risk control measure. If any reasonably foreseeable failure could have either of these effects, then the first priority shall be to change the design of the E/E/PE safety-related system to avoid such failure modes. If this cannot be done, then measures shall be taken to reduce the likelihood of such failure modes to a level commensurate with the target failure measure. These measures shall be subject to the requirements of this standard.

NOTE The intention of this clause is to identify failure modes of the E/E/PE safety-related system that place a demand on other risk control measures. There may be cases where the failure rate of the specified failure modes cannot be reduced and either a new safety function will be required or the SIL of the other safety functions reconsidered taking into account the failure rate.

**7.4.2.13** De-rating (see IEC 61508-7) should be considered for all hardware components. Justification for operating any hardware elements at their limits shall be documented (see IEC 61508-1, Clause 5).

NOTE Where de-rating is appropriate, a de-rating factor of approximately two-thirds is typical.

**7.4.2.14** Where the design of an E/E/PE safety-related system includes one or more ASICs to implement a safety function, an ASIC development lifecycle (see 7.1.3.1) shall be used.

#### 7.4.3 Synthesis of elements to achieve the required systematic capability

- **7.4.3.1** To meet the requirements for systematic safety integrity, the designated safety-related E/E/PE system may, in the circumstances described in this section, be partitioned into elements of different systematic capability.

- NOTE 1 The systematic capability of an element determines the potential for systematic faults of that element to lead to a failure of the safety function. The concept of systematic capability of an element is applicable to both hardware and software elements.

- NOTE 2 Subclause 7.6.2.7 of IEC 61508-1 recognises the value of independence and diversity at the level of a safety function and the E/E/PE safety related systems to which it could be allocated. These concepts can also be applied at the detailed design level where an assembly of elements implementing a safety function can potentially achieve a better systematic performance than the individual elements.

- **7.4.3.2** For an element of systematic capability SC N (N=1, 2, 3), where a systematic fault of that element does not cause a failure of the specified safety function but does so only in combination with a second systematic fault of another element of systematic capability SC N, the systematic capability of the combination of the two elements can be treated as having a systematic capability of SC (N + 1) providing that sufficient independence exists between the two elements (see 7.4.3.4).

NOTE The independence of elements can be assessed only when the specific application of the elements is known in relation to the defined safety functions.

- **7.4.3.3** The systematic capability that can be claimed for a combination of elements each of systematic capability SC N can at most be SC (N+1). A SC N element may be used in this way only once. It is not permitted to achieve SC (N+2) and higher by successively building assemblies of SC N elements.

- **7.4.3.4** Sufficient independence, in the design between elements and in the application of elements, shall be justified by common cause failure analysis to show that the likelihood of interference between elements and between the elements and the environment is sufficiently low in comparison with the safety integrity level of the safety function under consideration.

- NOTE 1 For systematic capability, with respect to hardware design, realisation, operation and maintenance, possible approaches to the achievement of sufficient independence include:

- functional diversity: use of different approaches to achieve the same results;

- diverse technologies: use of different types of equipment to achieve the same results);

- common parts/services: ensuring that there are no common parts or services or support systems (for example power supplies) whose failure could result in a dangerous mode of failure of all systems;

- common procedures: ensuring that there are no common operational, maintenance or test procedures.

NOTE 2 Independence of application means that elements will not adversely interfere with each other's execution behaviour such that a dangerous failure would occur.

NOTE 3 For independence of software elements see 7.4.2.8 and 7.4.2.9 of IEC 61508-3.

#### 7.4.4 Hardware safety integrity architectural constraints

NOTE 1 The equation, relating to the hardware safety integrity constraints, are specified in Annex C and the safety integrity constraints are summarized in Table 2 and Table 3

NOTE 2 Clause A.2 of IEC 61508-6 gives an overview of the necessary steps in achieving required hardware safety integrity, and shows how this subclause relates to other requirements of this standard.

In the context of hardware safety integrity, the highest safety integrity level that can be claimed for a safety function is limited by the hardware safety integrity constraints which shall be achieved by implementing one of two possible routes (to be implemented at system or subsystem level):

- Route 1<sub>H</sub> based on hardware fault tolerance and safe failure fraction concepts; or,

- Route 2<sub>H</sub> based on component reliability data from feedback from end users, increased confidence levels and hardware fault tolerance for specified safety integrity levels.

Application standards based on the IEC 61508 series may indicate the preferred Route (i.e. Route  $1_H$  or Route  $2_H$ ).