# Standard Guide for Ionizing Radiation (Total Dose) Effects Testing of Semiconductor Devices<sup>1</sup>

This standard is issued under the fixed designation F1892; the number immediately following the designation indicates the year of original adoption or, in the case of revision, the year of last revision. A number in parentheses indicates the year of last reapproval. A superscript epsilon  $(\varepsilon)$  indicates an editorial change since the last revision or reapproval.

#### INTRODUCTION

This guide is designed to assist investigators in performing ionizing radiation effects testing of semiconductor devices, commonly termed total dose testing. When actual use conditions, which include dose, dose rate, temperature, and bias conditions and the time sequence of application of these conditions, are the same as those used in the test procedure, the results obtained using this guide applies without qualification. For some part types, results obtained when following this guide are much more broadly applicable. There are many part types, however, where care must be used in extrapolating test results to situations that do not duplicate all aspects of the test conditions in which the response data were obtained. For example, some linear bipolar devices and devices containing metal oxide semiconductor (MOS) structures require special treatment. This guide provides direction for appropriate testing of such devices.

## 1. Scope

- 1.1 This guide presents background and guidelines for establishing an appropriate sequence of tests and data analysis procedures for determining the ionizing radiation (total dose) hardness of microelectronic devices for dose rates below 300 rd(SiO<sub>2</sub>)/s. These tests and analysis will be appropriate to assist in the determination of the ability of the devices under test to meet specific hardness requirements or to evaluate the parts for use in a range of radiation environments.

- 1.2 The methods and guidelines presented will be applicable to characterization, qualification, and lot acceptance of siliconbased MOS and bipolar discrete devices and integrated circuits. They will be appropriate for treatment of the effects of electron and photon irradiation.

- 1.3 This guide provides a framework for choosing a test sequence based on general characteristics of the parts to be tested and the radiation hardness requirements or goals for these parts.

- 1.4 This guide provides for tradeoffs between minimizing the conservative nature of the testing method and minimizing the required testing effort.

- <sup>1</sup> This guide is under the jurisdiction of ASTM Committee F01 on Electronics and is the direct responsibility of Subcommittee F01.11 on Nuclear and Space Radiation Effects.

- Current edition approved July 1, 2012. Published September 2012. Originally approved in 1998. Last previous edition approved in 2006 as F1892-06. DOI: 10.1520/F1892-12.

- 1.5 Determination of an effective and economical hardness test typically will require several kinds of decisions. A partial enumeration of the decisions that typically must be made is as follows:

- 1.5.1 Determination of the Need to Perform Device Characterization—For some cases it may be more appropriate to adopt some kind of worst case testing scheme that does not require device characterization. For other cases it may be most effective to determine the effect of dose-rate on the radiation sensitivity of a device. As necessary, the appropriate level of detail of such a characterization also must be determined.

- 1.5.2 Determination of an Effective Strategy for Minimizing the Effects of Irradiation Dose Rate on the Test Result—The results of radiation testing on some types of devices are relatively insensitive to the dose rate of the radiation applied in the test. In contrast, many MOS devices and some bipolar devices have a significant sensitivity to dose rate. Several different strategies for managing the dose rate sensitivity of test results will be discussed.

- 1.5.3 *Choice of an Effective Test Methodology*—The selection of effective test methodologies will be discussed.

- 1.6 Low Dose Requirements—Hardness testing of MOS and bipolar microelectronic devices for the purpose of qualification or lot acceptance is not necessary when the required hardness is 100 rd(SiO<sub>2</sub>) or lower.

- 1.7 *Sources*—This guide will cover effects due to device testing using irradiation from photon sources, such as  $^{60}$ Co  $\gamma$  irradiators,  $^{137}$ Cs  $\gamma$  irradiators, and low energy (approximately 10 keV) X-ray sources. Other sources of test radiation such as

linacs, Van de Graaff sources, Dymnamitrons, SEMs, and flash X-ray sources occasionally are used but are outside the scope of this guide.

- 1.8 Displacement damage effects are outside the scope of this guide, as well.

- 1.9 The values stated in SI units are to be regarded as the standard.

#### 2. Referenced Documents

- 2.1 ASTM Standards:<sup>2</sup>

- E170 Terminology Relating to Radiation Measurements and Dosimetry

- E666 Practice for Calculating Absorbed Dose From Gamma or X Radiation

- E668 Practice for Application of Thermoluminescence-Dosimetry (TLD) Systems for Determining Absorbed Dose in Radiation-Hardness Testing of Electronic Devices

- E1249 Practice for Minimizing Dosimetry Errors in Radiation Hardness Testing of Silicon Electronic Devices Using Co-60 Sources

- E1250 Test Method for Application of Ionization Chambers to Assess the Low Energy Gamma Component of Cobalt-60 Irradiators Used in Radiation-Hardness Testing of Silicon Electronic Devices

- F996 Test Method for Separating an Ionizing Radiation-Induced MOSFET Threshold Voltage Shift Into Components Due to Oxide Trapped Holes and Interface States Using the Subthreshold Current-Voltage Characteristics

- F1467 Guide for Use of an X-Ray Tester (≈10 keV Photons) in Ionizing Radiation Effects Testing of Semiconductor Devices and Microcircuits

- ISO/ASTM 51275 Practice for Use of a Radiochromic Film Dosimetry System

- 2.2 Military Specifications:

- MIL-STD-883, Method 1019, Ionizing Radiation (Total Dose) Test Method<sup>3</sup>

- MIL-STD-750, Method 1019, Steady-State Total Dose Irradiation Procedure<sup>3</sup>

- MIL-HDBK-814 Ionizing Dose and Neutron Hardness Assurance Guidelines for Microcircuits and Semiconductor Devices<sup>3</sup>

# 3. Terminology

- 3.1 For terms relating to radiation measurements and dosimetry, see Terminology E170.

- 3.2 Definitions of Terms Specific to This Standard:

- 3.2.1 accelerated annealing test, n—procedure utilizing elevated temperature to accelerate time-dependent growth and annealing of trapped charge.

- 3.2.2 *category A*, *n*—used to refer to a part containing bipolar structures that is not low dose rate sensitive.

- 3.2.3 *category B, n*—used to refer to a part containing bipolar structures that is low dose rate sensitive.

- 3.2.4 *characterization*, *n*—testing to determine the effect of dose, dose-rate, bias, temperature, etc. on the radiation induced degradation of a part.

- 3.2.5 delayed reaction rate effect (DRRE), n—a time and temperature dependent effect where the rate of degradation for a second irradiation is much greater than the rate of degradation for the first irradiation after a delay time that is dependent on the temperature of the part during the time between the two irradiations.

- 3.2.6 enhanced low dose rate sensitivity (ELDRS), n—used to refer to a bipolar part that shows enhanced (greater) radiation induced damage for a fixed dose at dose rates below about 50  $\rm rd(SiO_2)/s$  compared to damage at the same dose for dose rates of >50  $\rm rd(SiO_2)/s$ . The enhancement may be a result of true dose rate effects or time dependent effects, or both.

- 3.2.7 gray, n—the gray (Gy) symbol, is the SI unit of absorbed dose, defined as 1 Gy = 1 J/kg (1 Gy = 100 rd).

- 3.2.8 *in-flux tests*, *n*—measurements made in-situ while the test device is in the radiation field.

- 3.2.9 *in-situ tests*, *n*—electrical measurements made on devices during, or before-and-after, irradiation while they remain in the irradiation location.

- 3.2.10 in-source tests, n—an in-flux test.

- 3.2.11 *ionizing radiation effects, n*—the changes in the electrical parameters of a microelectronic device resulting from radiation-induced trapped charge.

- 3.2.11.1 *Discussion*—Ionizing radiation effects are sometimes referred to as" total dose effects."

- 3.2.11.2 Discussion—In this guide, doses and dose rates are specified in rd(SiO<sub>2</sub>) as contrasted with the use of rd(Si) in other related standards. The reason is that for ionizing radiation effects in silicon based microelectronic components, it is the energy deposited in the SiO<sub>2</sub> gate, field, and spacer oxides that is responsible for the radiation-induced degradation effects. For high energy irradiation, for example, <sup>60</sup>Co photons, the difference between dose deposited in Si and SiO<sub>2</sub> typically is negligible. For X-ray irradiation, approximately 10 keV photon energy, the energy deposited in Si under some circumstances may be approximately 1.8 times the energy deposited in SiO<sub>2</sub>. For additional details, see Guide F1467.

- 3.2.12 *not in-flux test, n*—electrical measurements made on devices at any time other than during irradiation.

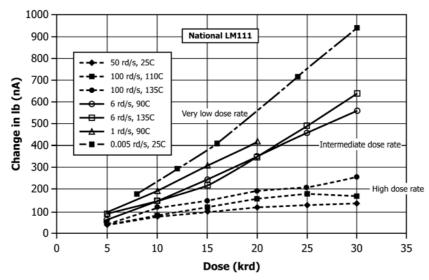

- 3.2.13 *overtest, n*—a factor that is applied to the specification dose to determine the test dose level that the samples must pass to be acceptable at the specification level. An overtest factor of 1.5 means that the parts must be tested at 1.5 times the specification dose.

- 3.2.14 parameter delta design margin (PDDM), n—a design margin that is applied to the radiation induced change in an electrical parameter.

- 3.2.14.1 *Discussion*—For example, for a PDDM of 3 the change in a parameter at a specified dose from the pre-irradiation value is multiplied by three and added to the

<sup>&</sup>lt;sup>2</sup> For referenced ASTM standards, visit the ASTM website, www.astm.org, or contact ASTM Customer Service at service@astm.org. For *Annual Book of ASTM Standards* volume information, refer to the standard's Document Summary page on the ASTM website.

<sup>&</sup>lt;sup>3</sup> Available from the Standardization Documents Order Desk, Building 4, Section D, 700 Robbins Ave., Philadelphia, PA 19111–5094.

pre-irradiation value to see if the sample exceeds the post-irradiation parameter limit. For example, if the pre-irradiation value of  $I_b$  is 30 nA and the post-irradiation value at 20 krd(SiO<sub>2</sub>) is 70 nA (change in  $I_b$  is 40 nA), then for a PDDM of 3 the post-irradiation value would be 150 nA (30 nA + 3 X 40 nA). If the allowable post-irradiation limit is 100 nA the part would fail.

- 3.2.15 *qualification*, *n*—testing to determine the adequacy of a part to meet the requirements of a specific application.

- 3.2.16 *rad*, n—the rad symbol, rd, is a commonly used unit for absorbed dose, defined in terms of the SI unit of absorbed dose as 1 rd = 0.01 Gy.

- 3.2.17 *remote tests*, *n*—electrical measurements made on devices that are removed physically from the irradiation location for the measurements.

- 3.2.18 *time dependent effects (TDE)*, *n*—the time dependent growth and annealing of ionizing radiation induced trapped charge and interface states and the resulting transistor or IC parameter changes caused by these effects.

- 3.2.18.1 *Discussion*—Similar effects also take place during irradiation. Because of the complexity of time dependent effects, alternative, but not inconsistent, definitions may prove useful. Two of these are: the complex of time-dependent processes that alter trapped oxide change  $(\Delta N_{\rm ot})$  and interface trap density  $(\Delta N_{\rm it})$  in an MOS or bipolar structure during and after irradiation; and, the effects of these processes upon device or circuit characteristics or performance, or both.

- 3.2.19 *true dose rate effect, n*—a response that occurs during low dose rate irradiation that cannot be reproduced with a high dose rate irradiation followed by an equivalent time anneal.

## 4. Summary of Guide

- 4.1 This guide is designed to provide an introduction and direction to the purposes, methods, and strategies of total ionizing dose testing.

- 4.1.1 *Purposes*—Device or system hardness may be measured for several different purposes. These may include device characterization, device qualification, lot acceptance, line qualification, and studies of device physics.

- 4.1.2 Methods:

- 4.1.2.1 An ionizing radiation effects test consists of performing a set of electrical measurements on a device, exposing the device to ionizing radiation while appropriately biased, and then performing a set of electrical measurements either during or after irradiation.

- 4.1.2.2 Because several factors enter into the effects of the radiation on the device, parties to the test must establish and agree to a variety of conditions before the validity of the test can be established or before the results of any one test can be compared with those of another. Conditions that must be established and agreed to include the following:

- (a) Radiation Source—The type of radiation source ( $^{60}$ Co, X-ray, etc.) that is to be used.

Note 1—The ionizing dose response of many device types has been shown to depend on the type of ionizing radiation to which the device is subjected. The selection of a suitable radiation source for use in such a test must be based on the understanding that the gamma or electron radiation

source will induce a device response that then should be correlated to the response anticipated in the device application.

- (b) Dose Rate Range—The range of dose rates within which the radiation exposures must take place (see 6.4).

- Note 2—The response of many devices has been shown to be highly dependent on the rate at which the dose is accumulated. There must be a demonstrated correlation between the response of the device under the selected test conditions and the rate at which the device would be expected to accumulate dose in its intended application.

- (c) Operating Conditions—The test circuit, electrical biases to be applied, and the electrical operating sequence, if applicable, for the part during irradiation (see 6.3). This includes the use of in-flux or not in-flux testing.

- (d) Electrical Parameters—The measurements that are to be made on the test devices before, during (if appropriate), and after (if appropriate) irradiation.

- (e) *Time Sequence*—The exposure time, the elapsed time between exposure and post-exposure measurements, and the time between irradiations (see 6.5).

- (f) Irradiation Levels—The dose(s) to which the test device is to be exposed between measurements (see Practice E666).

- (g) Dosimetry—The dosimetry technique (TLDs, calorimeters, diodes, etc.) to be used. This depends to some extent on the radiation source selection.

- (h) Temperature—Exposure, measurement, and storage temperature ranges (see 6.5 and 6.6).

- (i) Experimental Configuration—The physical arrangement of the radiation source, test unit, radiation shielding, and any other mechanical or electrical elements of the test.

- (j) Accelerated Annealing Testing for MOS—The accelerated annealing tests called for in 8.2.2.3 (a) through (e) should be performed for hardness assurance testing of any device that contains MOS elements by design. Further requirements and exceptions to such accelerated annealing testing may be made based on the factors discussed in Appendix X1.

- (k) Special Testing for Linear Bipolar—The special testing procedures called for in 8.1.2.1 through 8.1.2.5 and 8.2.3.1 through 8.2.3.4 should be performed for hardness assurance testing of linear bipolar devices. Further requirements and suggestions for the testing of linear bipolar devices will be found in Appendix X2.

- 4.1.3 Strategies—Several kinds of strategies may prove useful for device testing. The strategy used will depend on the key impediments to accurate, repeatable, and inexpensive testing. For example, it may be useful to measure device properties at several different dose rates and then to extrapolate to the results expected at the actual dose rate anticipated in use. Then again, it may be more efficient to devise a method that will place an upper or lower bound on the excursions that may be anticipated for a given device parameter.

- 4.2 The choice of optimal procedures for the performance of total ionizing dose testing typically involves resolution of the conflicts between the following four competing requirements:

- 4.2.1 *Test Fidelity*—It is necessary that a test reproduce the results to be expected in the projected application environment to an acceptable degree of precision. The test methodology chosen has a strong effect on the precision of the result. Typically, however, greater test fidelity must be balanced

against greater cost. In addition, many environments cannot be reproduced in the laboratory. Often it may be necessary to have an adequate command of device physics in order to devise laboratory tests that adequately match or bound the performance to be expected in actual use.

- 4.2.2 Reproducibility—It is important to have test procedures that can be depended upon to give approximately the same result each time when used by different laboratories. Failure to achieve this goal may have significant contract implications. Obtaining this goal typically requires careful attention to the control of experimental variables and to the development of accurate dosimetry methods.

- 4.2.3 Single-Valued Result—For some purposes, it is desirable to have a test that can be used to simply categorize parts and that gives one answer for each part. For example, labeling of parts for the military parts system is facilitated if such a characterization is available. On the other hand, the search for a simple characterization scheme must not be allowed to obscure real dependencies on dose rate, temperature, bias, etc., which may have a significant effect on operational hardness. Care must be taken to extrapolate appropriately from the conditions that lead to the test rating to those conditions to be expected in use.

- 4.2.4 *Testability*—It is, of course, desirable to obtain a test that is economical in its use of time, equipment, and personnel. The perfect test typically will be too expensive to perform. The goal is to determine an optimal balance between expense and reliability of results.

# 5. Significance and Use

- 5.1 Electronic circuits used in space, military, and nuclear power systems may be exposed to various levels of ionizing radiation. It is essential for the design and fabrication of such circuits that test methods be available that can determine the vulnerability or hardness (measure of nonvulnerability) of components to be used in such systems.

- 5.2 Some manufacturers currently are selling semiconductor parts with guaranteed hardness ratings. Use of this guide provides a basis for standardized qualification and acceptance testing.

## 6. Interferences

- 6.1 There are many factors that can affect the results of ionizing radiation tests. Care must be taken to control these factors to obtain consistent and reproducible results. Several of these factors are discussed as follows:

- 6.2 Energy Spectrum—Many gamma-ray sources have associated low-energy electron and photon components that result from interaction of the gamma radiation with shielding surrounding the source (see Practice E1249). These low-energy components can deposit their energy in a shallow layer near the surface of the device chip. This places an absorbed dose in the most susceptible region of a test device that can be much higher than the dose measured by a monitoring dosimeter, typically the average dose deposited in the dosimeter material. The severity of the effects is very dependent on the radiation source being used and the geometry of the test configuration.

6.3 Bias—Most ionizing radiation effects are related to the post irradiation net trapped charge in the device dielectric layers, usually oxides, and to the interface traps at the dielectric-semiconductor interface. These effects often are dependent strongly on the electrical field in the dielectric during and after exposure (see Test Method E1250). In general, the largest effect for the net trapped charge occurs for a large positive electric field in the dielectric during irradiation. For the interface trap build-up, the worst case condition most often is a small electric field during irradiation and a large positive field after irradiation. Radiation testing typically is performed under worst-case bias conditions. For many circuits, the worst-case bias is a static dc bias with the supply voltages at their maximum rated voltage. The determination of the worst case bias for the input/output lines and internal nodes of any given circuit often is a complex process of circuit analysis or characterization tests, or both, under many bias conditions. Some guidance is given in the appendices for methods to determine the worst case irradiation and anneal bias. For complementary metal-oxide semiconductor transistor (CMOS) components, see Appendix X1; for bipolar components, see Appendix X2; and, for application-specific integrated circuits, (ASIC) see Appendix X3. The irradiation bias conditions selected for any component should not exceed the manufacturer's maximum ratings or place the component in a configuration that is unrealistic for a system application.

Note 3—Lacking information on worst-case application conditions, preliminary analysis and characterization tests should be performed to determine worst-case conditions. In performing step-wise irradiations, it is important to minimize the changes taking place between exposures so that measurements at each level accurately reflect the effects of the cumulative dose to which the device was exposed. Minimum parameter changes generally take place between exposures if the device pins are kept shorted. Bias should not be changed from one level to another in a step stress sequence, in order to avoid charge neutralization effects.

Note 4—Some space applications involve devices used at very low repetition rates; for example, electrically programmable read-only memory (EPROMs.) Another example is redundant devices and circuits that ride along in an unbiased condition until they are switched on. Still another example is sensor circuits that only are biased on when a measurement is to be taken. Thus, it may be desirable to characterize and test these devices in an unbiased condition. Ionizing dose survival levels may be three to ten times higher in the unbiased condition than under typical bias conditions.

## 6.4 Dose Rate:

- 6.4.1 The concentration of excess carriers depends on the dose rate. High densities of excess carriers can affect the charge state of trapping levels, as well as the mobilities and lifetimes of these carriers resulting in altered post-radiation densities and distributions of trapped charge.

- 6.4.2 Photocurrents produced by the excess carriers generated by ionization can alter internal bias levels of a semiconductor chip, thereby causing a variation in the response of the device or circuit.

- 6.4.3 Because of the counteracting effects of charge annealing and interface state growth in some MOS device oxides, the dose rate at which a test is carried out can have a strong effect on the apparent device hardness (see 6.5 for further detail).

- 6.4.4 For the reasons noted in 6.4.1 6.4.3, the dose rate to be used in an ionizing radiation test must be established and agreed upon between the parties to the test and controlled

during the test. Selection of appropriate dose rate ranges should be based on the radiation environments anticipated for the parts while in actual system operation.

6.4.5 The use of thick absorbers in order to produce a low dose-rate <sup>60</sup>Co test source must be used with caution. The absorbers may cause softening of the spectrum (through Compton scattering). This may cause dose deposition and dose enhancement problems (see 6.2).

# 6.5 Time Dependent Effects:

# 6.5.1 Time Dependent Effects for MOS Devices:

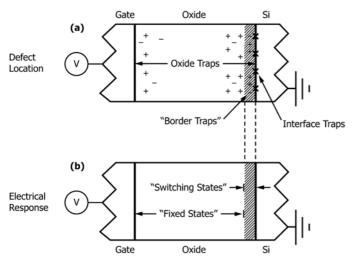

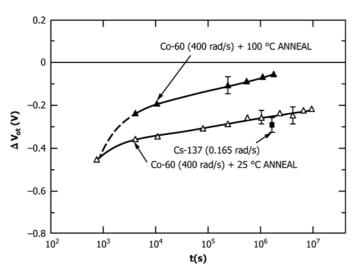

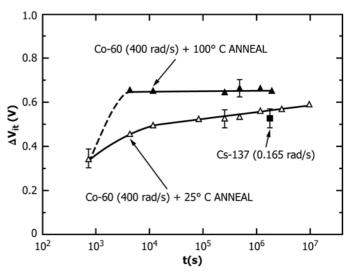

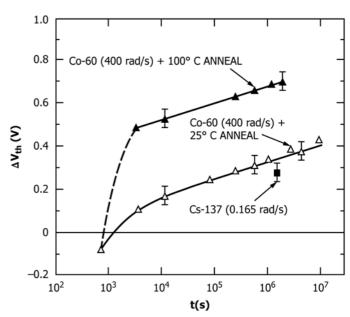

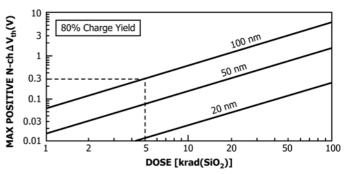

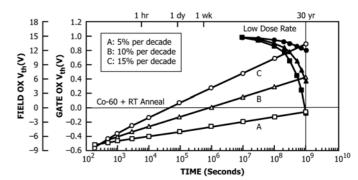

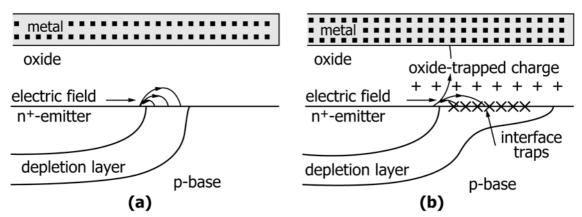

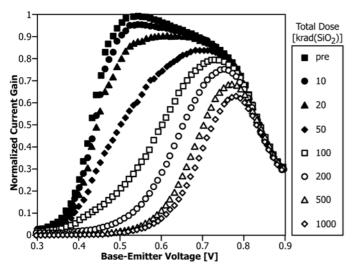

6.5.1.1 Ionizing irradiation of MOS devices results in two major species of defects: trapped holes in gate (and field) oxides and interface states at  $Si-SiO_2$  interfaces. Hole trapping occurs rapidly (typically less than  $\sim 1$  s) and often anneals significantly in hours or days. Interface state density builds up slowly (in seconds to days) and does not usually anneal significantly at room temperature. The relative magnitudes of these defects determine the effects on operation of the device and its post-irradiation time dependence. The quality of the oxide determines the relative densities and saturation levels of the defects.

6.5.1.2 Trapped holes in the silicon oxide result in a negative shift in the gate threshold voltage for both n- and p-channel devices. Interface states maintain a net negative charge in n-channel devices (positive gate threshold shift) and a net positive charge in p-channel devices (negative gate threshold shift). See Test Method F996.

6.5.1.3 With increasing time, trapped holes are removed or compensated while interface state concentrations increase. Because hole trapping occurs rapidly, initial gate threshold shifts in both p- and n-channel devices are negative under irradiation at moderate to high dose rates. As time passes, the gate threshold shift of n-channel devices becomes less negative, and, if interface states build up sufficiently, can eventually become positive. Whether p-channel gate shifts become more or less negative with time depends on the relative rates of formation of interface states and the removal of trapped holes, but the shift always remains negative.

6.5.1.4 The interaction of these competing effects that shift with time cause the sometimes complex time dependent behavior of MOS parts following irradiation. This complex behavior explains observed effects once thought anomalous: reverse annealing, in which parts continue to degrade with time following cessation of irradiation; the rebound effect, in which *n*-channel devices super-recover past their preirradiation gate threshold values and can fail due to a positive gate threshold shift; dose rate effects where parts show little change at a particular dose rate but show a significant response at either higher or lower dose rates (because at the intermediate dose rate the net oxide-trapped charge buildup is balanced by interface buildup); etc.

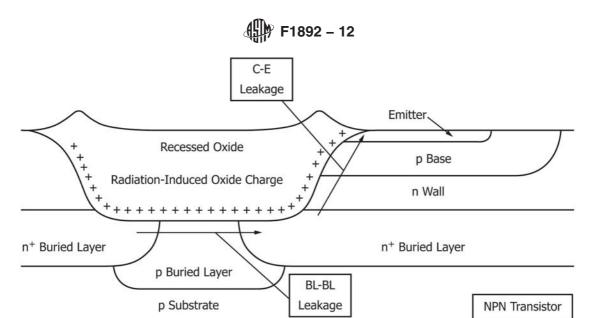

## 6.5.2 Time Dependent Effects for Bipolar Devices:

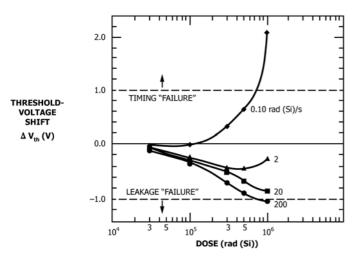

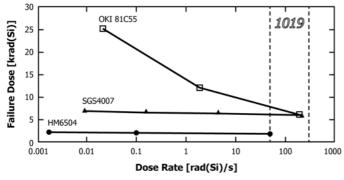

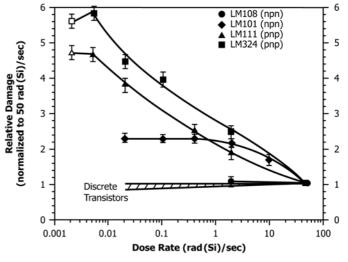

6.5.2.1 The crux of the bipolar TDE issue concerns the properties of field oxides used to isolate the base and emitter contacts. These oxides typically are of poor quality. The effects of radiation on such oxides determine the radiation response of many bipolar transistors. A characteristic failure mechanism in such bipolar transistors is radiation-induced increase in the

base current, and resulting decrease in transistor gain. This excess base current largely is caused by enhanced surface recombination current in the emitter-base diode.

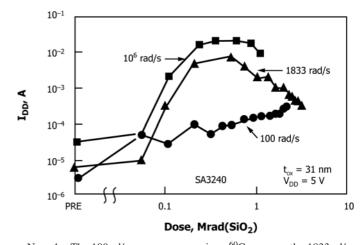

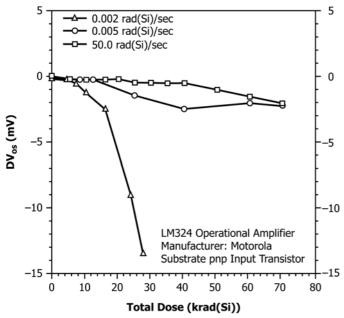

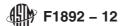

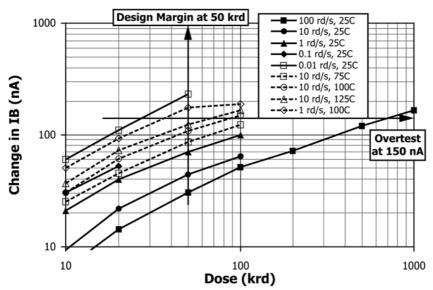

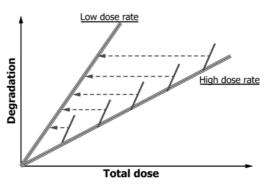

6.5.2.2 For the bipolar technologies mentioned above, failures occur at lower doses for irradiations at low dose rates than at higher rates. For example, the devices may show higher excess base currents below 1 rd(SiO<sub>2</sub>)/s than at 100 rd/(SiO<sub>2</sub>)/s, for the same level of accumulated total ionizing dose. Such enhanced failure at low dose rates has been observed both in modern bipolar technologies and in relatively old designs. These effects have been observed both in transistors and ICs.

6.5.2.3 There are at least two types of enhanced low-dose-rate effects that have been characterized extensively, true dose rate effects and time dependent effects. Many low-dose-rate sensitive bipolar linear circuits have shown both types of enhanced low-dose-rate effects. In addition there is a delayed reaction rate effect described in the work of Freitag and Brown (see Refs (1, 2))<sup>4</sup> that results in an increased rate of degradation if the circuit is being irradiated at the time the interface state "precursors" arrive at the Si-SiO<sub>2</sub> interface. This arrival time is temperature dependent and for some circuits is on the order of several hundred thousand seconds at room temperature and about ten thousand seconds at 100°C. This mechanism has only been characterized on two circuit types to date.

6.5.2.4 The true dose rate effects cannot be simulated by accelerated anneal procedures, such as that recommended for MOS devices in 8.2.2.3 (a) through (e) and Appendix X1. Currently, there is no proven single universal method for accelerating the testing of low dose-rate irradiation for all types of dose-rate sensitive bipolar devices. Some promising test methods, however, are described in Appendix X2.

# 6.6 Temperature:

6.6.1 Because time-dependent effects (see 6.5) may be thermally-activated processes, the temperatures at which radiation, measurements, and storage take place can affect parameter values. It is recommended that all radiation exposures, measurements, and storage be done at  $24 \pm 6^{\circ}\text{C}$  unless another temperature range is called out specifically in the test or is agreed upon between the parties to the test. If devices are to be transported to and from a remote electrical measurement site, the temperature of the devices shall not be allowed to increase by more than  $10^{\circ}\text{C}$  from the radiation-environment temperature.

6.6.2 When the post irradiation electrical measurements are made at a location remote from the radiation source the irradiated parts may be stored at a temperature  $\leq$ 60°C (using dry ice) to increase the time between the end of irradiation and the beginning of electrical testing. The requirements for using this option are detailed in Section 8.

6.6.3 Many device parameters are temperature sensitive. To obtain accurate measures of the radiation-induced parameter changes, the temperature must be controlled.

6.6.4 Temperature effects also must be considered in establishing the sequence of post-irradiation testing. The sequence of parameter measurements should be chosen to allow lowest

<sup>&</sup>lt;sup>4</sup> The boldface numbers in parentheses refer to the list of references at the end of this standard.

power dissipation measurements to be made first. Power dissipation may increase with each subsequent measurement. When high power is to be dissipated in the test devices, pulsed measurements are required to minimize the temperature excursions.

- 6.7 *Handling*—As in any other type of testing, care must be taken in handling the parts. This applies especially to parts that are susceptible to electrostatic discharge damage.

- 6.8 *Delidding*—For some testing, it is necessary to de-lid the devices prior to irradiation and testing. Care must be taken to make proper allowance for the effects of such a process.

- 6.9 Radiation Damage:

- 6.9.1 If a test fixture is used over a long period of time, components of the fixture can be damaged by exposure to the ionizing radiation, causing an impact on the test results. Such fixtures should be checked regularly for socket or printed circuit board leakage and for degradation of any peripheral components used in the test. Current leakage between pins or wires shall not be allowed to approach levels that interfere with accurate parameter measurements.

- 6.9.2 Ionizing radiation causes the introduction of color centers in optical materials, seriously degrading light transmission properties. Much of the radiation damage to devices containing optical elements may be due to this effect rather than to damage of the semiconductor elements. Such damage to the device under test or to test circuitry is outside the scope of this guide.

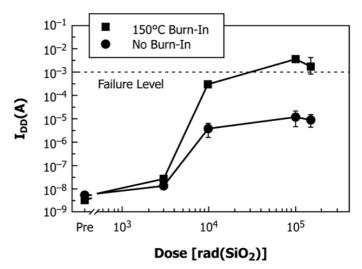

- 6.10 *Burn-In*—Burn-in is a set of elevated-temperature biased anneals required by reliability testing and the system application. For some devices, there is a significant difference in the radiation response before and after burn-in. Unless it has been shown by characterization testing that burn-in has no effect on radiation response, then either characterization and qualification testing must be performed on devices that have been exposed to all elevated-temperature biased (or unbiased) anneals required by reliability testing and the system application, or the results of characterization and qualification testing must be corrected for the changes in radiation response that would have been caused by elevated temperature anneals (such as burn-in). This correction shall be performed in a manner acceptable to the parties to the test.

- 6.11 Test Sample Size—There is a difficult trade-off in deciding the number of devices to use for a particular test. Using a large number may in some cases be prohibitively expensive. Then again, the reliability of a test result may be unacceptably low if too small a sample size is used. This outcome results from part-to-part variability within a given test lot. The sample sizes specified in this guide are accepted generally in the industry.

# 7. Apparatus

- 7.1 Radiation Sources Used for Ionizing Radiation (Total Dose) Effects Testing:

- 7.1.1 Sources typically used for characterization, qualification and lot acceptance testing include <sup>60</sup>Co and <sup>137</sup>Cs isotopes (mounted in pool sources, pop-up sources, and fully shielded

- irradiators), and low energy (approximately 10 keV photon energy) X-ray sources.

- 7.1.1.1 Each source can be used satisfactorily for such tests, and the differences in the results from using different sources or kinds of sources should be negligible provided that dose rates can be matched or deemed to have no significant impact on the devices being tested.

- 7.1.1.2 The radiation environment impinging on the tested device must be characterized in terms of photon energy spectrum and dose rate. In situations where the photon energy spectrum impinging on the device is not or cannot be well defined, but is suspected to contain low energy components that promote absorbed dose enhancement, a filter box such as the lead-aluminum structure (see 7.1.2.1 and Practice E1249) can be incorporated into the radiation test environment to harden the photon spectrum.

- 7.1.2 The following radiation sources may be used to support ionizing radiation effects testing:

- 7.1.2.1 60 Co—The most commonly used source for ionization radiation (total dose) effects testing is 60Co. Gamma rays with energies of 1.17 and 1.33 MeV are the primary ionizing radiation emitted by <sup>60</sup>Co (see 6.2). In exposures using <sup>60</sup>Co sources, test specimens must be enclosed in a lead-aluminum container to minimize dose enhancement effects caused by low-energy scattered radiation. A minimum of 1.5 mm of lead surrounding an inner shield of 0.7 to 1.0 mm of aluminum is required. This lead-aluminum container produces an approximate charged particle equilibrium for silicon devices with some attenuation of the gamma rays. Because of this attenuation, the gamma ray intensity inside the container shall be calibrated initially, whenever sources are changed, and each time the source, container, or test fixture orientation or configurations are changed. This measurement shall be performed by placing a dosimeter, for example a TLD, in the device irradiation container at the approximate position of the test device (see Practice E1249).

- 7.1.2.2 <sup>137</sup>Cs—Radiation sources based on <sup>137</sup>Cs can be used for characterization testing in much the same way as <sup>60</sup>Co sources. The lead-aluminum box used for <sup>137</sup>Cs testing will require adjustment of the lead and aluminum thickness because of the lower energy of the gamma rays.

- 7.1.2.3 A special case of radioactive source testing, for example, <sup>60</sup>Co sources and <sup>137</sup>Cs sources, is to support very low dose rate testing, that is, <1 rd/s. The use of attenuation to obtain a low dose rate, for example the use of lead bricks or sheet, can add a significant low energy component to the radiation due to Compton scattering. The radiation effects of such a softened beam may be significantly different than those of the unattenuated beam. See Practice E1249 for additional discussion. Special care is required to support such testing.

- 7.1.2.4 Low Energy X-Ray Source—Low energy (approximately 10 keV photon energy) X-ray sources commonly are used for transistor characterization. Because of the low penetration of such photons, devices must be tested prior to packaging or be delidded for testing. For additional detail, see Guide F1467.

- 7.2 *Bias Circuit*—The bias circuit may be simple or complex, depending on the part type and testing requirements.

Good commercial design and fabrication practices should be used to prevent oscillations, minimize leakage currents, prevent device damage, and support accurate and repeatable measurements. For test fixtures holding several devices, isolation should be used between devices so that a failure of one device will not impact the other test units. For in-situ measurements, provision must be made for switching individual devices between the radiation bias circuit and the test instrumentation used for pre- and post-irradiation parameter measurements. For remote measurements, MOS and bipolar parts should be maintained with shorted leads during transport.

7.3 Test Instrumentation—Various instruments for device parameter measurement may be required. Depending upon the device to be tested, these can range from simple broadboard circuits to complex IC test systems. All equipment is to be in calibration and of suitable stability and accuracy.

# 7.4 Dosimetry System:

7.4.1 Determination of Absorbed Dose—Determining the absorbed dose in a semiconductor device requires a knowledge of the elemental composition and geometrical structure of the materials involved, the appropriate tabulated mass energy-absorption coefficients ( $\mu_{en}/\rho$ ), the energy spectrum of the radiation field (not merely that of the unperturbed radiation source, in which the exposure is conducted), and a related measurement based on a dosimeter whose response is well defined in the particular radiation field of interest.

7.4.2 For <sup>60</sup>Co irradiation systems, dosimetry most often is performed using thermoluminescent dosimeters (TLDs) to measure the dose inside the lead-aluminum container delivered in a fixed time period. Other dosimeters, such as cobalt glass, radiochromic dye dosimeters (see ISO/ASTM 51275), or ion chambers, however, can be used. This measurement is used to establish the dose rate for the geometry used. Once the dose rate is established, preselected radiation levels are attained by irradiating for the proper time period. TLDs also may be used with any of the other radiation sources. Dosimeter systems can be calibrated through a service of the NIST.<sup>6</sup> Proper use of TLD systems is described in Practice E668.

7.5 Irradiation Temperature Chamber—Ionizing radiation effects testing may require the use of an elevated temperature irradiation chamber if determined through characterization testing. The chamber should be capable of maintaining a circuit under test at up to 150°C while it is being irradiated. The chamber should be capable of raising the temperature of the circuit under test from room temperature to the irradiation temperature within a reasonable time prior to irradiation and cooling the circuit under test from the irradiation temperature to room temperature in less than 20 minutes following irradiation. The irradiation bias shall be maintained during the heating

and cooling. The method for raising, maintaining and lowering the temperature of the circuit under test may be by conduction through a heat sink using heating and cooling fluids, by convection using forced hot and cool air, or other means that will achieve the proper results. Elevated temperature irradiation is intended for use in characterizing bipolar circuits and devices for low-dose-rate sensitivity (see 8.1.2.5).

#### 8. Procedure

#### INTRODUCTION

This section provides guidance for characterization testing and for hardness assurance acceptance testing.

Note 5—Hardness assurance refers to part qualification and lot/process quality conformance.

Note 6—Semiconductor Devices and Integrated Circuits with Intended Use at Dose Rates above 300 rd ( $SiO_2$ )/s—For some strategic and possibly some tactical military applications, the ionizing dose response of many semiconductor devices can be non-monotonic with the severity of non-monotonic behavior depending strongly on both ionizing dose and dose rate. This problem can occur for ionizing dose in the prompt pulse resulting from a nuclear explosion. Parameters, such as leakage currents and current gain, may reach failure levels during the pulse and return to passing levels shortly after the pulse. The time during which the parameters are above failure level may cause system failure even though they return to passing levels after a short period of time. Hardness assurance testing for these parts is discussed in Appendix X1.

- 8.1 Characterization Testing—Characterization testing is performed for the purpose of part selection, determination of sensitivity to dose rate or time dependent effects, categorization for hardness assurance, or to determine the specific nominal worst case test conditions for hardness assurance testing.

- 8.1.1 MOS Devices and Integrated Circuits with Intended Use At Dose Rates At or Below 300 rd(SiO<sub>2</sub>)/s—Parts in this category are those intended for use in, for example, space systems, some tactical military systems, some nuclear power plant electronics or associated robotics, and high energy particle accelerator detectors.

- 8.1.1.1 Parties to the test must first establish the conditions of the test. These conditions should be stated in a test plan as follows:

- (a) Development of the Test Plan—As a minimum, the following conditions should be specified: test approach (step-stress or continuous), test type (in-flux, in-situ, or remote), irradiation source, total dose levels for electrical measurements (for step-stress), dose rate(s), irradiation bias(es), irradiation temperature(s), anneal bias(es), anneal temperature(s), anneal times, and use of test structures (where appropriate). In addition, it may be appropriate to specify date code information for the test devices (that is, limitations on the number of diffusion furnace lots or time to assemble date code lot, or both). All of the possible interferences listed in Section 6 must be considered when making these decisions.

- (b) Dose Rate—The dose rate for the test shall be selected from one of the following possibilities:

- (1) Standard Dose Rate, Condition A—Unless otherwise specified, the dose-rate range shall be between 50 and 300 rd( $SiO_2$ )/s. The dose rates may be different for each radiation dose level in a series; however, the dose rate shall not vary by more than  $\pm 10$  % during each irradiation.

<sup>&</sup>lt;sup>5</sup> See, for example, Hubbell, J.H. and Seltzer, S.M. "Tables of X-Ray Mass Attenuation Coefficients and Mass Energy-Absorption Coefficients, 1 keV to 20 MeV for Elements Z = 1 to 92 and 48 Additional Substances of Dosimetric Interest," *NISTIR* 5632, May 1995. Available from Ionizing Radiation Division, Physics Laboratory, National Institute of Standards and Technology, Technology Administration, U.S. Department of Commerce, Gaithersburg, MD 20899.

<sup>&</sup>lt;sup>6</sup> To schedule calibration services, contact Center for Radiation Research, Radiation Physics Building, National Institute of Standards and Technology (NIST), Gaithersburg, MD 20899.

- (2) Condition B—As an alternative, the test may be performed at the dose rate of the intended application if this is agreed to by the parties to the test.

- (3) Condition C—As an alternative, if the maximum dose rate is  $< 50 \text{ rd}(\text{SiO}_2)$ /s in the intended application, the parties to the test may agree to perform the test at a dose rate  $\geq$  the maximum dose rate of the intended application.

- (4) Condition D—To meet unusual requirements and if agreed upon between the parties to the test, a dose rate that fits none of the above conditions may be used.

- (c) Sample Selection—The sample size for each unique set of test conditions should be at least five and preferably larger. The total population from which the test sample is drawn will depend on the purpose of the characterization. For example, if the parts are to be used in a system, the population should be representative of the parts that will be used for flight hardware, that is, single wafer, single process lot, single date code, or multiple lots. If multiple lots are allowed, as a minimum the test sample should contain parts from at least three date codes or process lots. Control devices from the same population as the test samples should be employed to monitor repeatability of electrical test parameters.

- (d) Development of Test Matrix—For many of the test conditions there will be several values, for example, two or more irradiation biases, two or more dose rates, two or more annealing temperatures. If all of these test conditions are to be exercised with respect to all of the others, that is, a full factorial matrix, then the total sample size (for a minimum sample of five for each element) may be unmanageable. In this case, it is recommended that a reduced matrix be used. Best engineering judgment must be used in selecting the most important test parameters to emphasize. The test matrix should be included in the test plan.

- 8.1.1.2 Start with the first element (unique set of test conditions) in the test matrix. Prepare bias fixtures, test fixtures, test circuits (or test equipment), and test programs.

- 8.1.1.3 Perform dosimetry, including dose mapping of the entire device irradiation area, if recent data for such measurements are not available. For <sup>60</sup>Co irradiation, the dosimetry must be performed inside the lead-aluminum shield box (Section 7). Determine appropriate factors to convert dose in the dosimeter to dose in the device under test using Practice E666.

- (a) As an exception to 8.1.1.3, the lead-aluminum shield box, may be omitted for the dosimetry and the subsequent test sample irradiations under appropriate circumstances. In order to make this omission, it must be demonstrated that dose enhancement inside the test sample package is negligible for the irradiation source being used (see Test Method E1250).

- 8.1.1.4 If the devices are being tested in-flux using the continuous irradiation approach, place the devices in the irradiation test circuit inside the lead-aluminum shield box, if used, and initiate the test circuit. Record the preirradiation parameter, or functional measurements, or both. Begin irradiating the parts at the prescribed dose rate and continue to monitor the electrical parameters/functionality of the devices, either continuously or at the prescribed time intervals, until the final dose level is reached or the parts become nonfunctional.

Assure that all electrical data are time stamped so that the total dose levels for each set of measurements may be calculated.

- 8.1.1.5 If the devices are being irradiated using the stepstress approach, begin by making preirradiation parameter, or functional measurements, or both. Place the parts in the irradiation bias fixture in the lead-aluminum shield box, if used, and irradiate to the first total dose level. Perform the post irradiation electrical measurements either in-situ or at a remote site. If testing is remote, the parts should be transported to and from the test equipment with shorted leads. Conductive foam may be used to accomplish this shorting. Replace the parts in the irradiation bias fixture and irradiate to the next total dose level, following the same procedure just described, until the final level is reached. The time between irradiation and test and the time between irradiations should be minimized and recorded. The time between irradiation and test and the time between irradiations may be extended if the parts are maintained at ≤60°C (using dry ice) or if the dose rate for the test is significantly lower than for Condition A testing [50-300 rd(SiO<sub>2</sub>)/s]. When using dry ice to cool the parts, the time between irradiation and electrical test may be extended up to 72 h and the time between irradiations up to 120 h. When testing at dose rates lower than 50-300 rd(SiO<sub>2</sub>)/s the time between irradiation and test may be 10 % of the incremental irradiation time (or 1 h, whichever is greater) and the time between irradiations may be 20 % of the incremental irradiation time (or 2 h, whichever is greater). See MIL-STD-883, Test Method 1019 for details.

- 8.1.1.6 Following the final irradiation, post-irradiation annealing measurements shall be made if required by the test plan. Annealing measurements usually are made using a step-stress approach. Time zero for the annealing should be set immediately following the final postirradiation electrical characterization or when bias is applied (for biased anneals). Annealing may be performed at room temperature or at an elevated temperature as prescribed by the test plan. All electrical measurements shall be made at room temperature (24  $\pm$  6°C) unless otherwise specified by the test plan. See the following for use of an accelerated annealing procedure:

- (a) For details of the use of an accelerated annealing procedure to simulate space-level low dose rate effects, see 8.2.2.3, (a) through (f). Such a procedure may be required for hardness assurance testing. It also may be performed for characterization testing if prescribed by the test plan. Additional guidance may be found in Appendix X1.

- (b) If the anneals are to be performed at room temperature, the test devices shall be placed in the anneal bias fixture, the bias applied, and the parts left for the prescribed period. The parts then shall be characterized electrically either in-situ or at a remote site. Transport to and from a remote test site shall be with shorted leads. Conductive foam may be used to accomplish this shorting. This procedure shall be repeated until the final anneal time prescribed by the test plan is reached. The time between anneal and electrical characterization and the time between anneals shall be minimized and recorded. The temperature of the anneal shall be recorded.

- (c) If the anneals are to be performed at an elevated temperature, the test devices shall be placed in the anneal bias

test fixture inside the environmental chamber, the bias applied, and the temperature rapidly brought to the anneal temperature and maintained for the first anneal time. The temperature then shall be reduced rapidly to room temperature while maintaining bias, and the parts characterized electrically, either in-situ, or at a remote test site, as prescribed in the test plan. If the testing is to be performed at a remote site, the parts shall be transported to and from the anneal chamber with shorted leads. Conductive foam may be used to accomplish this shorting. This procedure shall be repeated until the final elevated temperature anneal time prescribed by the test plan is reached. The elevated temperature anneal time shall be calculated without regard to time at room temperature during test sequences. The time between anneal and electrical characterization and the time between anneals shall be minimized and recorded.

- 8.1.1.7 The procedures described in 8.1.1.2 8.1.1.6 shall be repeated for each element of the matrix.

- 8.1.2 Bipolar Devices and Integrated Circuits with Intended Use at Dose Rates At or Below 300 rd(SiO<sub>2</sub>)/s—Parts in this category are those intended for use in, for example, space systems, some tactical military systems, nuclear power plants or associated robotics, and high energy particle accelerator detectors.

#### 8.1.2.1 Dose Rate Sensitivity:

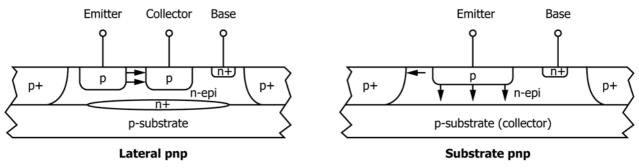

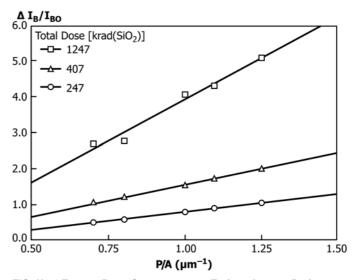

(a) It has been demonstrated that several bipolar linear circuits exhibit an increased rate of degradation at low dose rates (see X2.2.3). The effect is such that if we compare gain degradation for two cases: at the end of a low dose rate exposure, and at the end of a high dose rate exposure to the same dose, followed by a room temperature anneal for the same time as it takes for the low dose rate exposure, the gain degradation for first case can be much greater. This effect will be referred to as "dose rate sensitivity."

Note 7—Low dose rate sensitivity on discrete bipolar transistors has not yet been observed to be greater than a factor of two. Also, it has not been observed on any type of MOS transistor while under normal operating bias with one exception (3).

- (b) The first concern for characterization testing for bipolar parts is to identify low dose rate sensitive parts. Parts which are not low dose rate sensitive are classified as Category A Parts and parts which are low dose rate sensitive are classified as Category B Parts. A set of tests to determine whether a device-under-test is Category A or Category B is described in 8.1.2.2. This ELDRS screen test may not be used to ensure that the part is a Category A part. To establish that a part is Category A it must be demonstrated by characterization testing as described in 8.1.2.4 or analysis based on design and process technology. If previous testing on the same or similar parts has indicated that these parts are low dose rate sensitive, the devices-under-test may, with the agreement of the parties to test, be classified as Category B and the tests of 8.1.2.2 may be skipped.

- (c) Testing Parts Which Are Not Low Dose Rate Sensitive—For parts that are not low dose rate sensitive, the characterization testing may be performed at the standard dose rate of 50 to 300  $\text{rd}(\text{SiO}_2)$ /s (see 8.1.1.1 (b) (1)).

- (d) Testing Parts Which Are Low Dose Rate Sensitive:

- (1) Low dose rate sensitive parts may be tested at the dose rate of the intended application; however, this often may be impractical.

- (2) For low dose rate applications, in many cases it will be desirable to use an accelerated testing method; that is, a test method that provides a conservative measure of low dose rate part response while irradiating at a dose rate well above that expected in the intended application. Some combination of overtest, elevated temperature irradiation and anneal, can bound the low dose rate response for many low dose rate sensitive parts. If a part is low dose rate sensitive and is to be used in a low dose rate application, the determination of an appropriate accelerated test method for a given test typically will involve characterization over a range of dose rates to select test procedures that will bound the low dose rate response.

Note 8—Based on transistor and base oxide capacitor tests, initial studies of the mechanisms of the low dose rate sensitivity have suggested that an elevated temperature irradiation at 1-10 rd(SiO<sub>2</sub>)/s can produce comparable damage to a low dose rate exposure in some cases. Also, it has been shown that an extended room temperature anneal following high dose rate irradiation may result in additional degradation in some circuits, particularly those which fail from gain degradation in a substrate or lateral pnp. Several other accelerated test methods are discussed in Appendix X2.

8.1.2.2 Test to Determine Low Dose Rate Sensitivity— Before proceeding with the full characterization testing, a preliminary screen test should be run to determine whether the bipolar part has enhanced degradation at low dose rates, unless the dose rate sensitivity already has been determined through previous testing or analysis. This test is to be used only to identity those parts which are low dose rate sensitive and not as a test to ensure that a part does not have enhanced low dose rate sensitivity. This preliminary test should be run on all bipolar microcircuits which contain linear circuitry and any discrete or digital part which is suspected of being dose rate sensitive (see Appendix X2 for discussion). Select a minimum random sample of 21 circuits from a population representative of recent production runs. Smaller sample sizes may be used if agreed upon between the parties to the test. All of the selected devices shall have undergone appropriate elevated temperature reliability screens, e.g. burn-in and high temperature storage life and shall be packaged in the package type that will be used for the system application. If more than one package type is used then parts in each package type must be characterized. Divide the samples into four groups of 5 each and use the remaining part for a control. Perform pre-irradiation electrical characterization on all parts ensuring that they meet the pre-irradiation electrical tests. Irradiate 5 samples with all leads grounded and another 5 under the worst case irradiation bias condition (as determined by characterization testing, or specified in a procurement document or at maximum supply voltage) at 50-300 rd(SiO<sub>2</sub>)/s and room temperature. Irradiate 5 samples with all leads grounded and another 5 under worst case bias (same as at high dose rate) at ≤10 mrad/s and room temperature. Irradiate all samples to the same dose levels, including 0.5 and 1.0 times the anticipated specification dose, and repeat the electrical characterization on each part at each dose level. Calculate the radiation induced change in each electrical parameter ( $\Delta$ para) for each sample at each radiation level. Calculate the ratio of the median  $\Delta$ para at low dose rate to the median  $\Delta$ para at high

dose rate for each irradiation bias group at each total dose level. If this ratio exceeds 1.5 for any of the most sensitive parameters then the part is considered to be low dose rate sensitive. This criterion does not apply to parameters which exhibit changes that are within experimental error or whose values are below the pre-irradiation electrical specification limits at low dose rate at the specification dose.

Note 9—There are risks involved in using smaller numbers of test parts. These result from part-to-part variability within a given test lot.

Note 10—Low dose rate sensitivity often has been observed to show a large variability in response with a change in date code.

8.1.2.3 Characterization Testing of Category A Parts—The characterization of Category A bipolar parts shall follow the same procedures as prescribed for MOS parts (see 8.1.1.1 – 8.1.1.7). The dose rate for these tests shall be the standard dose rate of 50 to 300 rd(SiO<sub>2</sub>)/s (see 8.1.1.1 (b) (1) or MIL-STD-883, Test Method 1019) unless otherwise required by the test plan. The primary purpose of this test is to establish the worst case irradiation bias conditions for the total dose testing if they are not specified in the procurement document or test plan. If a part has not been demonstrated to be Category A by previous characterization testing or analysis, then it must be treated as a Category B part until it has been demonstrated by the tests in 8.1.2.4 to be Category A.

8.1.2.4 Characterization Testing of Unknown Category or Category B Parts:

- (a) One of the main objectives of the Category B characterization testing is to determine the dose rate response of the parts down to dose rates of interest for the intended use. Fortunately, most low-dose-rate sensitive parts show a saturation of the enhanced response at dose rates below a value determined by the most sensitive transistor type for the parameter of interest. For some part types, this may be  $\sim 1$  rd(SiO<sub>2</sub>)/s, and for others it may be  $\sim 1-10$  mrd(SiO<sub>2</sub>)/s.

- (b) The characterization testing should be performed over a range of dose rates starting at  $\sim 100~\rm rd(SiO_2)/s$  and going to dose rates sufficiently low to observe saturation of the enhanced response. An exception to this rule is that the testing need not be carried down to dose rates below that specified for the intended use of the device-under-test if this is agreed to by the parties to the test. If no saturation is observed at practically attainable dose rates, engineering judgment is required, for example, via use of overstress and extrapolation techniques, to estimate saturated values. All critical electrical parameters shall be measured at each dose rate and total dose level and the total dose should be taken to at least the part specification level.

- (c) Once the dose rate response has been determined, the category of the part can be established. If the worst case low dose rate enhancement factor for any critical parameter at any dose and dose rate is greater than 1.5, then the part should be considered Category B. Otherwise it is Category A. The change in the parameter must be significant and well above the noise floor. For example if all post-irradiation parameters are still well below the pre-irradiation specification levels for all doses and dose rates then the part would be considered a Category A part.

- 8.1.2.5 Characterization Testing of Category B Parts to Establish Test Conditions for Accelerated Testing:

- (a) The default test for Category B parts is a low dose rate test at  $\leq 10 \text{ mrd}(\text{SiO}_2)/\text{s}$ . This test may require a very long irradiation time depending on the required dose levels for the test. It is often very desirable to decrease the time for the test using an accelerated test method. The purpose of the characterization testing is to establish the appropriate test conditions and procedures for the accelerated test and demonstrate that the accelerated test will bound the response at low dose rate. The response of the part at low dose rate, as determined in 8.1.2.4, must be established and used as a baseline for comparison to demonstrate that the accelerated test will provide at least as much degradation as the low dose rate test. Examples of possible accelerated tests to bound the low dose rate response are given in Appendix X2. These tests include but are not limited to the following: (a) low dose rate tests at dose rates above 10 mrd(SiO<sub>2</sub>)/s, (b) irradiation at elevated temperature at dose rates on the order of 0.5 to 5 rd(SiO<sub>2</sub>)/s, (c) switched dose rates tests using multiple sample sets first exposed at high dose rate (to increasing dose levels) and then switched to low dose rate, and (d) exposure at high dose rate in the presence of molecular hydrogen.

- (b) When implementing any of the above, or other, accelerated tests, detailed test conditions (irradiation bias, irradiation temperature, dose rate(s), anneal times and temperatures, etc.) and test procedures must be established, as well as any overtest factors or parameter delta design margins, to demonstrate that the accelerated test will bound the low dose rate response for all critical parameters. The characterization testing should be performed on a statistically significant sample from a minimum of three wafer lots fabricated over a period of at least 6 months to a year. These test conditions may then be used for an accelerated test for hardness assurance acceptance testing.

- (c) If the devices are to be irradiated at an elevated temperature, follow the procedures in 8.1.1.2 through 8.1.1.5 as well as the next statement. After electrical characterization and before each irradiation begins, the test devices shall be heated rapidly to the prescribed temperature and stabilized for no more than 3 min before irradiation. See Section 7 for a description of the environmental irradiation chamber. At the end of each irradiation, the temperature shall be reduced rapidly to room temperature and stabilized for at least three minutes before electrical characterization.

- 8.2 Hardness Assurance Acceptance Testing—Hardness assurance testing is performed for qualification or lot/process quality conformance, often for a specific system application. Hardness assurance testing will be performed using a prescribed method of test sample selection and a single set of test conditions, such as irradiation bias, dose rate, and total dose levels. The specific set of test conditions often are determined to be the nominal worst case based on characterization tests.

- 8.2.1 Low Dose Requirements—Hardness testing of MOS and bipolar microelectronic devices is not necessary when the required hardness is 100 rd(SiO<sub>2</sub>) or lower.

- 8.2.2 MOS Devices and Integrated Circuits with Intended Use at Dose Rates At or Below 300  $rd(SiO_2)/s$ :

- 8.2.2.1 Parties to the test must first establish the conditions of the test. These conditions should be stated in a detailed specification or other procurement document. As a minimum,

the following conditions should be specified: test approach, test type, irradiation source, total dose levels, dose rate, irradiation bias, irradiation temperature, anneal bias, anneal temperature, and anneal times. The recommended default irradiation conditions are step stress, remote characterization,  $^{60}\text{Co}$ , four dose levels (0.1X, 0.2X, 0.5X, and 1.0X, where X is the system specification), 50 to 300 rd(SiO<sub>2</sub>)/s, static dc bias, and 24  $\pm$  6°C. All possible interferences of Section 6 must be considered. The two-part test given below is based on that of MIL-STD-883, Test Method 1019; however, the procedure given here does depart from Test Method 1019 where that document is considered to be too conservative.

- 8.2.2.2 *Test 1*—for failures related to oxide trapped charge.

- (a) Prepare bias fixtures, test fixtures, test circuits (or test equipment), and test programs.

- (b) Follow 8.1.1.3 8.1.1.5 as described above with the following exceptions. The time between the end of irradiation and the end of the electrical tests shall not exceed 1 h, and the time between irradiations shall not exceed 2 h. If the electrical testing is being performed at a remote site and the 1 and 2 h requirements cannot be met, the times between irradiation and test and the time between irradiations may be extended by cooling the parts to  $\leq$ 60°C using dry ice as described in MIL-STD-883, Test Method 1019. Using this option the time between irradiation and electrical test may not exceed 72 h and the time between irradiations may not exceed 120 h.

Note 11—There are significant categories of semiconductor devices that show less ionizing dose damage at low dose rates than at 300 rd(SiO<sub>2</sub>)/s. These are devices wherein the damage mechanism is dominated by build-up of holes in the oxide layer, and that are only slightly affected by the build-up of interface states. For low dose rates typical of space applications, the effect can be very significant. Devices, which fail at a dose level,  $D_f$ , at 300 rd(SiO<sub>2</sub>)/s may survive at dose levels from  $2D_f$  to  $5D_f$  when tested at low dose rates, for example, 0.01 rd(SiO<sub>2</sub>)/s. In some cases, characterization of these devices can permit the use of key components, which would be rejected considering only the test data taken at 300 rd(SiO<sub>2</sub>)/s. In many other cases, it can reduce the amount of either local shielding or box shielding required to insure survivability. The methods described in 8.2.2.2 (c) may provide a cost effective method to make allowance for these effects.

- (c) If the intended use dose rate is below  $0.1~{\rm rd(SiO_2)/s}$  and the parts fail at a higher dose rate, then one may perform a post irradiation room temperature anneal for a time not to exceed the specification dose divided by the maximum intended use dose rate. The anneal bias shall be the same as the irradiation bias. At the end of the anneal period remeasure the electrical characteristics and use these data to determine acceptance/ rejection.

- (d) If the dose rate for the test is significantly below the standard dose rate of 50 to 300  $\mathrm{rd}(\mathrm{SiO}_2)$ /s and the electrical testing is being performed at a remote site, the time between irradiation and test may be equal to 10 % of the incremental irradiation time or 1 h, whichever is greater. In addition, the time between irradiations may be 20 % of the incremental irradiation time or 2 h, whichever is greater.

- 8.2.2.3 *Test* 2—For failures related to interface traps.

- (a) An accelerated annealing (rebound) test shall be performed for failures related to interface traps, unless Test 1 is performed at the intended use dose rate or below or the conditions of 8.2.2.3 (f) apply.

- (b) Prepare bias fixtures, test fixtures, test circuits (or test equipment), and test programs.

- (c) Follow 8.1.1.3 8.1.1.5 as just described with the following exceptions. The parts shall be given an additional irradiation to raise their total dose level to 1.5 times the specification level. The time between the end of irradiation and the end of the electrical tests shall not exceed 1 h. If the electrical testing is being performed at a remote site and the 1-h requirement cannot be met, the time between irradiation and test may be extended by cooling the parts to  $\leq$ 60°C using dry ice as described in MIL-STD-883, Test Method 1019. Using this option, the time between irradiation and electrical test may not exceed 72 h. The samples used for this test may be the same samples used for the original test.

- (d) Following irradiation the parts shall be subjected to an accelerated anneal. Within 1 h following post irradiation electrical characterization, place the parts in an environmental chamber under the same bias used for irradiation and heat the parts to  $100 \pm 5^{\circ}$ C for  $168 \pm 12$  h, or for the temperature and time required by the specification. Reduce the temperature rapidly to room temperature and within 1 h following the anneal, perform the required electrical characterization to determine acceptance/rejection.

- (e) As an alternative to  $100 \pm 5^{\circ}\mathrm{C}$  for  $168 \pm 12$  h, the temperature and time may be determined by either characterization of the actual part type, or by characterization of nMOS transistors representative of the parts under test. If transistors are used the alternate temperature and time must demonstrate > 60% trapped charge annealing and < 10% interface trap annealing.

- (f) The accelerated annealing test may be eliminated for certain part types or processes, or both, if it can be shown by characterization testing that rebound failures are not a problem for the irradiation conditions of interest. Also, it is permissible to omit the 50 % overtest requirement if characterization testing can demonstrate that the safety factor is not necessary. See Appendix X1 for a discussion of the conditions for eliminating the rebound test or the overtest requirement.

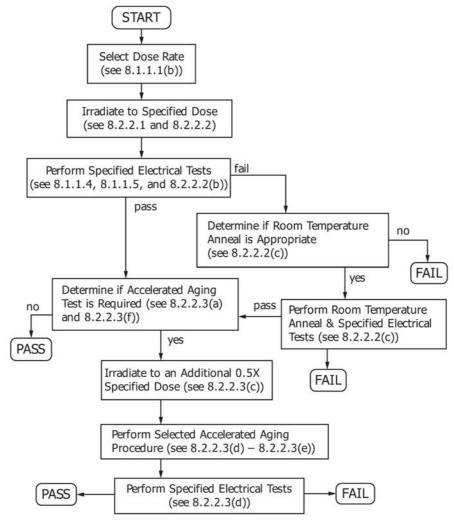

- 8.2.2.4 A chart summarizing the test decision flow specified in 8.2.2 through 8.2.2.3 (*f*) is given in Fig. 1.

- 8.2.3 Bipolar Devices and Integrated Circuits with Intended Use at Dose Rates at or Below 300 rd(SiO<sub>2</sub>)/s:

- 8.2.3.1 The bipolar devices and circuits are divided into two categories, Category A Parts, which exhibit no dose rate sensitivity, and Category B Parts, which show enhanced degradation at lower dose rates, as described in 8.1.2.2.

- 8.2.3.2 Category A Parts—Category A Parts include all parts that have passed the screen described in 8.1.2.2 and have been determined to be dose rate insensitive by characterization testing as described in 8.1.2.4 or analysis. The screen test alone is not sufficient to classify a part as Category A. For these parts a standard room temperature test (see 8.1.1.1 8.1.1.5 or MIL-STD-883, Test Method 1019) is sufficient for lower dose rate applications. The dose rate for these tests shall be the standard dose rate of 50–300 rd(SiO<sub>2</sub>)/s (see 8.1.1.1 (b) (I) or MIL-STD-883, Test Method 1019) unless otherwise required by the test plan.

FIG. 1 Flow Chart for Ionizing Radiation Testing of MOS Devices (see 8.2.2 through 8.2.2.3 (f))

- (a) Prepare bias fixtures, test fixtures, test circuits (or test equipment), and test programs.

- (b) Follow 8.1.1.3 8.1.1.5 with the following exceptions. The time between the end of irradiation and the end of the electrical tests shall not exceed 1 h, and the time between irradiations shall not exceed 2 h. If the electrical testing is being performed at a remote site and the 1 and 2 h requirements cannot be met, the times between irradiation and test and the time between irradiations may be extended by cooling the parts to  $\leq$ 60°C using dry ice as described in MIL-STD-883, Test Method 1019. Using this option the time between irradiation and electrical test may not exceed 72 h and the time between irradiations may not exceed 120 h.

- 8.2.3.3 *Category B Parts*—For parts, which are low dose rate sensitive, there are three options.

- (a) Option 1—Test the parts at the average intended use dose rate or at a dose rate agreed to by the parties of the test if the irradiation time at the specification dose is reasonable (see Appendix X2 for discussion). This option may be practical for many applications where the dose rate is no lower than 0.01 to 0.1 rd(SiO<sub>2</sub>)/s. Follow 8.1.1.3 8.1.1.5 using the specific test conditions required by the test plan and the following excep-

- tion. The time between the end of irradiation and the end of the electrical tests shall not exceed 1 h or 10 % of the incremental irradiation time and the time between irradiations shall not exceed 2 h or 20 % of the incremental irradiation time. For remote electrical testing, if these times are not long enough then the parts may be cooled to  $\leq 60^{\circ}$ C using dry ice as described in MIL-STD-883, Test Method 1019. Using the dry ice option the time between irradiation and electrical test may not exceed 72 h and the time between irradiations may not exceed 120 h.

- (b) Option 2—Test the parts at  $24 \pm 5^{\circ}$ C at a low dose rate of  $10 \pm 1$  mrd(SiO2)/s to 1.5 times the specification dose. Device parametric values shall be compared to the specification requirement for the parameter to determine pass or fail for the lot.

- (c) Option 3—For some parts, irradiation at the dose and dose rate of the intended use or the dose rate of Option 2 is impractical because the resulting testing times are excessive. For such cases, an accelerated test method may be possible.

- (1) An appropriate set of accelerated test conditions, if available, must be determined using characterization testing described in 8.1.2.5. Potential methods for achieving an

accelerated test include (a) irradiation at a low dose rate somewhat higher than the baseline dose rate of  $10 \pm 1 \, \mathrm{mrd}(\mathrm{SiO}_2)/\mathrm{s}$ , (b) a high-dose-rate irradiation (50 to 300  $\mathrm{rd}(\mathrm{SiO}_2)/\mathrm{s}$ ) at an elevated temperature, (c) a moderately low-dose-rate irradiation (0.5 to 5  $\mathrm{rd}(\mathrm{SiO}_2)/\mathrm{s}$ ) at an elevated temperature, (d) use of switched dose rate testing, (e) use of irradiation at high dose rate in the presence of molecular hydrogen, and (f) use of a two-step high dose rate irradiation with elevated temperature anneals after each irradiation. See Appendix X2 for discussion of these and other strategies for obtaining an accelerated test.

- (2) The test plan for the determination of an appropriate accelerated test should receive careful attention in order to minimize cost and time.

- (3) For such a test a well-documented test procedure will be required. Follow 8.1.1.3 8.1.1.6 and 8.1.2.5 using the specific test conditions required by the test plan. The time between the end of irradiation and the end of the electrical tests shall not exceed 1 h or 10 % of the incremental irradiation time and the time between irradiations shall not exceed 2 h or 20 % of the incremental irradiation time. For remote electrical testing, if these times are not long enough then the parts may be cooled to  $\leq 60^{\circ}$ C using dry ice as described in MIL-STD-883, Test Method 1019. Using the dry ice option the time between irradiation and electrical test may not exceed 72 h and the time between irradiations may not exceed 120 h.

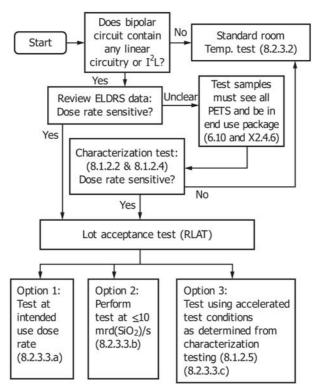

- 8.2.3.4 A chart summarizing the test decision flow specified in 8.2.3.2 through 8.2.3.3 (*d*) is given in Fig. 2.

#### 9. Report

9.1 Report the following information:

- 9.1.1 *Identity of the Part(s) Tested*—All information available for part identification should be included, for example, part type, serial number, manufacturer, lot date code, diffusion lot designation, wafer lot designation, package type, etc.

- 9.1.2 The test plan containing a listing of items agreed upon by parties to the test including all conditions of 4.1.2.2, for example, nature and spectrum of the radiation source and spectrum of radiation impinging on parts, dose rates, time sequences, and dosimetry techniques and measurements.

- 9.1.3 A schematic for the bias and parameter measurement circuits.

- 9.1.4 A diagram of the physical test configuration with distance and materials.

- 9.1.5 A tabulation of test parameter measurement data including electrical noise and current leakage of the electrical measurement system for in-flux testing, the test date, the radiation source used, the bias conditions during irradiation and transport, the ambient temperature around the device during irradiation and testing, the duration of each irradiation, the time between irradiation and electrical testing, the duration of the electrical measurements, the time to the next irradiation, the electrical test conditions and the radiation test (dose) levels;

- 9.1.6 Any anomalous incidents during the test.

- 9.1.7 A description of the accelerated annealing procedure, if used.

- 9.1.8 For bipolar devices, whether Category A or Category B, test conditions used if Category B, and how those test conditions were established.

- 9.1.9 For procurement testing the pre- and post-irradiation data shall be recorded for each part and retained with the parent population data.

FIG. 2 Flow Chart for Lot Acceptance Testing for Bipolar Devices (see 8.2.3 through 8.2.3.3 (c) (d))

## 10. Keywords

10.1 ASIC (application specific integrated circuit); bipolar; cobalt 60 testing; ELDRS (enhanced low dose rate sensitivity);